半加器和全加器是數字電路中的基本組件,用于執行二進制數的加法運算。它們在計算機、微處理器和其他數字系統中扮演著重要角色。

半加器的功能特點

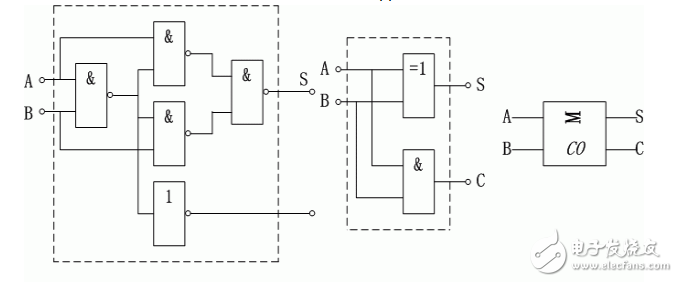

半加器是一種簡單的數字電路,它能夠實現兩個一位二進制數的加法運算。半加器的設計目的是計算兩個輸入位的和,但不包括進位。半加器有兩個輸入端(A和B)和一個輸出端(和S),以及一個進位輸出端(C)。

功能特點

- 基本功能 :半加器只能處理兩個一位二進制數的加法,輸出結果為和(Sum)和進位(Carry)。

- 輸入輸出 :半加器有兩個輸入(A和B),一個輸出(S),以及一個進位輸出(C)。

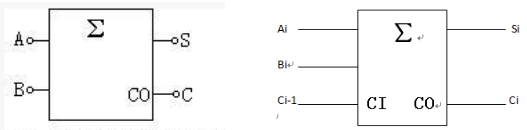

- 真值表 :半加器的真值表如下所示:

| A | B | S | C |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

- 邏輯表達式 :半加器的邏輯表達式可以表示為:

- S = A XOR B

- C = A AND B

- 電路實現 :半加器通常使用異或門(XOR)和與門(AND)來實現。

- 應用場景 :半加器常用于更復雜的加法器設計中,作為構建塊之一。

- 限制 :由于半加器不處理來自前一位的進位,因此它不能單獨用于多位數的加法運算。

全加器的功能特點

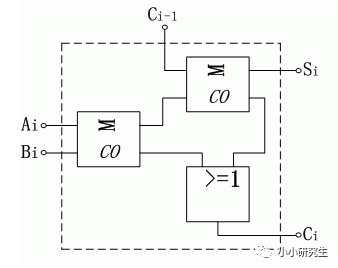

全加器是一種更復雜的數字電路,它能夠處理三個一位二進制數的加法運算,包括兩個加數位和一個進位輸入。全加器的設計目的是計算三個輸入位的和,同時考慮來自前一位的進位。

功能特點

- 基本功能 :全加器能夠處理三個一位二進制數的加法,包括兩個加數位和一個進位輸入,輸出結果為和(Sum)和進位(Carry)。

- 輸入輸出 :全加器有三個輸入(A、B和一個進位輸入Cin),兩個輸出(和S和一個進位輸出Cout)。

- 真值表 :全加器的真值表如下所示:

| A | B | Cin | S | Cout |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

- 邏輯表達式 :全加器的邏輯表達式可以表示為:

- S = (A XOR B) XOR Cin

- Cout = (A AND B) OR (B AND Cin) OR (A AND Cin)

- 電路實現 :全加器通常使用異或門(XOR)、與門(AND)和或門(OR)來實現。

- 應用場景 :全加器是構建多位數加法器的關鍵組件,可以單獨使用或與其他全加器級聯,以實現多位數的加法運算。

- 優勢 :與半加器相比,全加器能夠處理來自前一位的進位,使其適用于多位數的加法運算。

總結

半加器和全加器是數字電路中實現二進制加法的基本組件。半加器簡單,只能處理兩個一位二進制數的加法,而不包括進位。全加器則更為復雜,能夠處理三個一位二進制數的加法,包括兩個加數位和一個進位輸入。全加器的設計使其能夠處理來自前一位的進位,因此更適合用于多位數的加法運算。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

全加器

+關注

關注

10文章

62瀏覽量

28505 -

數字電路

+關注

關注

193文章

1605瀏覽量

80618 -

數字系統

+關注

關注

0文章

143瀏覽量

20851 -

半加器

+關注

關注

1文章

29瀏覽量

8793

發布評論請先 登錄

相關推薦

FPGA入門——1位全加器設計 精選資料分享

FPGA入門——1位全加器設計一、原理圖輸入1.1 創建工程1.2 原理圖輸入1.3 將設計項目設置成可調用的元件1.4 半加器仿真1.5 設計全加

發表于 07-26 07:01

半加器和全加器的區別是什么

半加器(Half Adder)和全加器(Full Adder)是數字電路中的基本組件,用于執行二進制加法運算。它們的主要區別在于功能和輸入輸

半加器和全加器的功能特點

半加器和全加器的功能特點

評論