文章來源:慧智微電子

原文作者:彭

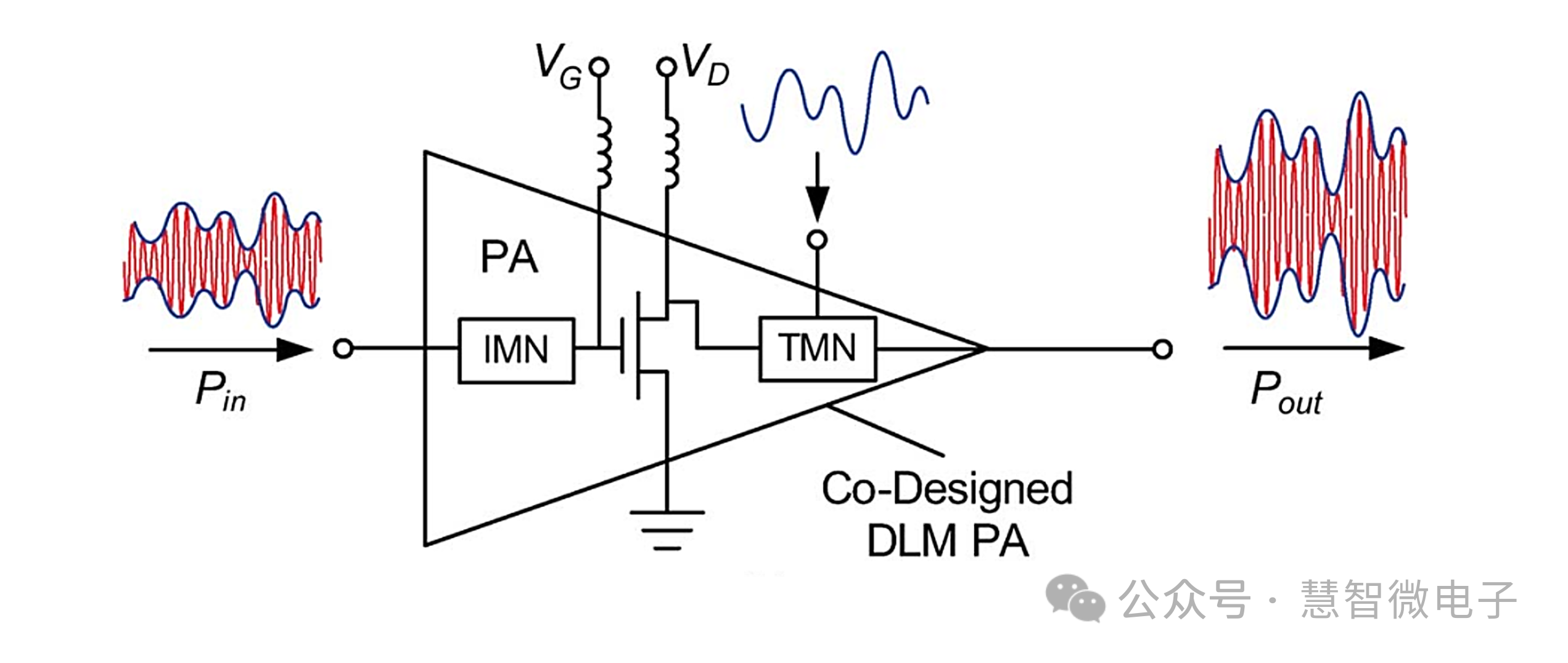

“效率”在射頻功率放大器(PA)設計中占據舉足輕重的地位。高效率PA設計的兩大核心:PA的“Class”設計以及功率合成架構。然而,在實際的射頻前端系統中,PA并非孤立存在,而是與整個系統緊密相連。系統層面的設計方案對PA功耗有著深遠影響。

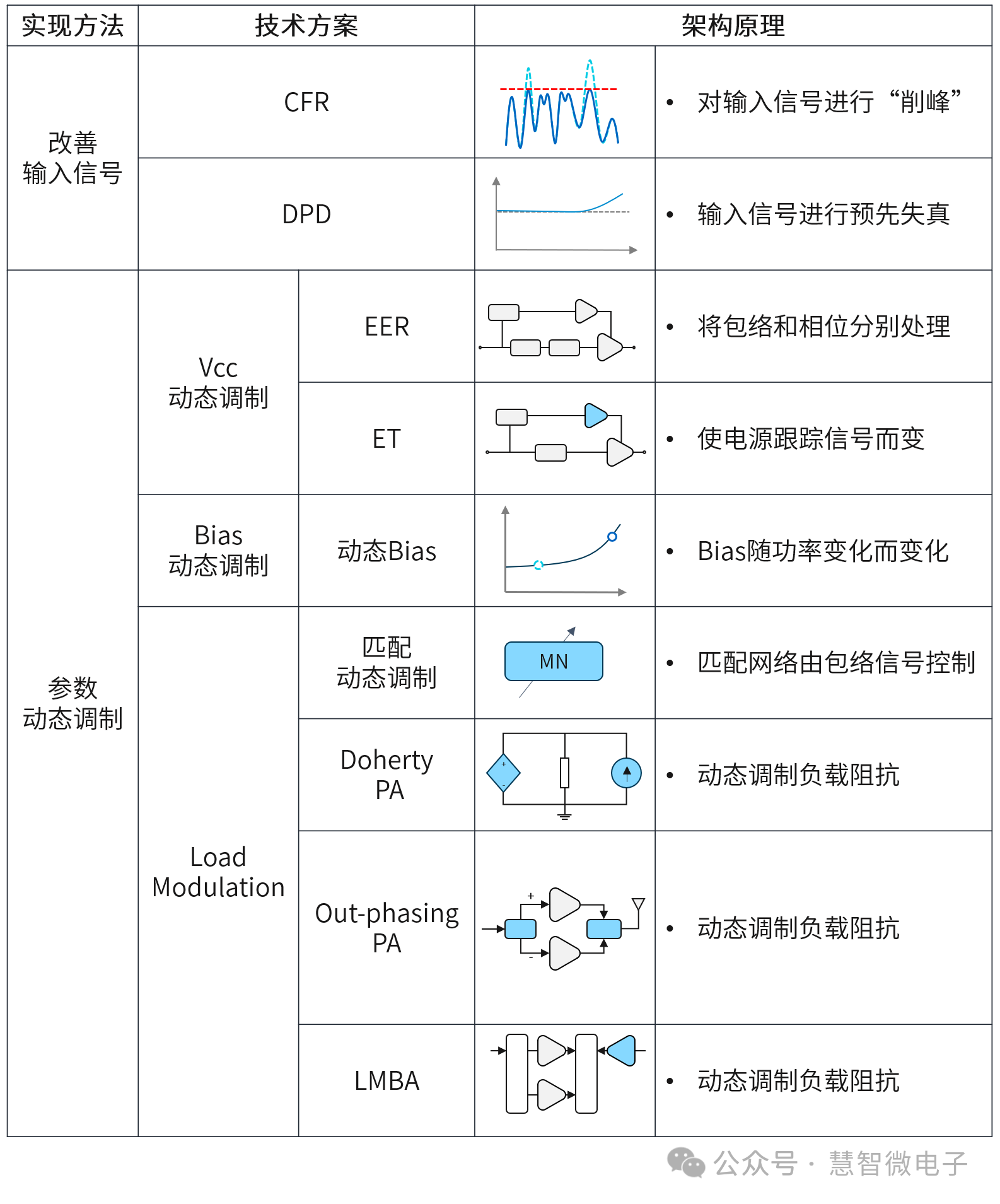

當單體PA的效率提升至一定極限后,PA廠商、平臺廠商以及終端系統廠商開始將研究焦點轉向包含PA在內的系統級設計。試圖通過更高層次的系統解決方案,進一步突破PA的性能瓶頸。在這一領域,既有大家耳熟能詳的包絡跟蹤(ET)和數字預失真(DPD)技術,也有相對陌生的負載調制(Load Modulation)和波峰因子減少(CFR)等技術。

這些技術究竟是如何神奇地提升PA效率的?未來又有哪些新技術可能應用于PA效率的提升?本文將試著從系統級的角度,理解高效率PA系統設計的奧秘。

PA設計的雙重挑戰

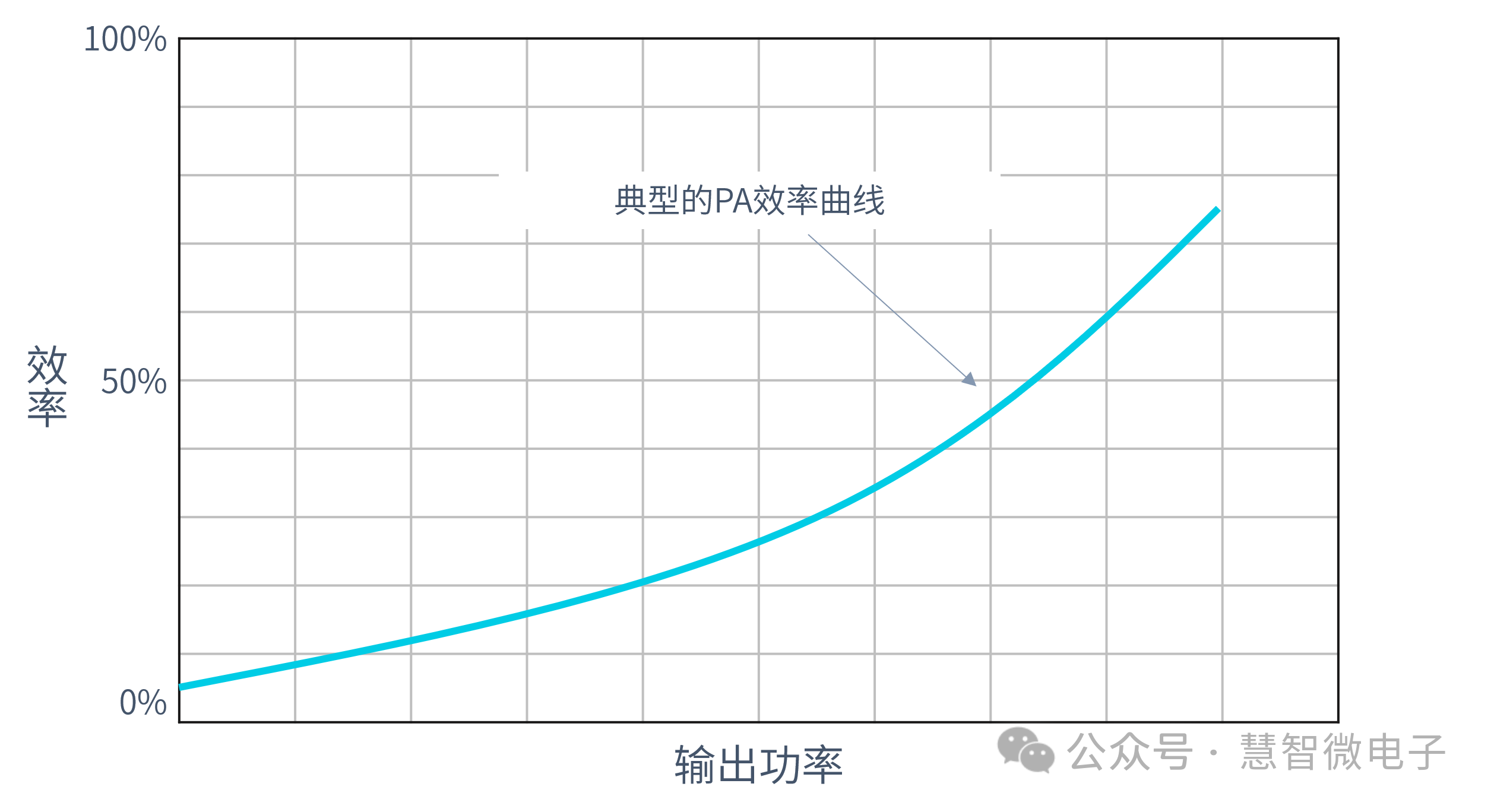

在PA的單體設計中,效率和設計所選的“Class”、拓撲架構乃至匹配網絡的損耗等諸多因素緊密相連。然而,從系統層面來看,各種PA的效率曲線都可大致描繪為一根隨功率提升而上升的曲線。簡而言之,隨著功率的增加,射頻擺幅擴大,越來越多的能量被轉化為射頻信號,因此在高功率狀態下,PA將直流電轉換為射頻信號的效率達到最高。

圖:典型的PA效率曲線

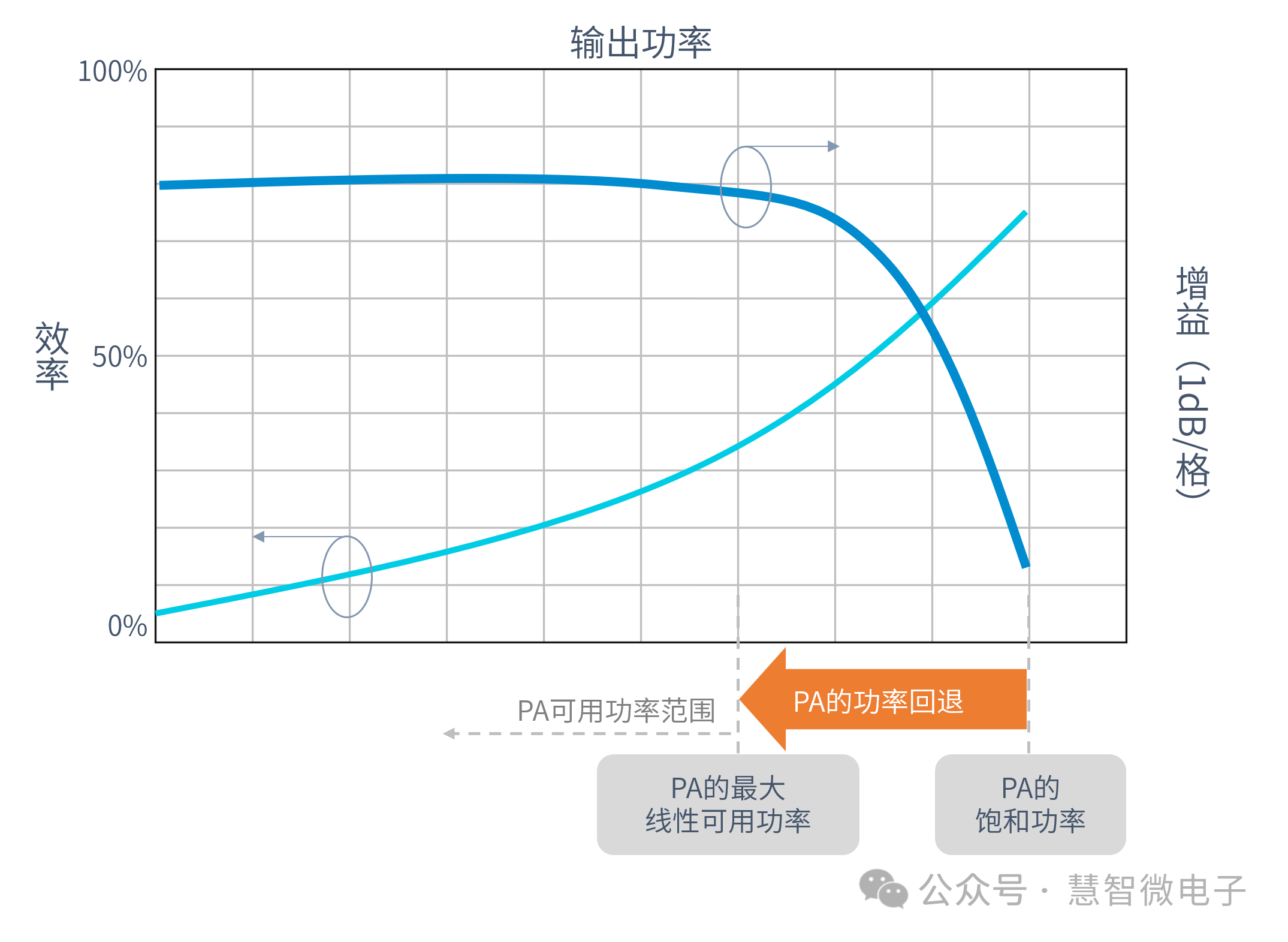

盡管不同PA的峰值效率點和功率回退時的斜率存在差異,但效率隨功率變化的大致趨勢是固定的。基于這一效率曲線,我們可以得出一個PA高效率應用的基本原則:盡量讓PA工作在接近高功率的狀態。

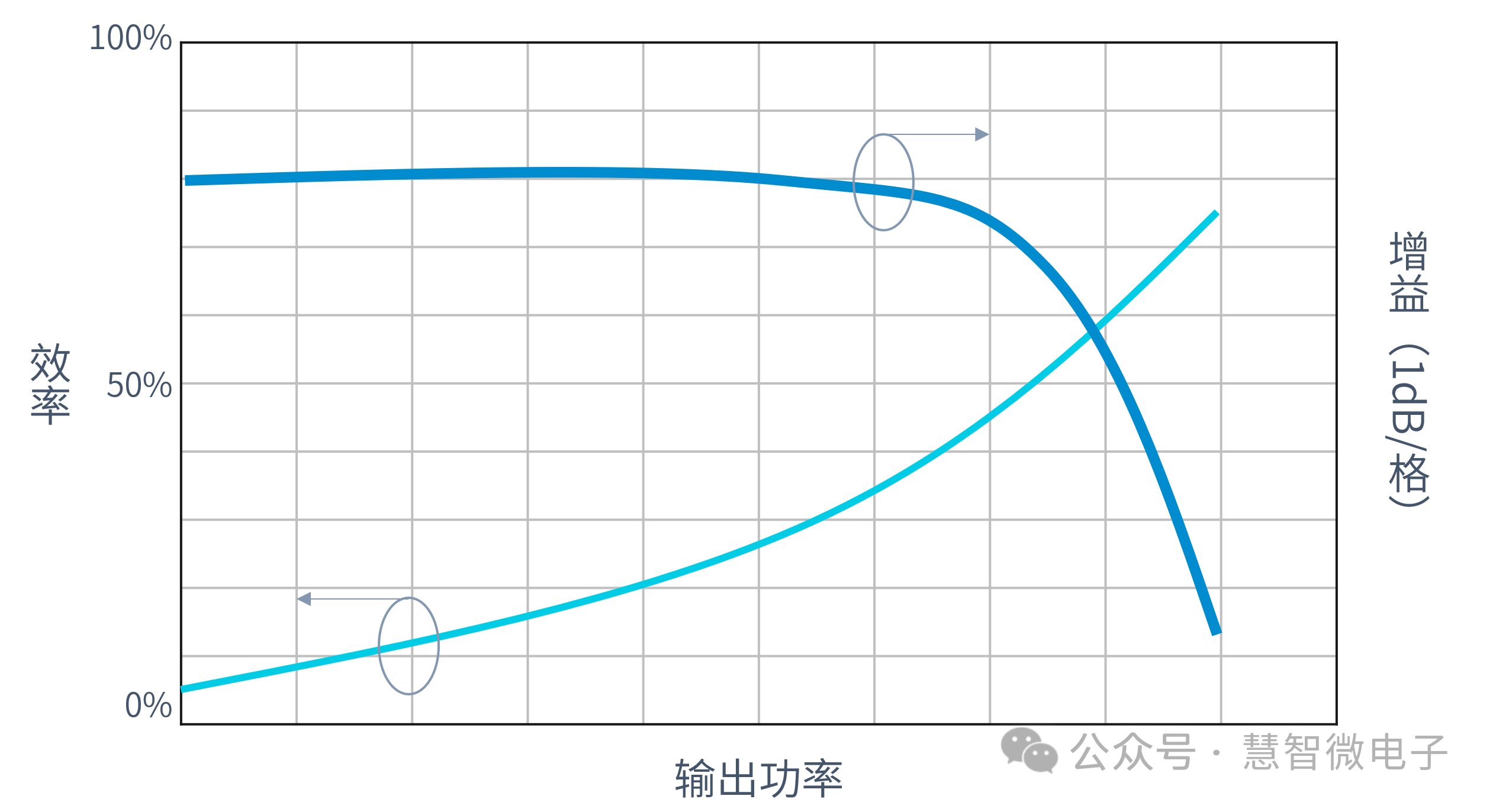

然而,這種高效率狀態并非沒有代價。當PA越接近高功率飽和區,其線性度就會逐漸惡化。典型的增益隨輸出功率變化曲線顯示,在飽和區,PA增益可能會出現幾dB甚至十幾dB的壓縮,對于線性信號而言,這幾乎使得PA處于不可用狀態。

圖:典型的PA效率與增益曲線

這一困境該如何應對?這就需要引入“功率回退”(Power-back off)的理念。所謂功率回退,即為了保持輸出信號的線性度,在使用時將功率從飽和點適度降低。這意味著為了保證線性度,我們必須犧牲一部分功率輸出,也就犧牲了一部分的效率。

?圖:PA的功率回退使用?

在PA的應用中,效率和線性度始終是一對需要權衡的因素。這種權衡體現在多個方面:

在調整輸出功率時,效率隨功率增加而提升,但線性度卻隨之下降;

在進行負載匹配時,PA的最佳效率點和最佳線性度點往往并不重合;

在選擇供電電壓時,更高的電壓雖然有利于改善線性度,但也會降低效率。

因此,在PA設計中,如何平衡效率和線性度成為了一個永恒的挑戰。

改善輸入信號

使PA在更高效率區域運行

在PA設計中,會致力于擴展PA的工作區域,以獲得更出色的效率表現。例如,設計時會盡量推遲P1dB點的出現,使PA增益的壓縮盡量延遲,從而讓PA的工作點更接近飽和點,以減少效率損失。

同樣,在不需要極高功率的設計中,也可以通過降低飽和功率的設計,也能使PA工作點更加接近飽和功率處的高效區域。

在系統設計層面,也可以采用類似的理念來提升效率。這里,CFR和DPD兩項關鍵技術發揮著重要作用。

CFR:降低信號的峰均比

CFR(Crest Factor

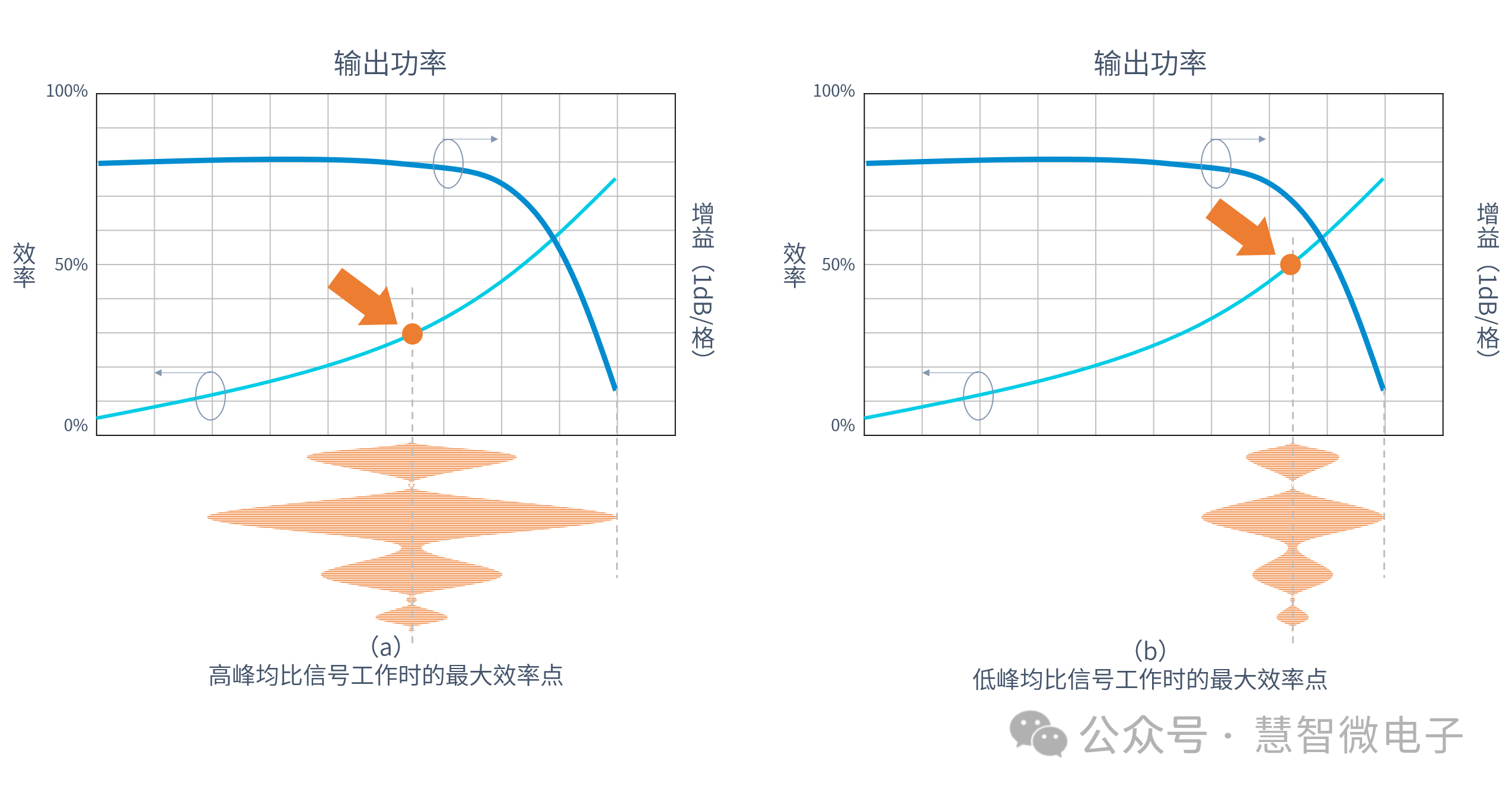

Reduction),即波峰因數降低技術,實質上是一種信號“削峰”技術。在現代通信系統中,傳輸的信號通常是幅度和相位均帶有信息的編碼信號,這導致信號存在較大的峰均比(PAPR)。峰均比越大,意味著信號中的峰值與均值之間的偏差越大。

為了保證信號不失真,必須確保信號的最高功率點不超過PA的飽和區。因此,均值功率的工作點需要比飽和功率低至少一個峰均比。所以,信號的峰均比越大,需要回退的功率就越多,從而降低PA的效率。

圖:高低兩種峰均比信號對PA使用影響對比

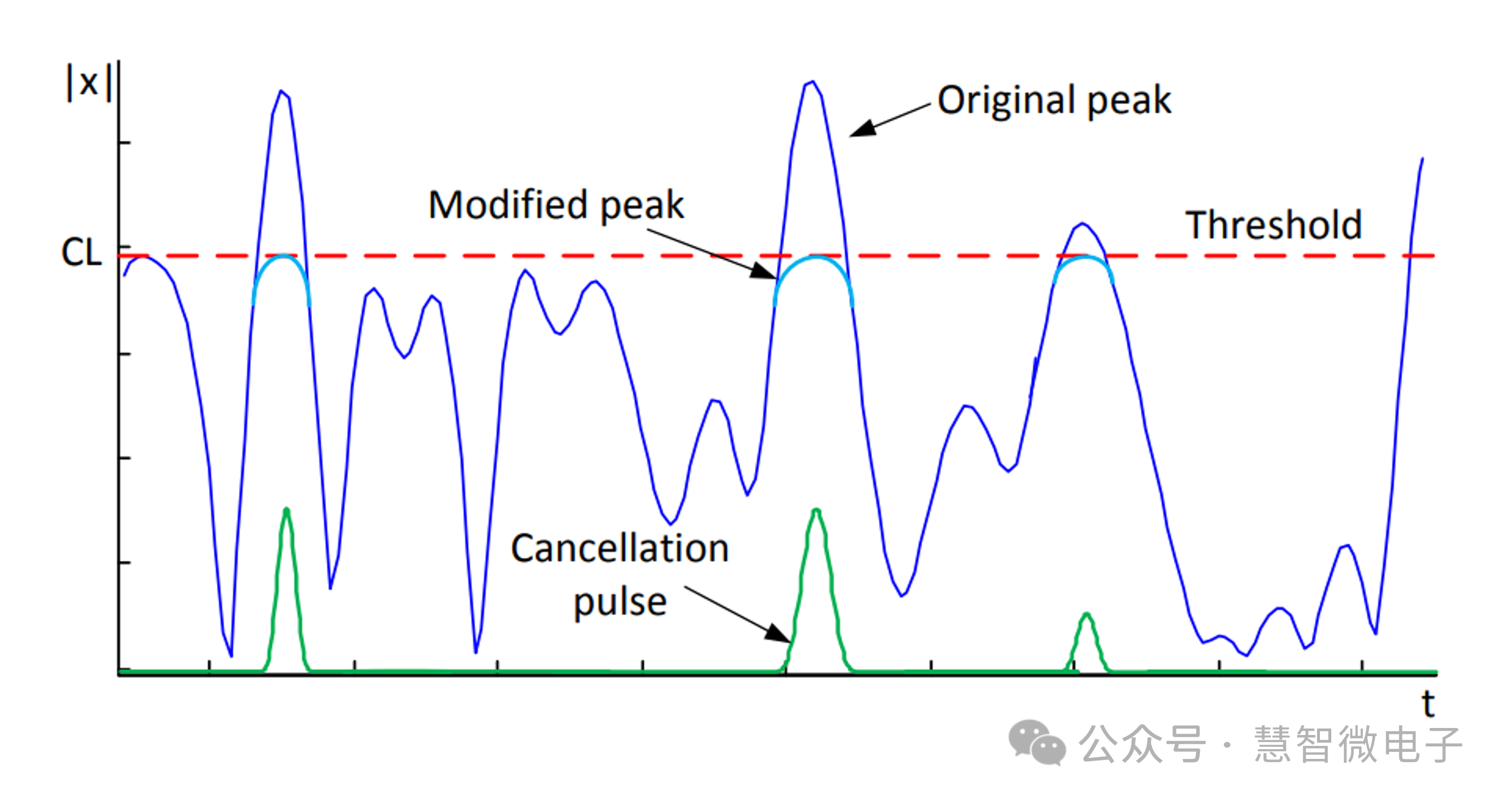

CFR技術通過算法處理原始信號,盡量減少高峰均值信號的出現,或通過限幅、削峰等方法對輸入信號進行限制。這樣,進入PA的信號就不會有過高的峰值,使PA能夠在更高的功率范圍內工作,從而提升效率。下圖為經過CFR修改后的信號與原始信號對比圖[1]。

圖:CFR技術對信號峰值的降低

由于OFDM信號的特性,4G/5G信號在時域中具有顯著的峰均比,這使得CFR技術顯得尤為重要。系統CFR能力的強弱直接影響到整個系統的性能表現。因此,在基站和手機終端等平臺中,CFR技術已經得到了廣泛的推廣和應用。

DPD:校準PA失真

盡管CFR能夠整形信號并降低峰均比,但信號的峰均比始終存在。當PA的功率向上提升時,必然會遇到線性度惡化的問題。此時,DPD技術便發揮作用。

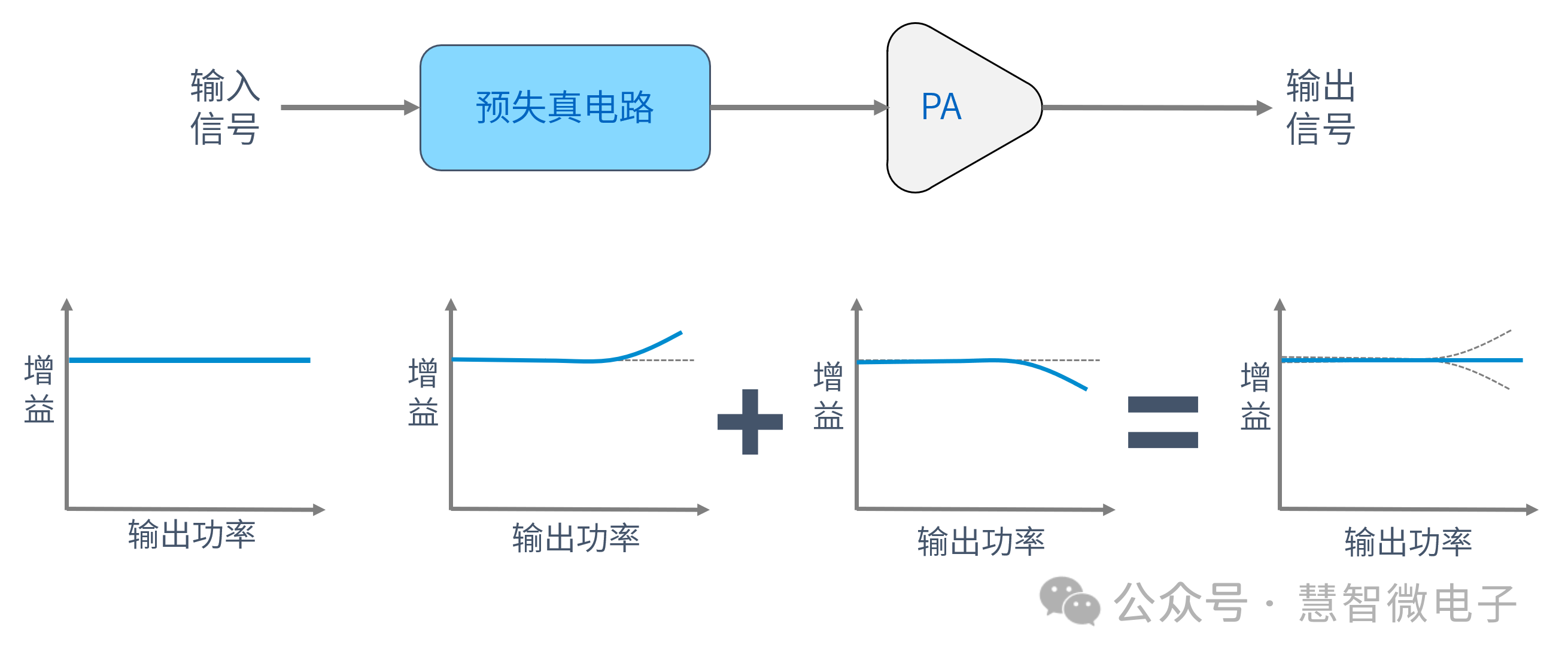

DPD(Digital

Pre-distortion),即數字預失真技術,其核心理念是讓輸入信號提前產生一個與PA相反的失真,以抵消PA引入的失真,工作原理如下圖所示。

圖:DPD的原理

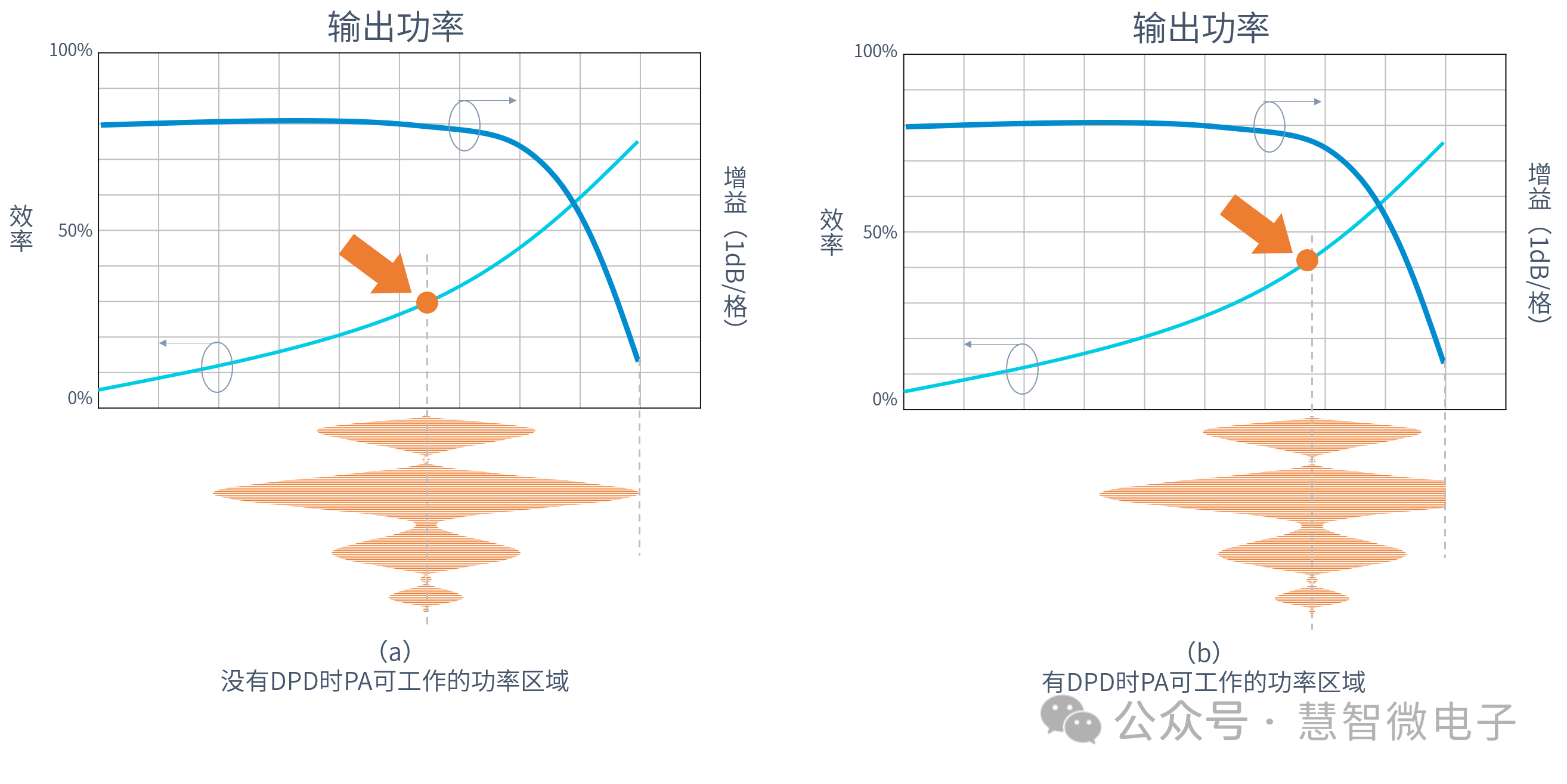

在DPD的幫助下,PA的線性度得到提升。系統也就能容忍更多的PA線性度惡化,從而使其能夠在更高的功率范圍內工作,進而提高效率。有DPD和沒有DPD時,PA可工作的功率區域如下圖所示。

圖:DPD下,PA工作的功率區域可以提升

DPD操作完全在數字域進行,無需對PA進行特殊調整即可看到效果。然而,DPD并非萬能,它也有自身的局限性。DPD的效果強烈依賴于算法,而移動終端由于功耗和算力的限制,無法支持過于復雜的DPD算法。此外,PA的特性會隨溫度、負載、偏壓和批次等因素的變化而變化,為了獲得良好的校正效果,DPD需要不斷調整以適應這些變化。同時,DPD需要與PA進行聯合調試和特定開發,以充分發揮二者的潛力。

盡管有所限制,DPD仍在蜂窩和Wi-Fi等應用中得到了廣泛應用。最近Wi-Fi應用中較為熱門的“非線性PA”,就是利用DPD技術和非線性PA技術結合實現的高效率PA技術。

無論是CFR還是DPD,它們都旨在通過算法降低系統對PA線性度的要求,從而提升PA的工作功率和效率。這些技術對平臺的算法能力提出了更高的要求。

除了CFR和DPD之外,系統中還采用了另一種方法來提升PA在回退功率點的效率,即“動態調制”。這種方法通過動態調整系統參數,來優化PA的工作效率。

參數的動態調制

動態調制是指根據信號的輸出功率,實時調整系統中的某些關鍵參數(如供電電壓、供電電流、負載阻抗等),以達到優化功耗的目的。這種調制方式要求參數的變化必須非常迅速,以適應信號輸出的瞬時變化需求,達到接近實時的狀態。

以100MHz帶寬的5G NR信號為例,調制信號的變化需要達到納秒級別,才能與包絡信號的變化保持同步。這樣的速度要求遠遠超出了芯片內部數字接口電路的能力范圍。舉例來說,射頻前端標準接口協議MIPI RFFE的最大通信時鐘頻率為52MHz,發送一個完整的MIPI指令需要25個時鐘周期,即完成一個控制轉變需要0.48mS。這個速度比動態調制所需的切換速度慢了上百倍。

因此,為了實現參數的動態調制,通常會利用模擬控制接口,或者直接利用PA的內部特性來完成。

根據調節參數的不同,動態調制主要可分為以下三種類型:

Vcc動態調制;

Bias動態調制;

負載動態調制。

這些調制方式能夠更有效地管理功耗,尤其是功率回退時的功耗,提升系統的整體效率。

Vcc動態調制:

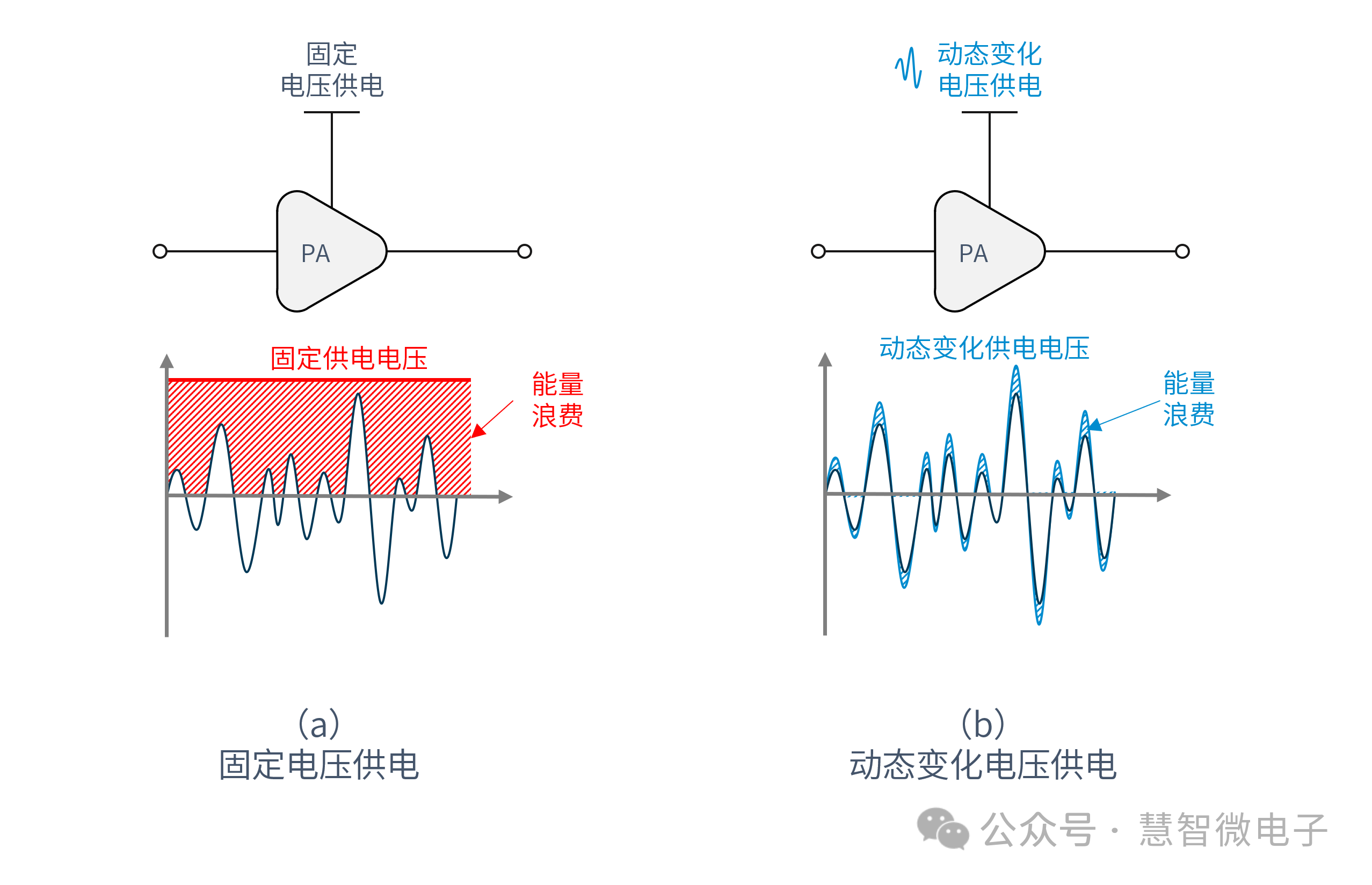

供電電壓的靈活調整。Vcc動態調制的核心思想在于,使PA的供電電源能夠隨信號幅度的變化而靈活調整,而非保持固定值。這種動態調整有助于顯著提高PA效率,減少不必要的能量損耗。

圖:固定電壓供電及動態變化電壓供電

上圖是Vcc動態調制的基本原理。對于高峰均比信號,其幅度隨時間快速變化。若采用固定電壓供電,將會導致顯著的能量浪費。而通過使電源電壓跟隨信號幅度變化,可以實時優化能耗。

實現Vcc動態調制的兩種主要技術是EER(Envelope Elimination and Restoration,包絡消除與恢復)和ET(Envelope Tracking,包絡跟蹤)。

EER技術

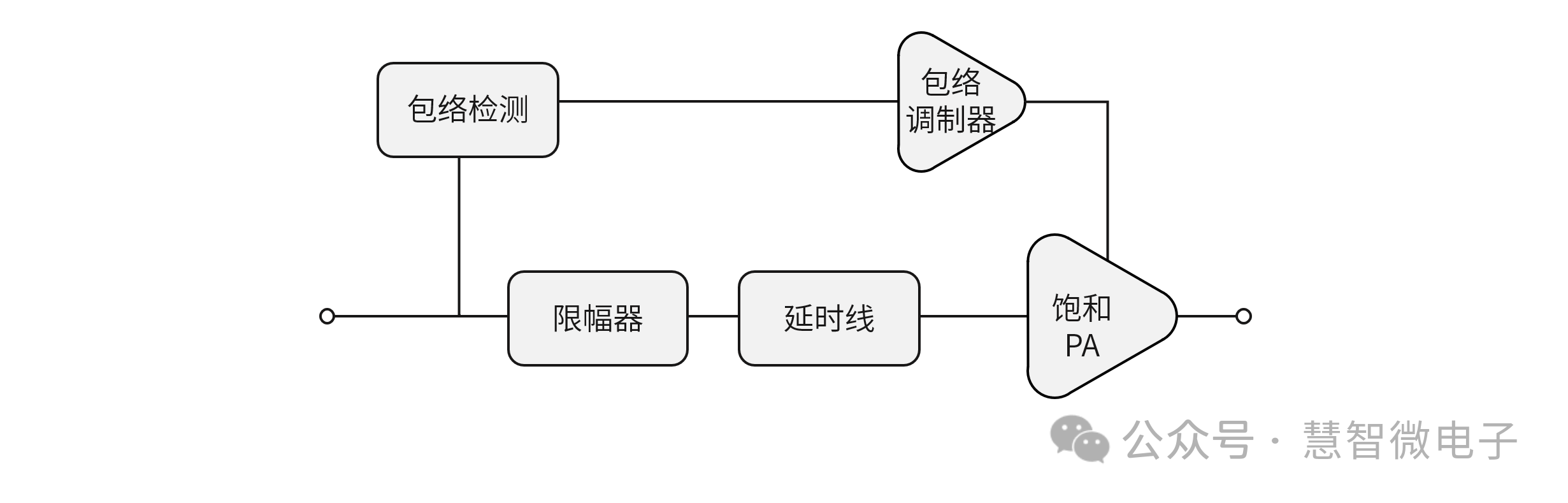

EER技術由Kahn教授于1952年提出,其基本原理是將輸入信號分解為兩部分處理[2]。其基本架構如下圖所示。

圖:EER PA系統架構

在EER架構中,一路信號忽略包絡信息,直接傳輸至工作在開關狀態的PA,從而實現高效放大。這一過程中,包絡信息被主動消除,故稱“包絡消除”通路。

另一路則負責“包絡恢復”。首先,通過包絡檢測電路提取包絡信號,然后輸入包絡調制器。輸出的包絡信號用作飽和PA的動態供電電源,既實現了電源的動態調制,又完成了包絡的恢復。

EER電路的優點在于巧妙地將包絡信號和載波信號分離處理,使得兩個通路各司其職,互不干擾,從而提高了系統效率。然而,它也存在一些缺點:

由于信號的幅度和相位信息被拆分,因此需要精確對齊兩個通路以確保信號的完整恢復。

EER過程中存在幅度消除和恢復兩個環節,若處理不當可能導致信號失真。

本質上,EER相當于包絡信號與高頻恒包絡信號的混頻,可能引發頻譜擴展問題。

鑒于EER技術的復雜性和挑戰性,另一種更為簡潔的PA系統結構——ET技術應運而生。

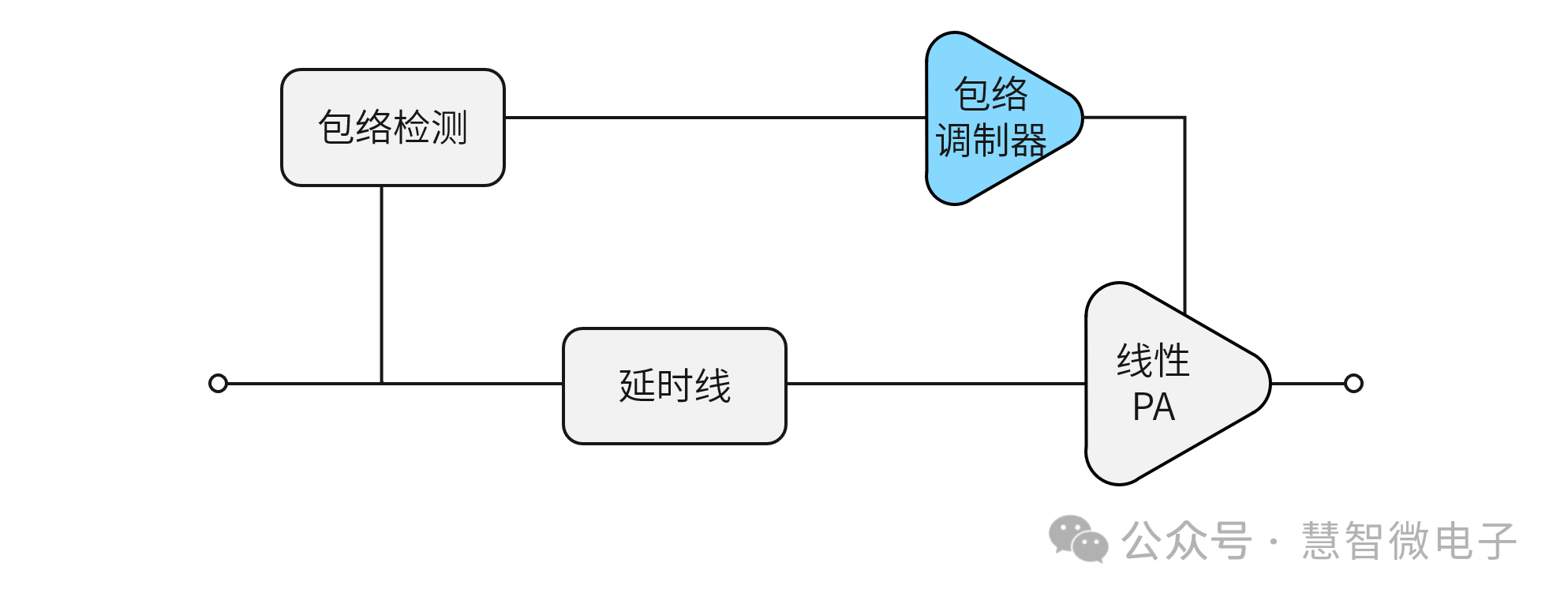

ET技術

ET,即包絡跟蹤技術,其核心理念是“跟蹤”信號所需的電源幅度,并為PA提供相應電源。這樣既節省了功耗,又避免了EER技術中復雜的信號拆分與對齊過程。結合ET技術,可以顯著提升系統整體效率。ET系統架構如下圖所示。

圖:ET PA系統架構

然而,ET技術的性能高度依賴于ET

Modulator的表現。為了輸出大帶寬(100MHz及以上)、大電流(2A及以上)的包絡信號,并保持高轉換效率,ET調制器的設計面臨巨大挑戰。隨著帶寬和電流能力的增強,實現高效率變得愈發困難。

在5G應用中,即使信號帶寬維持在100MHz,ET調制器的轉換效率通常也僅約80%,意味著存在20%左右的能量損失。因此,ET PA系統的收益必須足以彌補這部分能量損失才能實現整體收益。隨著未來信號帶寬的不斷增加,ET調制器的設計難度將進一步上升。

Bias的動態調制

除了對供電電壓Vcc進行動態調制外,PA的偏置電流,即Bias,同樣可以進行動態調制以優化性能。

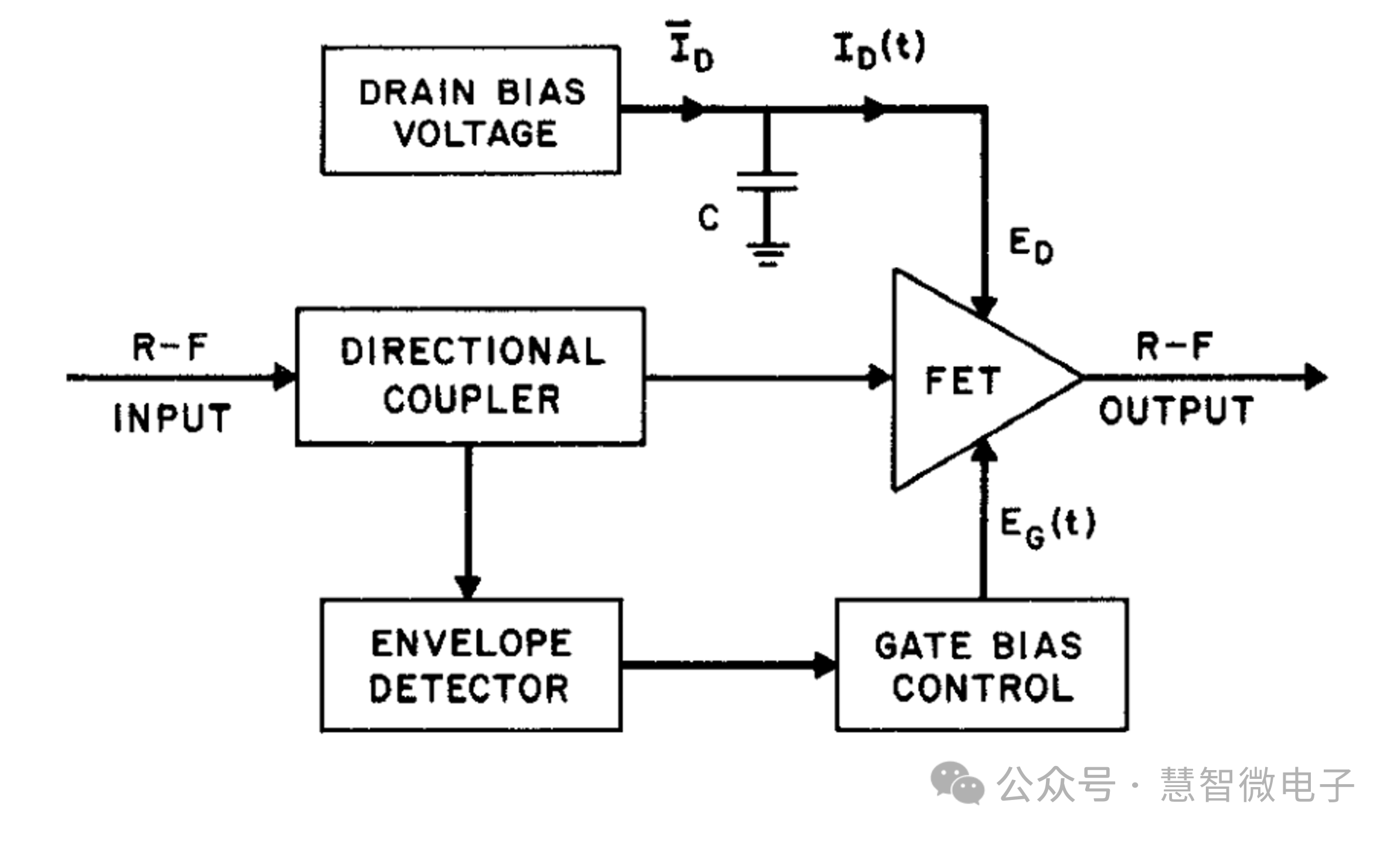

Saleh教授等人在1983年的一篇文章中,提出了一種創新的系統架構來提升PA的效率[3]。該架構的核心在于,通過提取輸入信號的包絡來控制PA的Bias,使Bias能夠隨輸入信號包絡的變化而動態調整。這種調整方式目標是實現PA效率的最優化。

圖:Saleh教授等于1983年提出的Bias調制PA架構

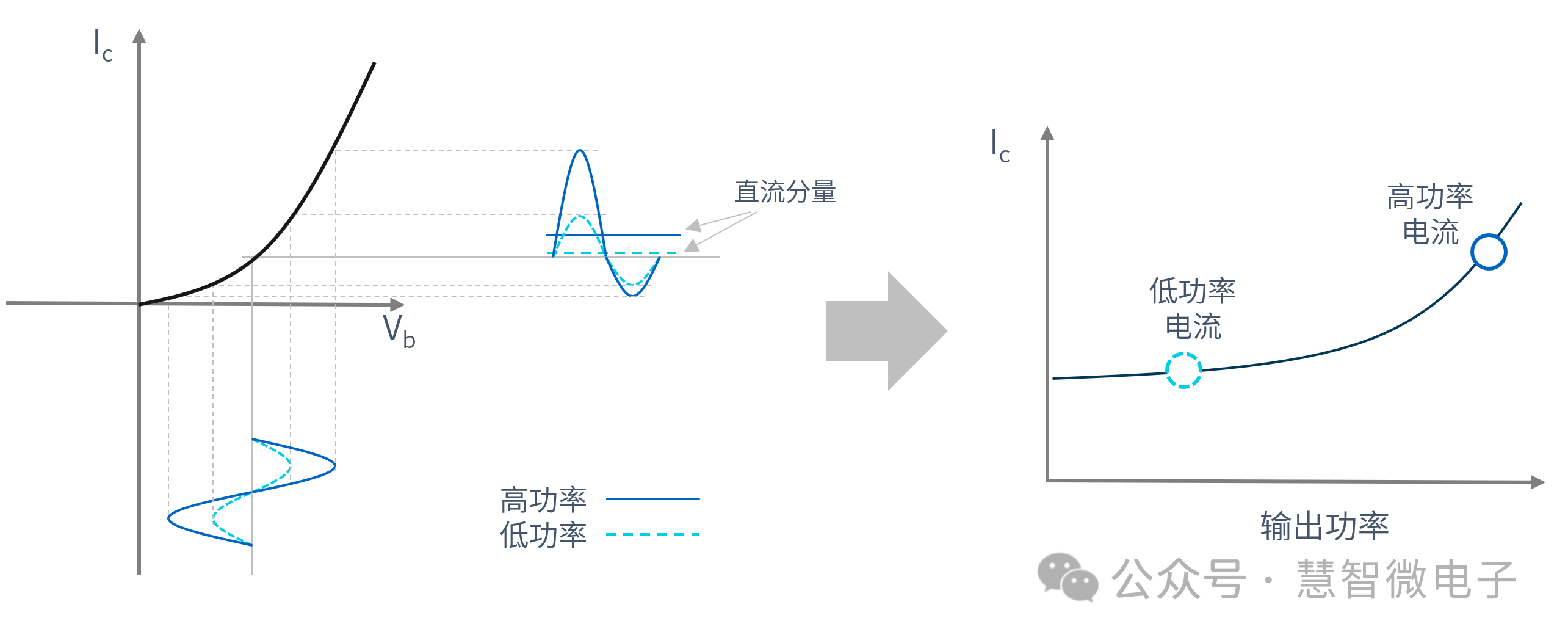

在現代PA設計中,“動態偏置”特性被巧妙地融入Bias電路的設計中,以提升效率并優化線性度。

以HBT PA為例,利用其偏置電壓Vb與Ic電流之間的指數關系,設計師們可確保偏置中心點Vb的盡量穩定。這時當大信號輸入時,Ic電流會自動增加,其工作原理如下圖所示。這種設計使得在大功率時提升Ic電流,而在小功率時減少Ic電流,從而實現了高效的動態調制[4]。

圖:電流的動態調制效應

負載的動態調制

除了電壓和電流的動態調制外,還存在一種獨特的調制技術,即負載動態調制(Load

Modulation)。PA的負載線(Load-line)在PA設計中占據至關重要的地位。負載線的高低直接影響著PA輸出功率的大小。

為了達到理想的輸出功率,PA的負載線通常是根據最大輸出功率來設計的。然而,這種設計在小功率輸出時顯得并不經濟:此時PA的工作功率遠低于其飽和功率。根據先前關于PA特性的討論,我們知道當PA的工作功率遠離飽和功率時,其效率會顯著降低。

盡管可以通過降低Vcc電壓來減少功率浪費,并降低輸出的飽和功率以提升PA在小功率輸出時的效率,但這種方法需要依賴ET技術。然而,ET調制器的成本相對較高,并且其在大帶寬下的效率是設計中的一大難題。

在這種情況下,對于小功率輸出的場景,我們可以利用負載線的特性來降低輸出飽和功率,從而提高效率。放大器的輸出功率與供電電壓成正比,與負載阻抗成反比。在供電電壓固定的情況下,可以通過增加放大器輸出負載的方式來降低PA的飽和輸出功率,從而提升小功率輸出點的效率。這正是負載動態調制的核心理念。

在實施方面,負載動態調制主要采用以下幾種方法:

通過可調匹配網絡實現;

利用Doherty架構實現;

借助Out-phasing架構實現;

采用Load Modulation Balance PA架構。

可調匹配網絡實現

可調匹配網絡方法的核心在于,在PA的匹配網絡中融入可由包絡信號控制的可調無源器件。經過精心設計,這種匹配網絡能夠實現負載阻抗隨功率的特定變化。以下是Kenlen Chen教授于2012年所發表論文中展示的架構圖[5]。

圖:可調匹配網絡示意

此方法的直觀性和易于理解性是其顯著優點。不同功率點對應不同的阻抗,設計師只需通過匹配網絡和相應的控制信號設計到相應的目標阻抗,便可實現阻抗的特定轉換。

然而,這種方法也存在局限性。其可控范圍有限,且受限于匹配網絡的固有特性,目標阻抗可能無法完全符合預期變化。此外,尋找滿足低插損、高集成度、大范圍調節和快速響應的可調器件也是不小的挑戰。

因此,多種等效負載阻抗調諧方法應運而生。在這些方法中,負載阻抗并非真正被調節,而是通過電路等效方式使其發生變化,從而達到相應改變PA特性的目的。其中,Doherty、Out-phasing和Load Modulation Balance PA三種實現方案尤為突出。

Doherty架構實現

從負載動態調制的系統角度來看,仍有必要重新審視Doherty PA。深入理解Doherty PA中的動態負載調制效應,將有助于更好地理解其他兩種負載動態調制架構。

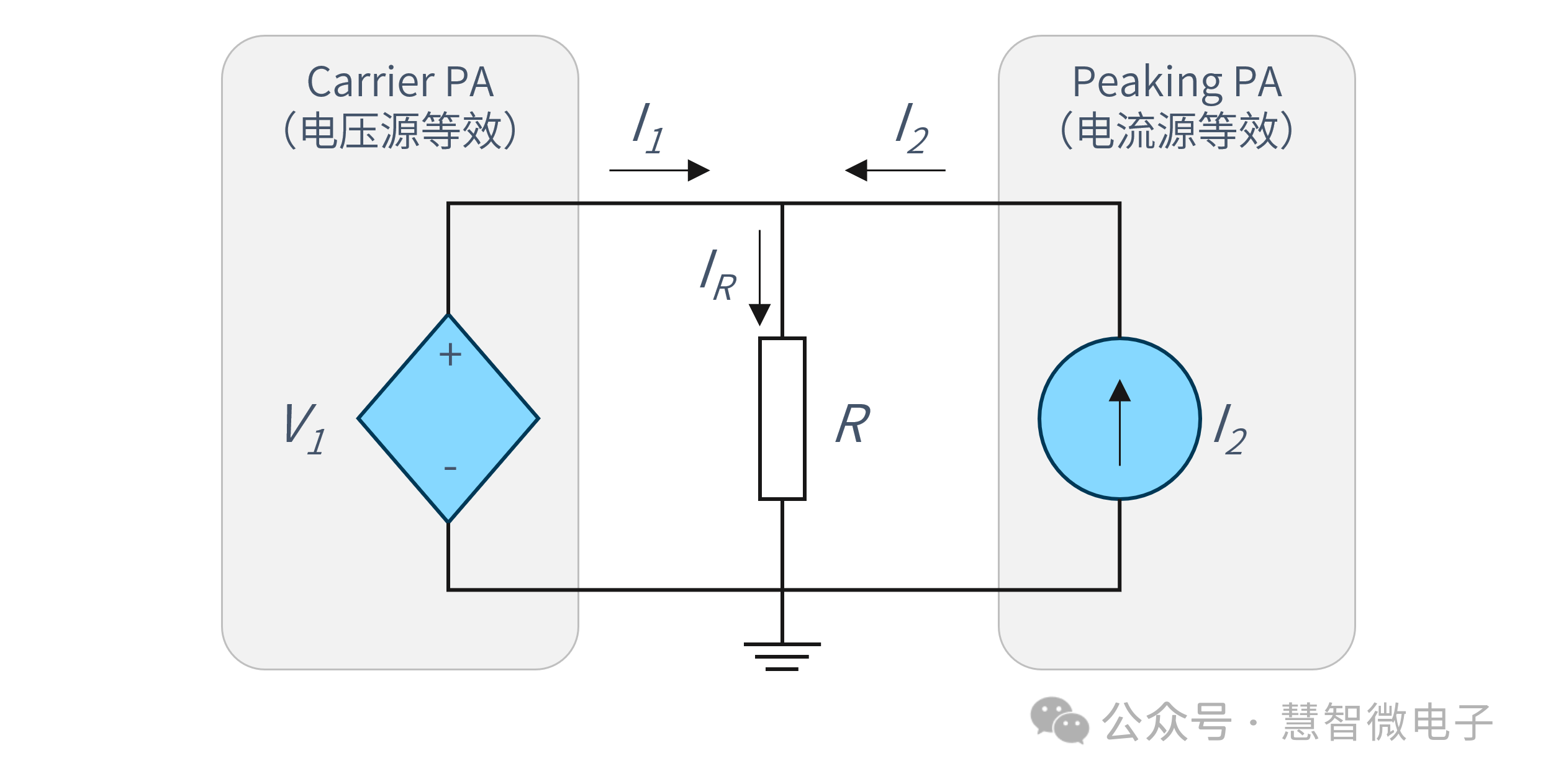

Doherty PA由兩個PA組成,但它們并非簡單合成。通過對兩個PA進行阻抗轉換,其工作原理可簡化為下圖所示[6]。

圖:Doherty PA的簡化電路

在此圖中,左右兩個電源分別代表Doherty PA中的Carrier和Peaking兩個PA。左側的Carrier PA通過阻抗變換被設計為等效電壓源,而右側的Peaking PA則設計為等效電流源。這兩個PA共同作用于同一個負載阻抗R上。

由于負載R直接連接在電壓源V1兩端,因此R兩端的電壓即為V1。根據歐姆定律,流過R的電流為V1/R。

值得注意的是,雖然電壓源為電阻R提供電壓,但它并不能控制其流向電阻R的電流。因為R上的電流由兩部分組成:一部分是電流源I2強制輸出的電流,另一部分是向電壓源請求的電流。電流源I2會強制輸出一個電流I2,因此電阻R向V1請求的電流僅為V1/R-I2。

對于電壓源V1而言,其輸出電流的大小會受到另一個電流源I2的影響。根據V1輸出的電壓和電流,我們可以計算出電壓源V1看到的等效阻抗為RLoad=V1/(V1/R-I2)。

從上述公式中可以看出,V1看到的阻抗會隨著I2輸出的大小而變化,仿佛V1的負載阻抗被外部控制了一樣。這就是動態負載調制效應。

在Doherty PA設計中,正是利用了這種效應。通過Peaking PA的開啟與關閉,可以控制Carrier PA看到的阻抗變化。通過匹配轉換網絡的設計,當Peaking PA開啟時,Carrier PA看到的阻抗降低,從而提升PA的輸出功率以實現高功率輸出;同時,當關閉Peaking PA時,Carrier PA看到的阻抗提升,此時PA的輸出功率降低,換回了較高的效率。

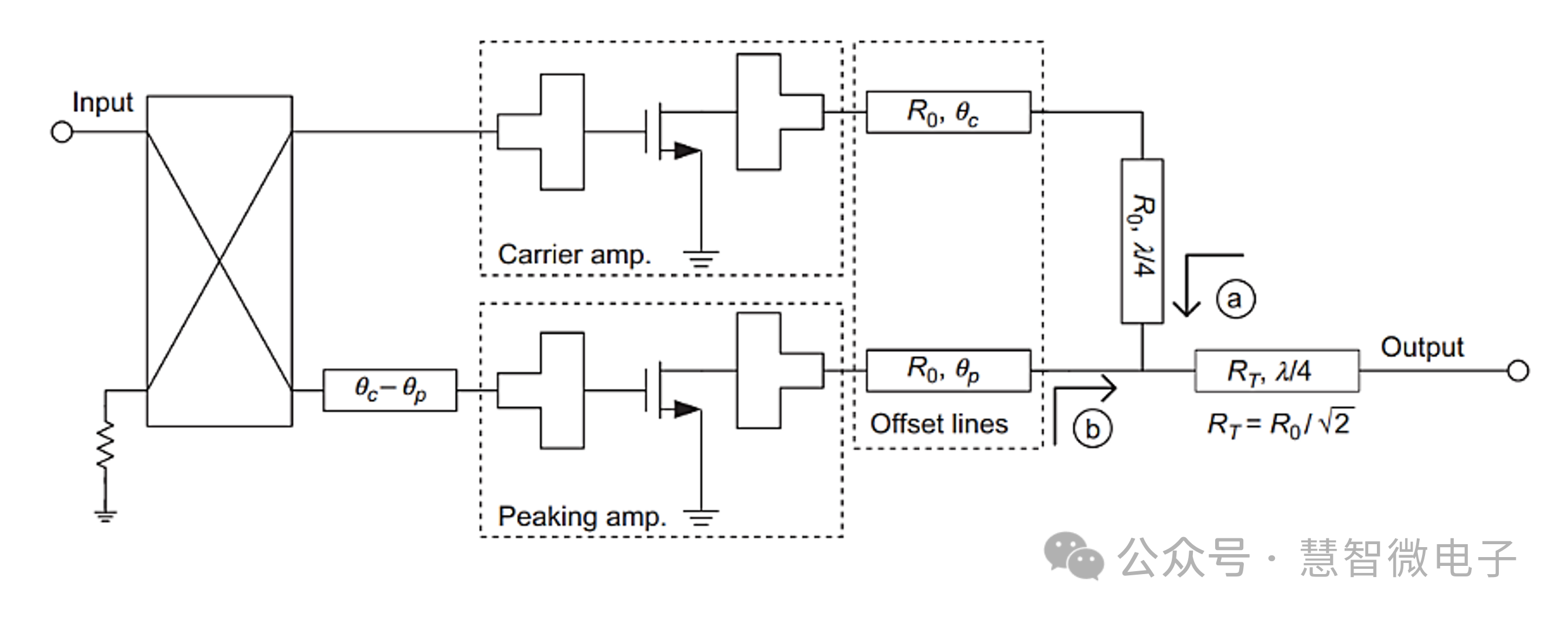

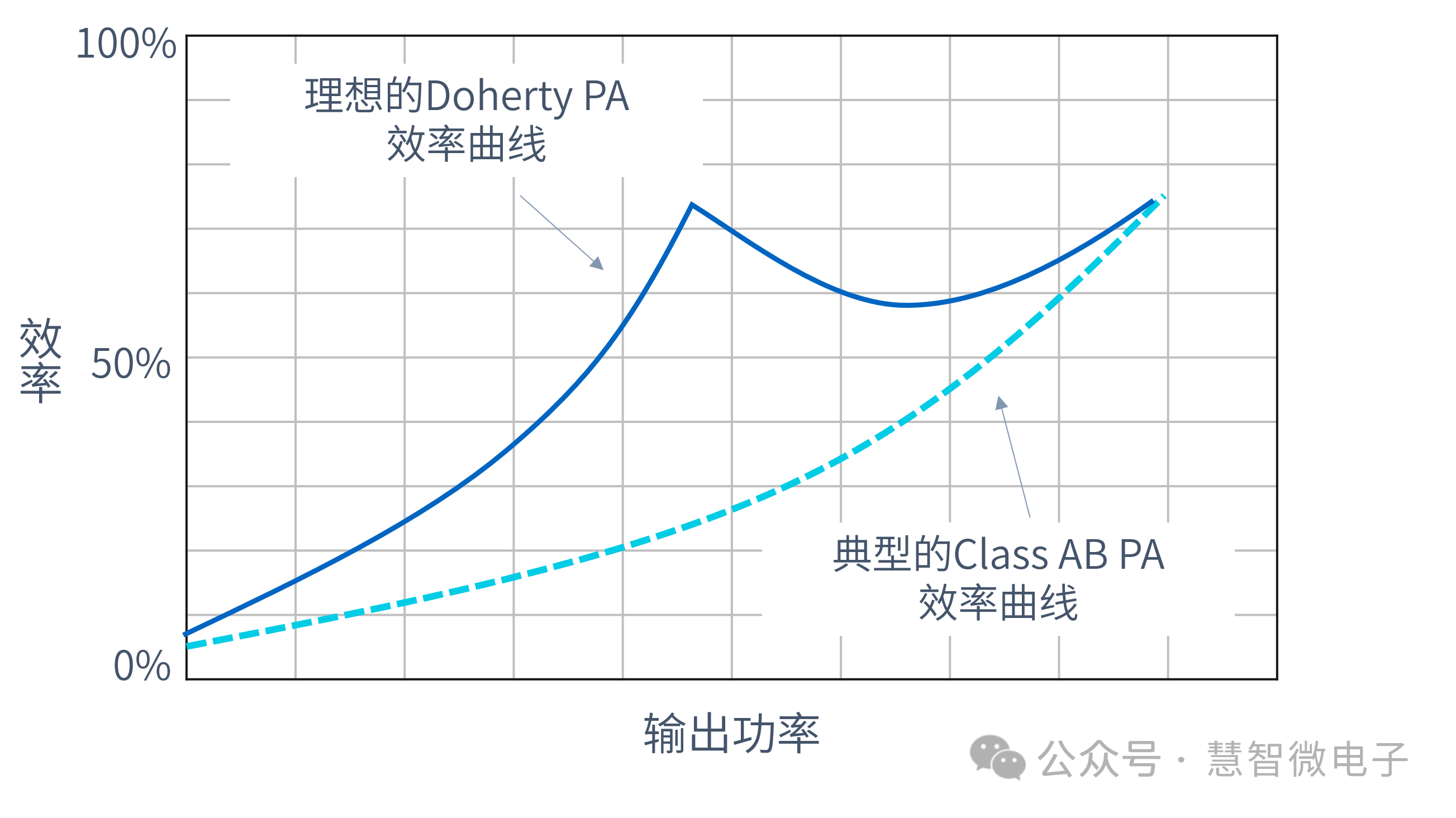

通過這種方式,Doherty PA通過負載線的動態調整實現了高功率和高效率的兼顧。以下為Doherty PA的完整實現架構以及典型的效率特性曲線圖。

圖:完整的Doherty PA電路

圖:理想的Doherty PA效率曲線

盡管Doherty PA在高功率和效率方面表現出色,但它也存在一些明顯的缺點。首先,兩路PA在切換時會影響線性度,因此通常需要與DPD技術結合使用;其次,Doherty PA利用了大量的阻抗變換網絡來實現電壓源和電流源的等效變換,這些網絡的相對窄帶特性限制了Doherty PA的帶寬;最后,Doherty PA對負載變化較為敏感,需要相對固定的PA輸出阻抗。

在過去幾十年的發展中,Doherty PA在基站中得到了廣泛應用。在這些應用場景中,有強大的DPD支持、只需針對特定運營商的較窄頻段設計、負載相對固定(如固定天線),這些條件恰好滿足了Doherty PA的系統需求。

近年來,一些廠商嘗試將Doherty PA應用于手機中。為了適應手機等移動終端有限的DPD算力、全球頻段支持和不斷變化的負載等挑戰,手機中應用的Doherty PA通常會弱化其Doherty特性。這樣一來,PA就不會對周圍環境和帶寬過于敏感。然而,這種設計也會相應地削弱Doherty PA對效率的改善效果。

Out-phasing架構的實現

在理解了Doherty PA架構之后,Out-phasing架構就變得相對容易掌握了。

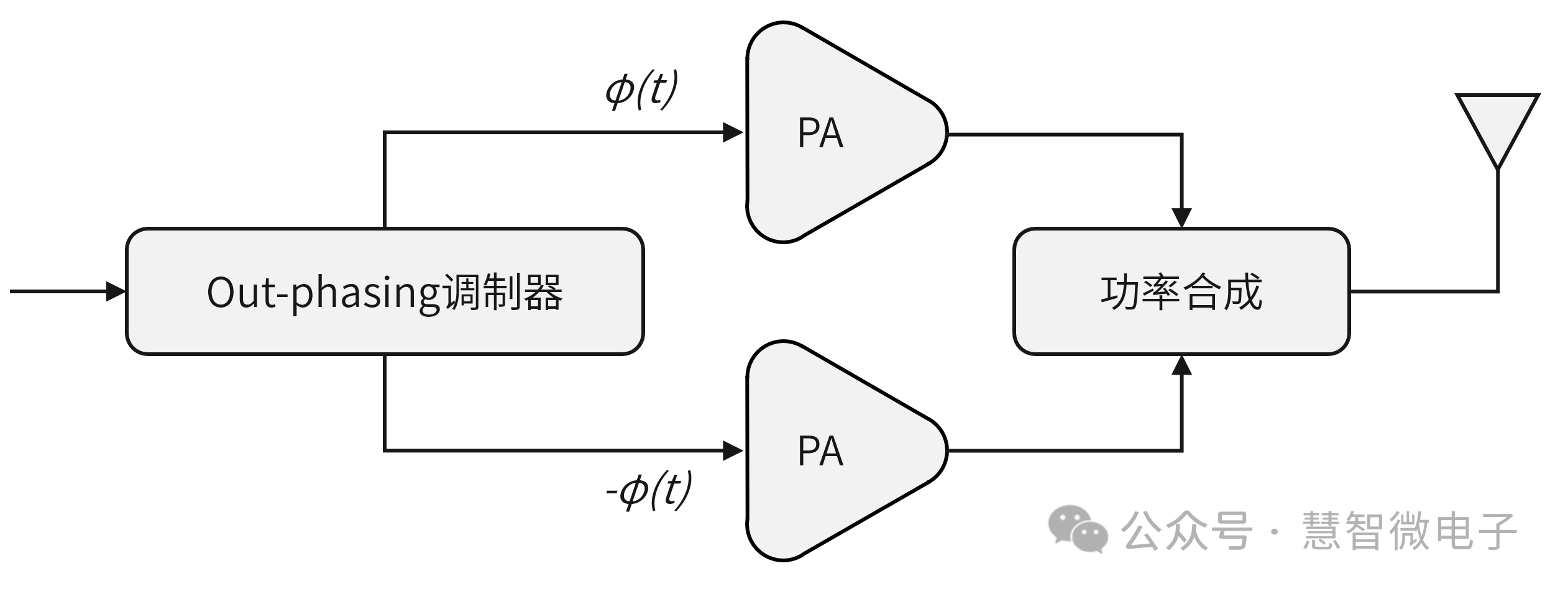

顧名思義,Out-phasing技術是通過利用不同“相位”(Phase)的PA來實現特定設計的。其代表性的架構圖如下圖所示[7]。

圖:Out-phasing PA架構

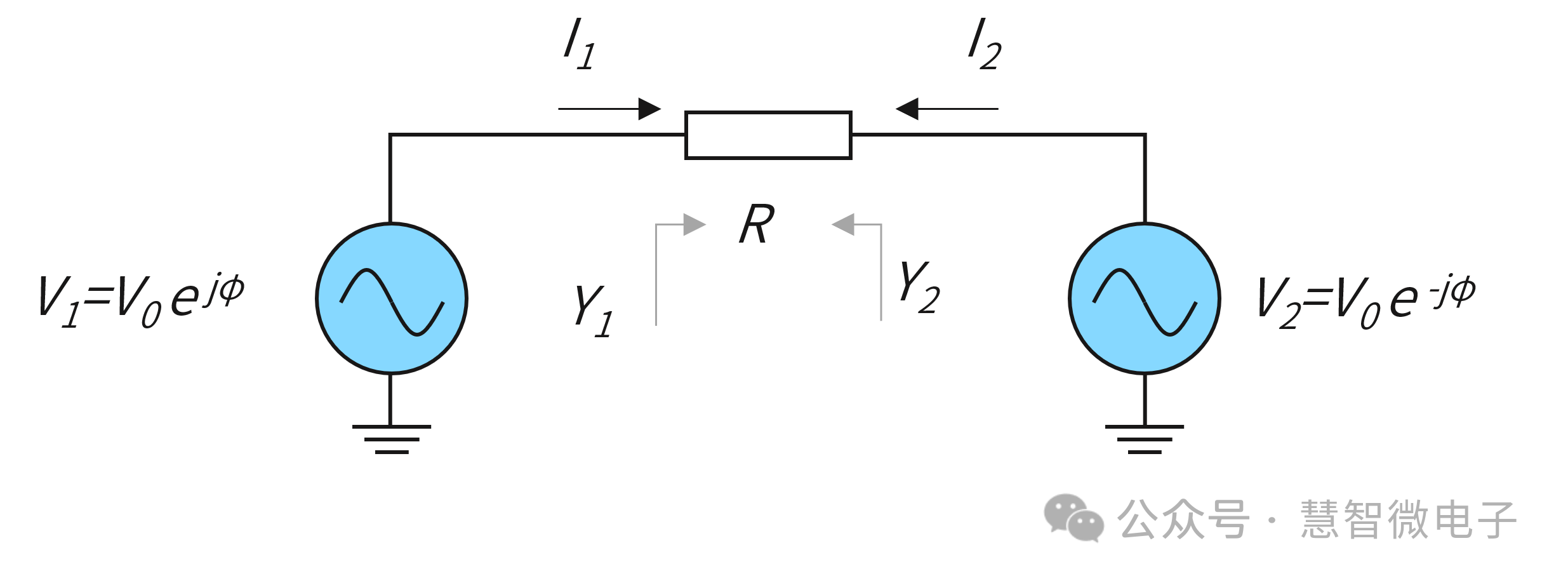

與理解Doherty PA類似,我們同樣可以將Out-phasing PA簡化,簡化后的等效電路圖如下所示。

圖:Out-phasing PA簡化電路圖

從圖中可以看出,負載阻抗RL兩端的電壓隨著兩個電壓源的相位變化而波動,因此流過RL的電流也會隨之調整。

需要注意的是,每個電壓源所見的等效阻抗并非RL,而是其自身電壓與電流的比值。因此,每個電源的等效阻抗也隨相位的變化而改變。這意味著,通過調控輸入到兩路PA的相位,我們可以實現對兩路PA負載阻抗的精準控制。這也就是利用Out-phasing架構,對負載進行調制的原理。

Load Modulation Balance PA架構

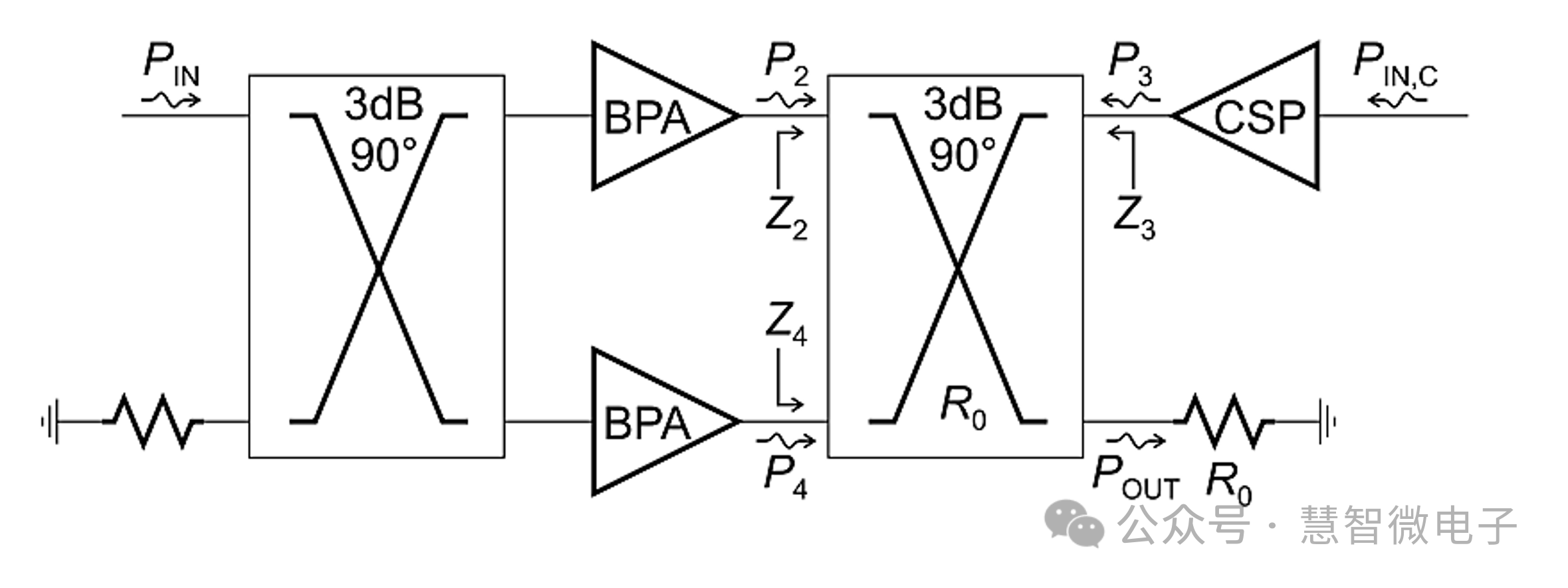

Load Modulation Balance PA(LMBA)是射頻功率放大器領域的杰出專家Cripps在2016年提出的一種創新型架構[8]。該架構的示意圖如下所示:

圖:LMBA架構

LMBA是在傳統Balance PA(BPA)的基礎上進行改造而來的。與傳統的BPA(通常只有兩路PA進行90度合成)不同,LMBA增加了一路PA,Cripps教授將其命名為CSP(控制信號功率)。CSP信號被注入到90度合成網絡的隔離端口中,這一信號的引入會影響兩路BPA所見的負載阻抗。通過調整CSP信號的大小,可以等效地控制BPA的負載阻抗,進而影響PA的輸出功率和效率。

LMBA的獨到之處在于它將影響負載阻抗的PA獨立出來,并允許通過單獨的信號進行控制。這與Doherty PA和Out-phasing PA只能依賴兩路PA自行調節的方式不同,從而極大地便利了負載調制PA的應用。

基于這一基本架構,一些文章已經開展了對Doherty與LMBA結合、不同類別的PA作為CSP

PA的影響等方面的研究。對此感興趣的同學可以查閱相關論文。

總結

在射頻系統中,PA是主要的能耗器件。為了有效降低PA的功耗,針對PA的研究也不能只停留在PA單體層面,還應更廣泛地從系統角度來探索解決方案。

從系統角度考慮,優化PA效率可能的方案有:

隨著技術平臺的不斷進步和PA技術的持續發展,未來肯定還會有更多創新的系統級手段涌現,以進一步降低PA的功耗。

-

射頻

+關注

關注

105文章

5671瀏覽量

168938 -

射頻功率放大器

+關注

關注

8文章

141瀏覽量

23328 -

PA設計

+關注

關注

0文章

3瀏覽量

1832

原文標題:高效率PA:系統級設計

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

高效率通信電源技術

高效率開關電源設計與制作

高效率高線性的功放怎么實現?

高效率電源的設計

高效率開關電源的設計及應用

何為高效率電機

提高效率的DC電源模塊設計技巧

評論