曾有人在STMCU社區網站咨詢如下問題:

由于實驗需要,要用到STM32F407的兩個DMA并用定時器觸發,在使用過程中發現DMA1無法把GPIO的IDR數據傳輸到內存,調試過程中出現DMA1的數據流傳輸錯誤標志,但是使用DMA2沒有問題。另外當把訪問GPIO的IDR改成訪問APB1下的tim5的ARR時,DMA1也能正常工作。請問這是怎么回事?

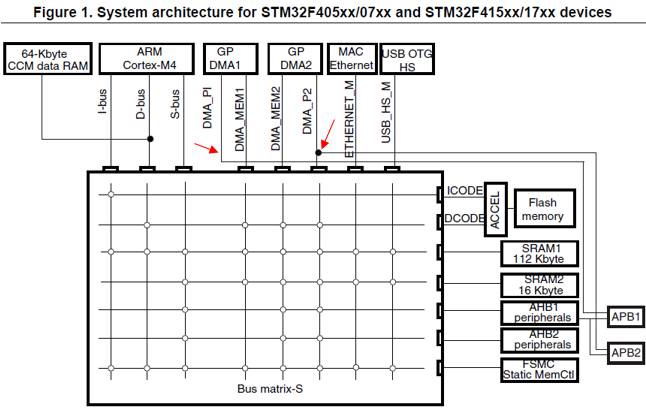

咨詢者提到STM32F4系列中DMA1與DMA和另外兩個外設GPIO和TIM5 。為了弄清這個問題,我們有必要先看看STM32F407的總線與存儲框架圖。 如下圖所示:

整個系統架構由多層32位AHB總線矩陣及主從總線構成,并建立起各個主從模塊間的互聯訪問。借助于總線矩陣,可以實現主控設備到從控設備的訪問,可以實現多個高速外設的并發訪問和高效運行。[需要注意的是,對于STM32F4系列,圖中64K CCM并不經過總線矩陣,只能被CPU訪問。自然DMA是不能訪問它的.]

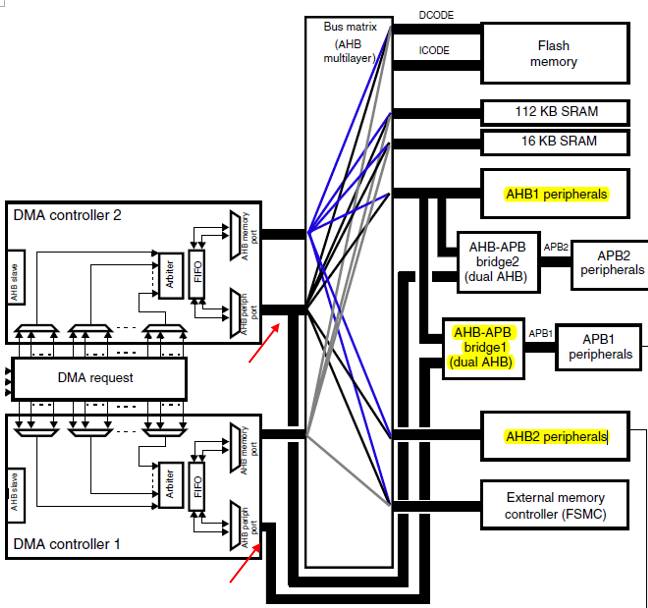

我們接著看看STM32F407 的DMA1和DMA2的訪問框架圖。這兩個DMA都具有雙AHB總線訪問端口,一端用于存儲器訪問,另一端用于外設訪問。

結合這幅DMA總線訪問框圖和上面的系統存儲總線框架圖可以看出,2個DMA的外設訪問端口的總線連接有點不一樣。

DMA2的外設訪問端口既與總線矩陣相連,經過矩陣可以訪問AHB外設,又與AHB-APB橋2相連,可以進一步訪問APB2外設;而DMA1卻沒有與總線矩陣相連,只是跟AHB-APB橋1相連,從而訪問APB1外設。[長方形方框代表總線矩陣]

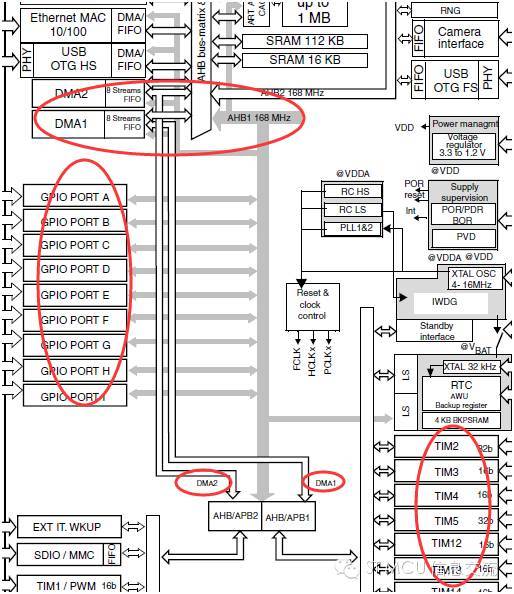

現在的問題是說DMA1訪問不了GPIO,但如果換成TIM5就可以。我們可以去芯片數據手冊的Device overview部分查看相關總線和外設聯結圖。截取STM32F40x block diagram的部分如下:

不難看出GPIO外設跟AHB1相連;TIM5跟APB1相連。我們再結合中間的DMA訪問框圖看得清楚,DMA1的外設端口根本沒連接AHB1,自然沒法訪問相應外設,比如GPIO。而DMA2 可以,因為它可以經過總線矩陣后再去訪問AHB1的外設。DMA1為什么能訪問TIM5也不難解釋了,因DMA1的AHB外設端口總線經過AHB/APB1橋后就可以訪問APB1各類外設,而TIM5就是掛在APB1總線上的外設之一。

咨詢者的問題基本上靠看上面幾幅圖可以得到答案。這些圖很重要,很多信息用圖描述也很直觀明了。各技術手冊里的插圖往往大有乾坤,不要視而不見。上面提到的都是基于STM32F4系列的總線架構,你也可以去看看其它系列的系統總線框圖,相信你一定會另有發現和收獲。

-

存儲器

+關注

關注

38文章

7524瀏覽量

164136 -

STM32

+關注

關注

2270文章

10921瀏覽量

356938 -

總線

+關注

關注

10文章

2898瀏覽量

88261

原文標題:一個跟STM32F4系統總線架構有關的問題

文章出處:【微信號:STM32_STM8_MCU,微信公眾號:STM32單片機】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

STM32F4系統總線架構介紹

STM32F407 DCMI攝像頭源碼

STM32F407與STM32F105 CAN通訊失敗的定位解決

STM32F407芯片介紹

【STM32F407開發板用戶手冊】第19章 STM32F407的GPIO應用之按鍵FIFO

STM32F407總線存儲框架及應用設計

STM32F407總線存儲框架及應用設計

評論