這里講解SATA主機協議的物理層的實現過程。

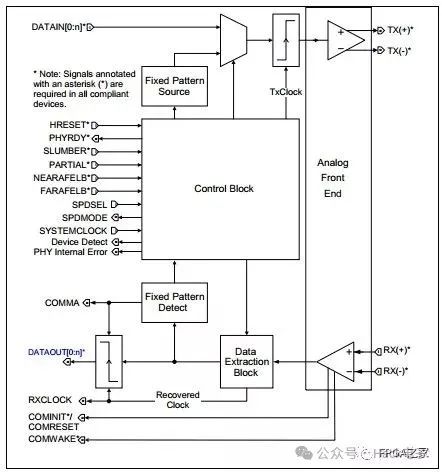

下圖是標準SATA協議文檔中給出的物理層結構。可以看到它包含控制模塊、時鐘數據提取單元、同步字符源和同步字符檢測模塊以及模擬前端幾個部分。其中,控制模塊負責協調控制整個物理層的邏輯功能,并向上層協議提供控制信號、狀態信息接口。時鐘數據提取模塊從串行數據流中提取時鐘數據信息。同步字符源和同步字符檢測兩個模塊負責串并/并串轉換過程中的字節對齊。模擬前端包含高速差分數據發送接收器和OOB信號檢測與生成電路。

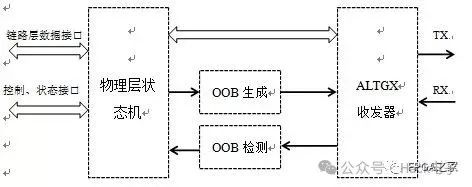

上面這個圖看上去比較復雜,但是如果仔細理解物理層協議,并對前一篇博客中提到的ALTGX收發器有一定認識之后,我們會發現其實這個收發器已經幫我們實現了時鐘數據提取單元、同步字符源和同步字符檢測模塊以及模擬前端這幾個部分,我們要做的就是如何配置這個收發器。另外,物理層還有一個重要的工作就是利用OOB(OUT OF BAND)信號實現設備的識別和上電初始化。因此,這里進一步劃分物理層模塊,得到下面這個物理層框圖。整個物理層被劃分為4個模塊,OOB生成和檢測、ALTGX收發器和物理層狀態機。

首先說一下這個ALTGX收發器。關于這個收發器具體結構這些東西這里限于篇幅就不一一介紹,詳細的介紹參考StatixIV器件手冊,這里只是說明一下為什么會用上它。我們知道現在常見的FPGA的處理速度最高也只是在幾百兆的水平,但是SATA1.0的串行數據流的傳輸速度已經達到了1.5Gbps,這樣的速度不可能直接在FPGA里實現,而且SATA最終在傳輸線上傳輸的是差分信號,這里會有一個數字到模擬的過程,這也不是一般的FPGA能干的事。上面這兩個問題其實并不只是實現SATA協議時會碰到,很多高速串行傳輸協議在使用FPGA實現時都會遇到,比如PCIe等。FPGA廠商為了滿足對這種高速串行傳輸協議的支持,通常的做法都是在FPGA芯片中集成專用的硬件,這種專用硬件通常是一組滿足高速數據傳輸速率要求的串行器/解串器(SERDES)以及模擬前端。這些集成的專用硬件通常是可以進行比較靈活的配置的,以使它們能滿足對不同通信協議的支持。ALTERA公司的ALTGX收發器就屬于這種,另外還有XILINX公司的RocketIO MGT等。ALTGX收發器可以通過QuartusII軟件中的IP配置向導配置生成,這個配置過程參考“實現Altera器件中的SATA與SAS協議”一文。這篇文檔中有詳細的配置講解,這里不再贅述。

接著說說這個OOB信號。帶外信號,即OOB信號是物理層特有的一組信號,它通過在數據線上傳輸一組特定格式的信號實現。OOB信號有3個,分別是COMRESET、COMINIT和COMWAKE,其中COMRESET與COMINIT信號組成形式一樣,只不過CONRESET由主機發出,而COMINIT由設備發出,它們的作用是在正常的通信鏈路沒有建立之前主機進行SATA設備識別。關于這三種信號的組成形式請查閱SATA協議文檔,這里主要說一下怎么實現這幾個信號。上面關于ALTGX配置過程中我們應該注意到兩個比較特殊的信號端口,一個是rx_signaldetect,一個是tx_forceelecidle,我們主要是通過控制這兩個端口產生和讀取OOB信號。查閱SATA文檔之后我們知道OOB信號實際是由數據線上的突發信號和空閑周期組成的,突發信號周期比較好理解,在差分數據線上傳輸特定的原語(ALIGNp)即可,那空閑周期是什么意思呢?簡單的理解就是不發送數據,那怎么就代表不發送數據呢?分析tx_forceelecidle這個端口的作用我們大概可以得到一些啟示。這個端口的作用是將ALTGX中的發送器強制置為高阻,原來“高阻”才意味著沒有數據發送,千萬不要以為發送器發送“0”就是空閑周期了,“0”也代表一個數據!相反地,在接受端就比較好理解了,對于差分信號來說,在接受器端設置閾值電平檢測電路就能區別差分數據線上“有或沒有”信號,也就是區分突發周期和空閑周期,反映閾值檢測結果的信號就是rx_signaldetect這個端口。這樣就好理解OOB信號的具體實現了,當發送OOB信號時,通過置位或復位tx_forceelecidle端口來發送空閑周期和突發信號周期,接收設備端的OOB信號時,通過檢測rx_signaldetect端口信號電平來確定當前設備發送的是空閑周期還是突發信號周期,當該端口被置位,說明接收到的是突發信號周期,否則是空閑周期。這里需要提醒一下的是這兩個端口的信號都是高電平有效的,這意味著tx_forceelecidle為高電平時是空閑周期,而rx_signaldetect為低電平時為空閑周期。這一點一定要注意,這跟XILINX FPGA中的信號電平定義好像不太一樣,我當時就在這里吃過虧。接下來的OOB生成和檢測模塊的實現就好辦了,我們要做的工作就是實現能產生和檢測一組符合OOB信號規定的高低電平電路就可以了。

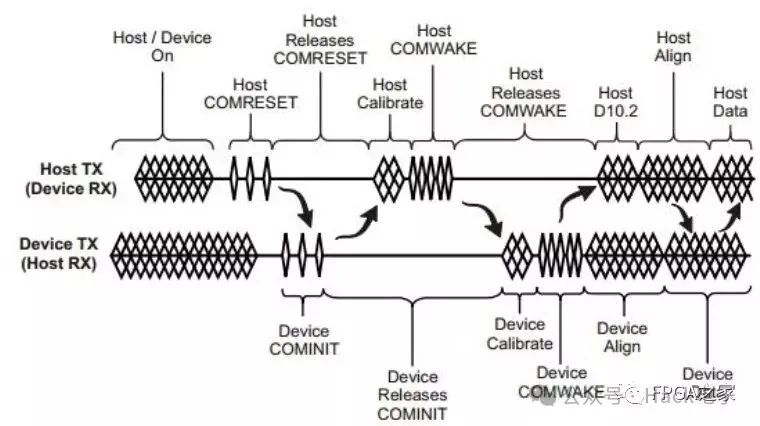

最后說說這個物理層狀態機。物理層狀態機是整個物理層電路工作的大腦,它主要負責控制前面提到的三個模塊,在上電時完成主機對SATA設備的識別和通信鏈路的建立。下面這個時序圖就是上電時主機初始化的過程。首先是主機發送COMRESET信號,設備接收后響應COMINIT,主機接收之后發送COMWAKE,設備接收后再響應COMWAKE。四個OOB信號交互之后,主機就完成了SATA設備的識別。之后主機與設備之間通過ALIGNp原語進行速度協商并完成通信鏈路的建立,最后在通信鏈路建立之后以SYNCp保持。詳細的描述參考文檔中關于這部分的描述。

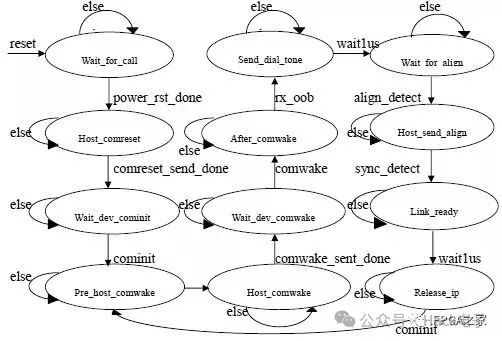

根據上面的時序圖,我設計了以下的狀態機,它的狀態轉移圖如下圖所示,供大家參考。

物理層狀態機共有12個狀態,狀態轉移圖上圖所示。主機上電后需要先對ALTGX收發器進行復位操作,使CDR能成功鎖定到接收數據。當復位完成后,狀態機能接收到power_rst_done信號,狀態機進入發送COMRESET狀態,使能OOB信號生成模塊發送COMRESET信號。如果設備接收到COMRESET信號,設備會向主機發送COMINIT信號,主機接收到COMINIT信號后,狀態機進入發送COMWAKE信號狀態,使能發送模塊發送COMWAKE信號,之后主機等待設備響應COMWAKE信號。主機在接到COMWAKE信號后會向設備發送一段時間D10.2數據,直到檢測到設備發送的ALIGNp原語。這時主機存儲ALIGNp原語,并以相同的速率返還給設備,完成速度協商。最后設備向主機發送SYNCp原語,主機在接收到該原語后進入Link_ready狀態,表示通信鏈路已經建立。

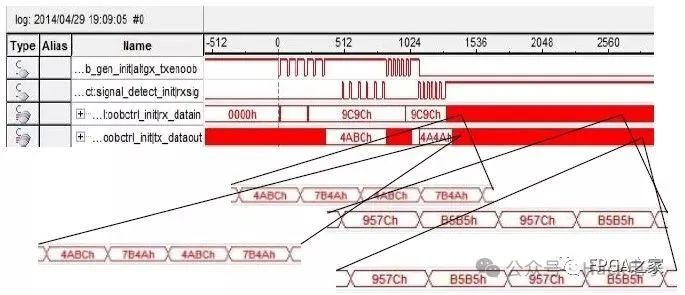

最終整個物理層的實現情況如下圖所示,這是用SignalTapII捕捉到的信號波形。第一個是OOB信號發送,即tx_forceelecidle端口控制信號,第二個是OOB信號接收,即rx_signaldetect端口信號,第三個是ALTGX接收轉換后的16位并行數據,第四個是ALTGX發送的16位并行數據。

至此,物理層基本邏輯設計完成

-

收發器

+關注

關注

10文章

3539瀏覽量

106916 -

SATA

+關注

關注

0文章

268瀏覽量

84125 -

物理層

+關注

關注

1文章

154瀏覽量

34783 -

模擬前端

+關注

關注

3文章

199瀏覽量

30122

原文標題:SATA主機協議的FPGA實現之物理層設計

文章出處:【微信號:Hack電子,微信公眾號:Hack電子】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

評論