總線分類

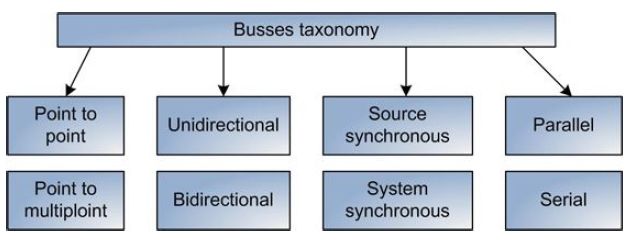

總線是一個被用來連接兩個或多個模塊和設備的設計組成。下圖展示了不同總線的分類。

01

點對點

只連接兩個設備或模塊的一種總線。點對點總線的優勢在于更好的信號完整性。

02

點對多

連接至兩個以上的模塊或設備的總線。點對多總線的優勢在于由于低數量軌跡帶來的低引腳數量和更簡化的板級設計。

03

單向

被單一模塊和設備驅動的總線連接至另一個總線。單向總線的優勢在于更簡便的執行,以及更簡便的板級終端方案。

04

雙向

可被任何設備或模塊驅動的總線連接至另一總線。其優勢在于由于共用相同總線信號帶來的更低的引腳數量。

05

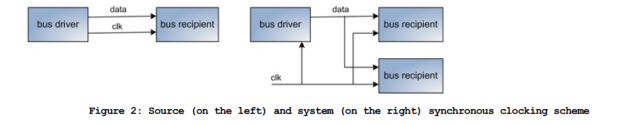

源同步時鐘

是一種在一總線上產生伴隨數據的時鐘的技術。這一方法的一個優勢在于它簡化了系統的時鐘設計,并且將總線驅動從接收方分離開。這一時鐘方案被用在幾個高速接口,如spi和pci接口。時鐘信號可以被分開,或嵌入到數據中,并且在接收端恢復。

06

系統同步時鐘

設備和模塊連接到一個總線并使用一個單一時鐘,不像源同步時鐘方法,系統同步時鐘方案不需要在接收端分離時鐘域。

07

并行總線

并行總線一般被用于中低頻總線中,對于中低頻的組成并沒有明確的定義,但經驗法則認為低于100MHz為低頻。100-300MHz為中頻。

Xilinx 提供了幾個可以被用來設計并行總線的元素:

1.IDDR:

一個專用寄存器,可在FPGA架構中將雙速率數據轉換為單速率數據輸出。

2.ODDR:

一個專用寄存器,可將輸入單速率數據轉換為雙速率外部輸出。

3.IODELAY:

被用來給輸入數據提供一個固定或可調節的延遲或給輸出數據提供一個固定延遲的設計元件。IODELAY主要被用來做輸入與輸出數據的對齊。

4.IDELAYCTRL:

與IODELAY一起用于控制延遲邏輯。 其中一個IDELAYCTRL輸入是一個參考時鐘,它必須是200MHz才能保證IODELAY中的分接頭延遲精度。在高頻率校準并行總線的時候需要調整輸入與輸出的延時。調整過程是動態的,在電路板加電之后并在操作過程中定期執行。執行動態總線校準有幾個原因。 例如,溫度和電壓波動會影響信號延遲。 此外,由于制造工藝的差異,PCB上和FPGA內部的跟蹤延遲也會有所不同。 由于不同信號上的可變延遲,并行總線數據可能會偏斜。

08

串行總線

并行總線不能擴展到更高的運行頻率和總線寬度。設計一個高頻率的并行總線是有挑戰性的因為多個數據信號之間的偏差,嚴格的時間預算,以及需要執行所有總線信號的長度匹配的更復雜的電路板布局。為了克服這些挑戰,許多系統和幾個眾所周知的通信協議已經從并行遷移到串行接口。其中兩個例子是Serial ATA,它是ATA或并行ATA的串行版本,PCI Express是下一代并行PCI。

串行總線的另一個優點是引腳數量較少。 串行總線的一個缺點是它的PCB設計要求更高。 高速串行鏈路通常以數千兆位的速度運行。 結果,它們產生更多的電磁干擾(EMI)并消耗更多的功率。

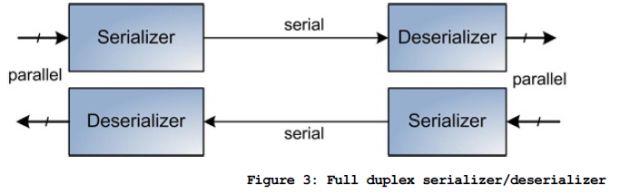

外部串行數據流通常轉換為FPGA內部的并行數據。 這個被稱為SerDes(串行器/解串器)的模塊。 串行器將并行數據并行轉換為串行輸出,速率更高。 相反,解串器將高速串行輸入轉換為并行輸出。 由于執行串行化和反序列化所需的額外步驟,使用SerDes的缺點是額外的通信延遲; 更復雜的初始化和定期的鏈路訓練; 和更大的邏輯大小。

下圖顯示了實現為兩個SerDes模塊的全雙工串行總線。

1.ISERDES

一個專用的串行到并行數據轉換器,以促進高速源同步數據采集。 它具有SDR和DDR數據選項和2到6位數據寬度。

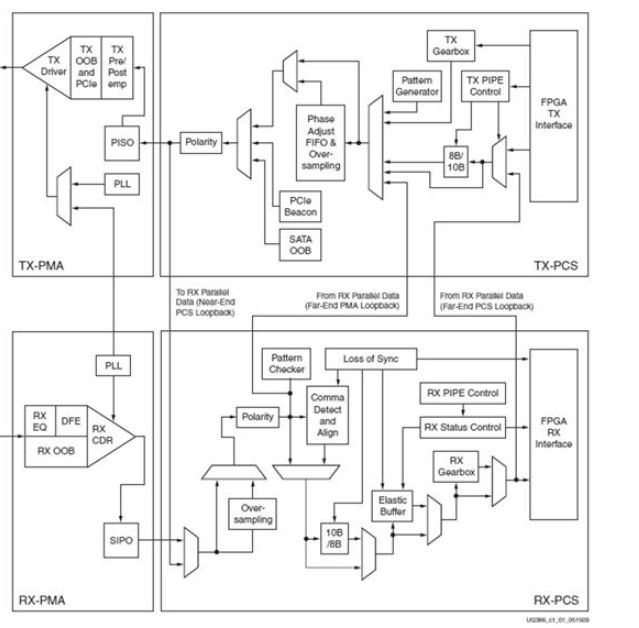

2.GTP/GTX

一些Virtex和Spartan FPGA中的嵌入式收發器模塊。 它是一個復雜的模塊,高度可配置,并與FPGA邏輯資源緊密集成。

下圖顯示了Virtex-6 GTX收發器的框圖。

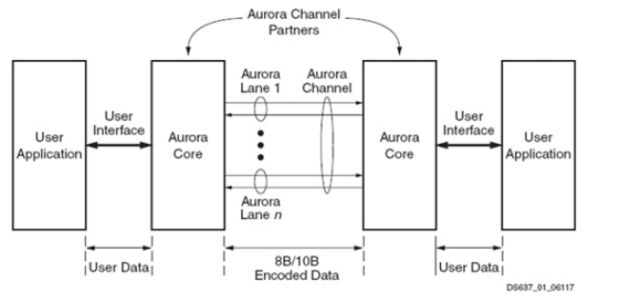

3.Aurora

Aurora 是一個很高效的低延遲點對點的串行協議,它使用了GTP收發器。它旨在隱藏GTP的接口細節和開銷。Xilinx 提供一個擁有執行aurora協議的用戶友好接口的ip核。核心提供的功能包括不同數量的GTP通道,單工和雙工操作,流量控制,可配置線路速率和用戶時鐘頻率。

下圖展示了使用了aurora核的點對點通信。

-

FPGA

+關注

關注

1630文章

21769瀏覽量

604657 -

Xilinx

+關注

關注

71文章

2168瀏覽量

121779 -

無線通信

+關注

關注

58文章

4587瀏覽量

143688

原文標題:FPGA的外部總線接口設計

文章出處:【微信號:gh_873435264fd4,微信公眾號:FPGA技術聯盟】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

豐田、Aurora及大陸集團攜手NVIDIA,共推高度自動駕駛車型

豐田、Aurora和大陸集團加入NVIDIA合作伙伴行列

思嵐科技SLAMTEC Aurora在智能割草機器人中的應用

全志T113雙核異構處理器的使用基于Tina Linux5.0——異構雙核通信驗證

【米爾-Xilinx XC7A100T FPGA開發板試用】+04.SFP之Aurora測試(zmj)

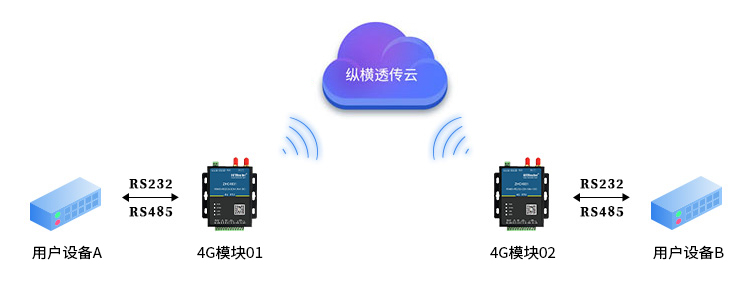

如何讓兩個設備通過4G進行點對點數據映射

TI基于Concerto雙核MCU的PRIME電力線通信數據集中器方案應用說明

NFC點對點模式傳輸

STM32MP157D-DK1使用Ubuntu鏡像作為開發板的內核鏡像應該怎么移植,移植完Ubuntu后還可以使用核間通信嗎?

4G數傳終端-RS485點對點無線對傳通信實踐

使用aurora核的點對點通信應用設計

使用aurora核的點對點通信應用設計

評論