Verilog語法--位選擇運算(+: 和 -:)

verilog語法中使用以下兩個運算符可以簡化我們的位選擇代碼

+:

-:

這兩個的用法如下

wire[7:0]a; a[base_addr+:width] a[base_addr-:width]

其中base_addr指的是起始選擇位,width指的是選擇的位寬

比如以下使用說明

wire[31:0]a; a[0+:8]等價于a[7:0] a[0+:16]等價于a[15:0] a[16+:8]等價于a[23:16] a[7-:8]等價于a[7:0] a[15-:16]等價于a[15:0] a[15-:2]等價于a[15:14]

這樣寫有什么好處呢,比如下面兩個使用場景

假設有一個128bit的數據,怎么方便的將其分割為16個8bit的數據

對一個32比特的數據進行按字節的大小端翻轉

問題一

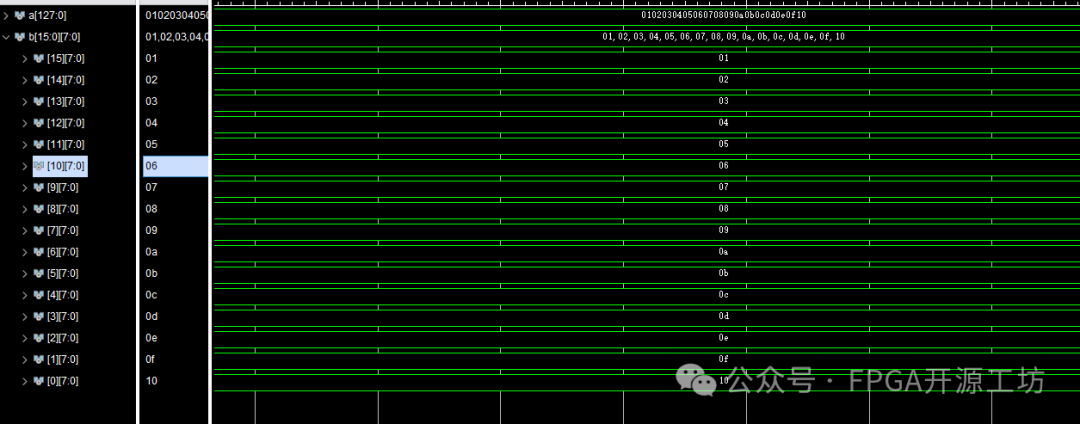

假設有一個128bit的數據,怎么方便的將其分割為16個8bit的數據

如果要解決上面的問題,我們可以直接手動的進行位選擇,代碼如下:

`timescale1ns/1ps moduletb( ); wire[127:0]a; wire[7:0]b[15:0]; assigna={8'd1,8'd2,8'd3,8'd4,8'd5,8'd6,8'd7,8'd8,8'd9,8'd10,8'd11,8'd12,8'd13,8'd14,8'd15,8'd16}; assignb[0]=[7:0]; assignb[1]=[15:8]; assignb[2]=[23:16]; assignb[3]=[31:24]; assignb[4]=[39:32]; assignb[5]=[47:40]; assignb[6]=[55:48]; assignb[7]=[63:56]; assignb[8]=[71:64]; assignb[9]=[79:72]; assignb[10]=[87:80]; assignb[11]=[95:88]; assignb[12]=[103:96]; assignb[13]=[111:104]; assignb[14]=[119:112]; assignb[15]=[127:120]; endmodule

為了方便觀察,我們將a的值賦值為1到16的特殊值,下面b里面的每一個元素都從a里面進行截取,如果bit數比較少的話,可以按上述代碼這樣完成,但是這個代碼看著也很啰嗦,所以可以按照下面的代碼進行改進

`timescale1ns/1ps

moduletb(

);

wire[127:0]a;

wire[7:0]b[15:0];

genvari;

assigna={8'd1,8'd2,8'd3,8'd4,8'd5,8'd6,8'd7,8'd8,8'd9,8'd10,8'd11,8'd12,8'd13,8'd14,8'd15,8'd16};

generate

for(i=0;i

可以看到使用位選擇加for循環的方式會很方便,以后即使位寬改變了,也僅僅只是在for循環這邊改一下就好

問題二

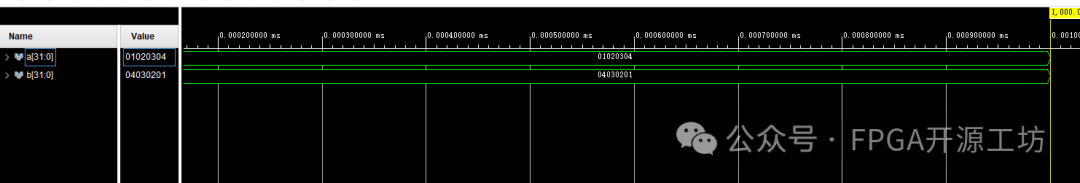

對一個32比特的數據進行按字節的大小端翻轉

最直接的代碼可以按下面這樣寫

`timescale1ns/1ps

moduletb(

);

wire[31:0]a;

wire[31:0]b;

assigna={8'd1,8'd2,8'd3,8'd4};

assignb={a[7:0],a[8:15],a[23:16],a[31:24]};

endmodule

當位寬比較小的時候可以按上面的方式進行,如果位寬比較大的話,上面的這種方法就顯得很冗余了,我們就可以使用位選擇的方式來進行賦值

`timescale1ns/1ps

moduletb(

);

wire[31:0]a;

wire[31:0]b;

genvari;

assigna={8'd1,8'd2,8'd3,8'd4};

generate

for(i=0;i

可以看到正確的完成了我們的需求

-

Verilog

+關注

關注

28文章

1351瀏覽量

110095 -

代碼

+關注

關注

30文章

4788瀏覽量

68603 -

語法

+關注

關注

0文章

44瀏覽量

9810 -

運算符

+關注

關注

0文章

172瀏覽量

11083

原文標題:Verilog語法--位選擇運算(+: 和 -:)

文章出處:【微信號:FPGA開源工坊,微信公眾號:FPGA開源工坊】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

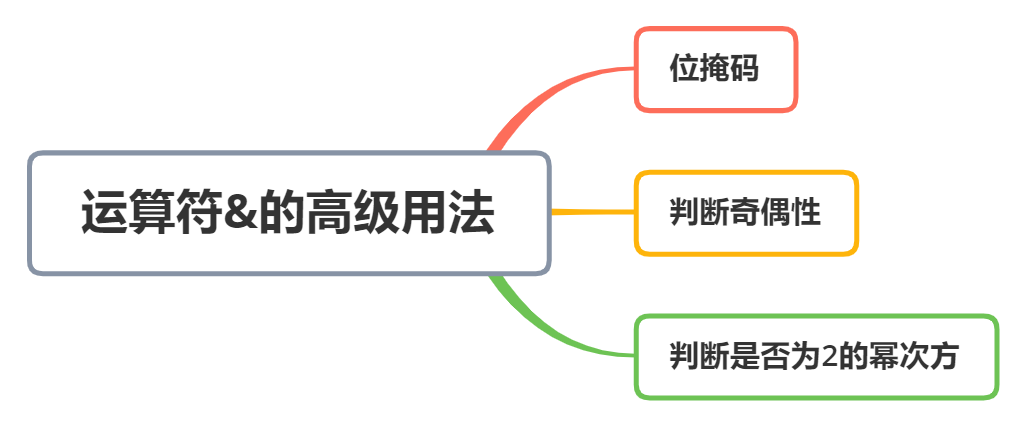

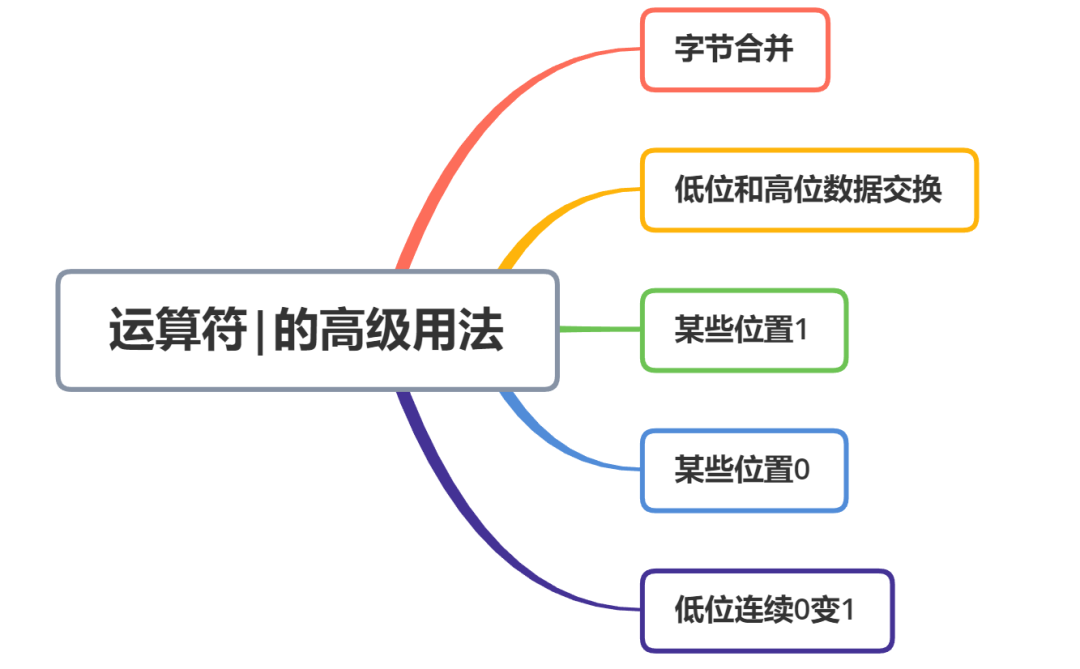

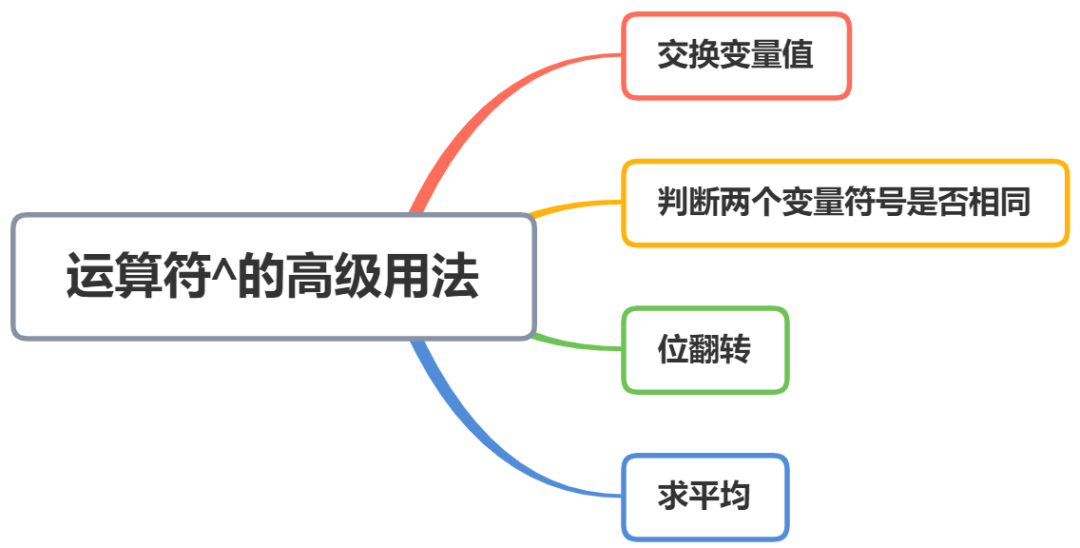

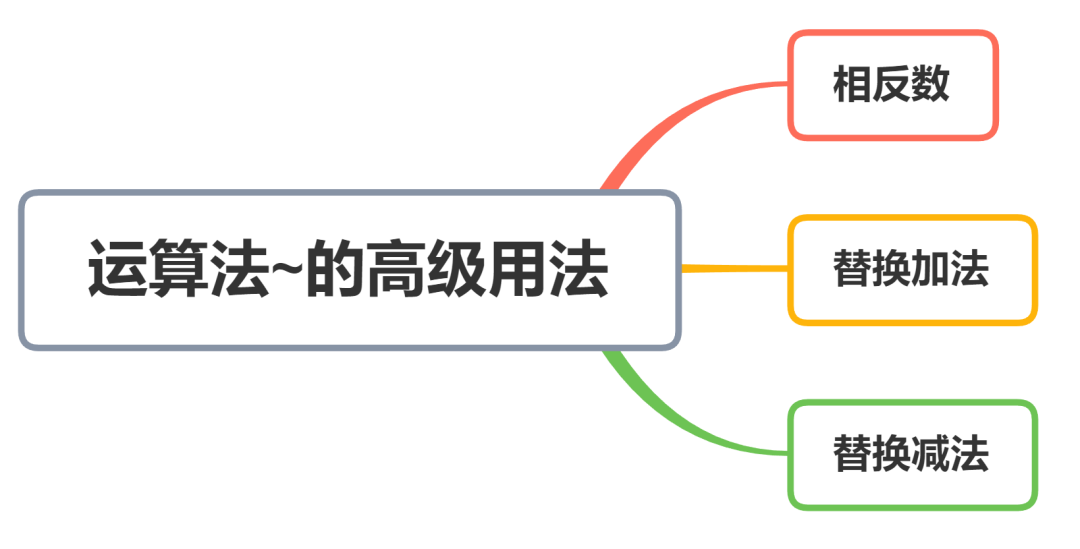

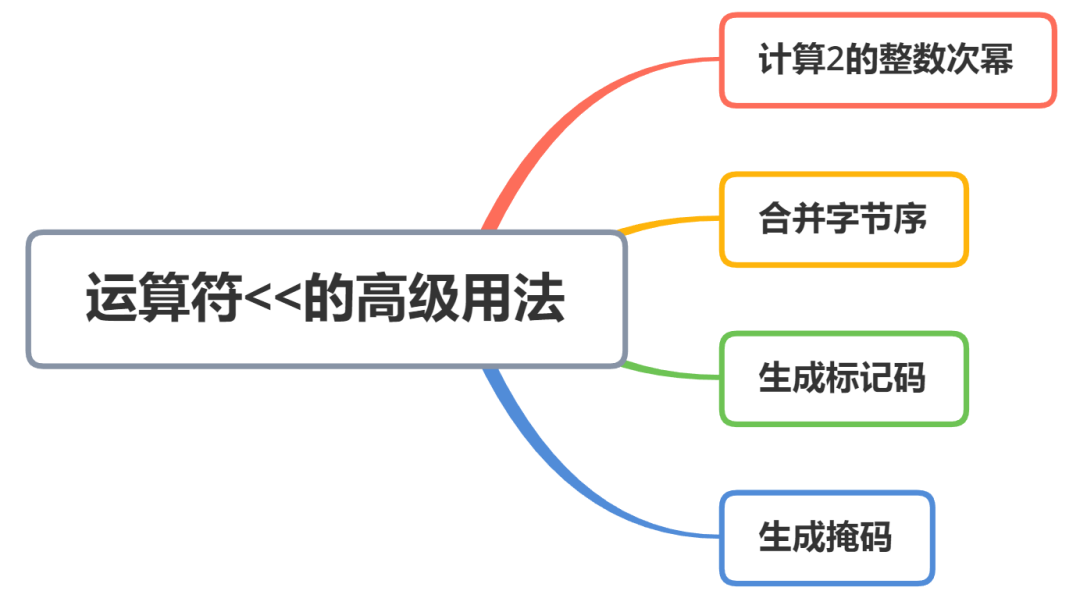

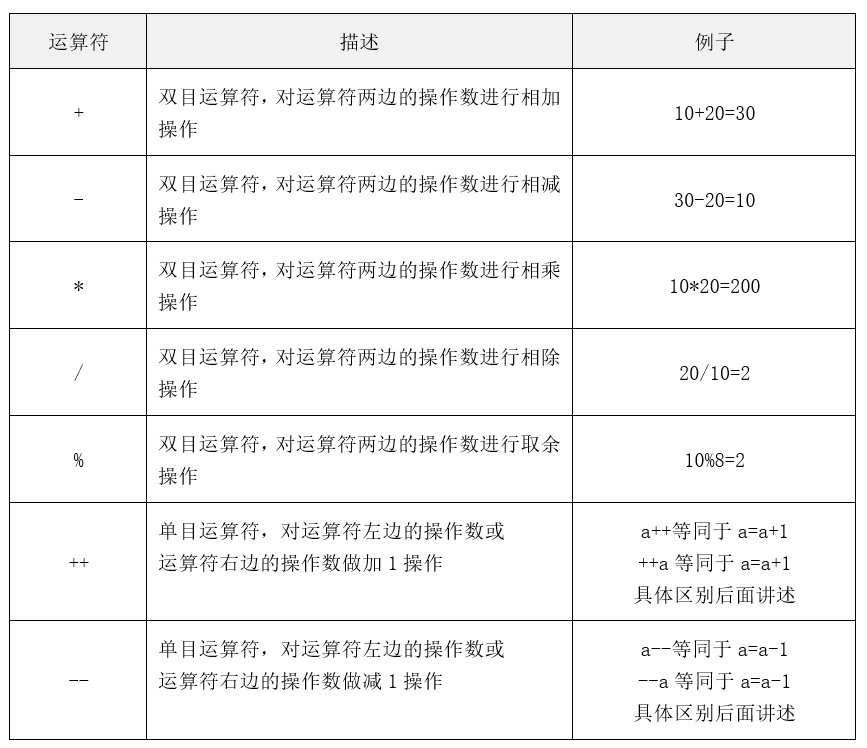

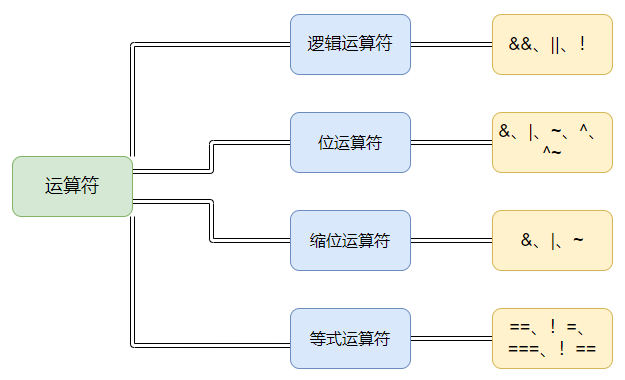

Verilog語法中運算符的用法

Verilog語法中運算符的用法

評論