本文首發于公眾號 FPGA開源工坊

FIFO是FPGA/IC設計中經常使用到的模塊,它經常被用在兩個模塊之間進行數據的緩存,以避免數據在傳輸過程中丟失。同時FIFO也經常被用在跨時鐘域處理中。

FIFO深度的計算是FPGA和IC筆面試中經常被問到的一個問題,在這篇文章里面我們就來討論一下FIFO的深度應該怎么計算。

FIFO的深度如果設置的小了就會有丟數的風險,設置的大了會有資源的浪費。

在討論如何計算FIFO的深度之前,應該先明白一個概念,那就是突發傳輸 ,也就是burst。

突發傳輸

為什么要明確突發傳輸的概念呢?我們假設有以下幾種開發場景。

場景一:讀比寫快

假如說一個FIFO在不間斷的向里面寫入數據和讀出數據,并且向FIFO里面寫數據的速度比從FIFO里面讀數據的速度要慢,那么是不是這個FIFO永遠都不會被寫滿了。

場景二:寫比讀快

假如說一個FIFO在不間斷的向里面寫入數據和讀出數據,并且寫入的速度比讀出的速度快,那么是不是意味著這個FIFO的深度無論設置多少都終將會被寫滿。

所以不間斷在對FIFO不間斷的進行讀寫的情形中討論FIFO深度是沒有意義的。

而我們要討論的FIFO深度其實是在突發傳輸中才是有意義的。

突發傳輸:就是說一個又一個的數據包,每一個數據包之間是有間隙的。

每一個數據包的長度叫做burst length 突發長度

FIFO的最小深度就與突發長度,讀寫速率有關系。

計算出來FIFO的深度關鍵就在于計算出來在讀寫突發的這段時間內,有多少數據沒有被讀走,這個數據的多少就是FIFO的最小深度。

計算公式

FIFO的深度可以用下面的公式計算出來

可以看到在上述公式里面的關鍵就是確定burst length。

下面就通過幾個例子來說明burst length的計算。

例子

例一

某大廠的筆試題:

設計同步FIFO,每100個cycle可以寫入80個數據,每10個cycle可以讀出8個數據,FIFO的深度至少為:

A: 16

B: 32

C: 64

D: 72

首先從題目中知道同步FIFO,所以rd_clk和wr_clk是一樣的。

第二每10個cycle中可以讀出8個數據,那么rd_rate就是8/10也就是0.8

現在關鍵就是burst length的計算了。

每100個cycle可以寫入80個數據,那么是不是意味著這80個數據可以在100個cycle的周期的任意時間寫進FIFO里面。那么什么時候是連續寫入數據最多的極端情況呢,這個極端情況就是burst length最大的時候。

這個極端情況就是在連續的200個cycle中,是不是可以寫入160個數據,那么這160個數據背靠背的連續寫入就是極端情況了。

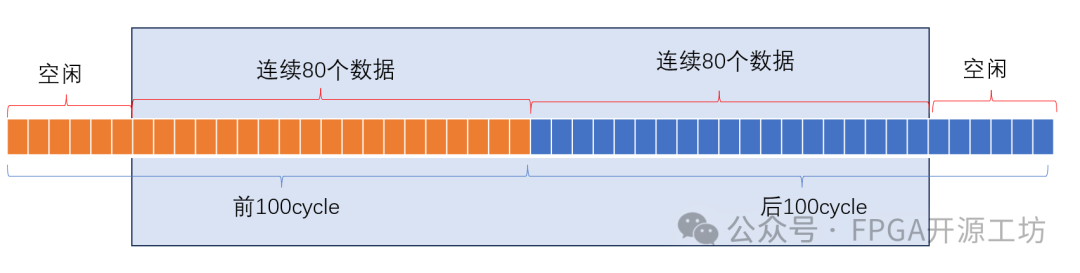

如下圖所示:

在連續兩百個周期內,前20個周期空閑,中間160個時鐘向FIFO寫入數據,最后20個時鐘再次空閑。

所以burst length就是160

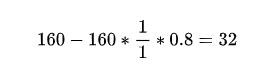

所以FIFO的最小深度為

例二

有一個FIFO設計,輸入時鐘100MHz,輸出時鐘80MHz,輸入數據模式是固定的,其中1000個時鐘中有800個時鐘傳輸連續數據,另外200個空閑,請問為了避免FIFO下溢/上溢,最小深度是多少

A: 320

B: 80

C: 160

D: 200

根據題意wr_clk是100, rd_clk是800。

因為輸入數據的模式是固定的,所以不用考慮背靠背的情況,所以burst length是800

題目中沒有說明在輸出的時候讀使能是否會拉低,所以我們認為FIFO一直在輸出,也就是rd_rate是1

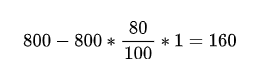

所以FIFO的深度為:

-

FPGA

+關注

關注

1630文章

21769瀏覽量

604638 -

IC設計

+關注

關注

38文章

1298瀏覽量

104126 -

fifo

+關注

關注

3文章

389瀏覽量

43769 -

時鐘域

+關注

關注

0文章

52瀏覽量

9545

原文標題:FPGA|IC筆面試--FIFO深度計算

文章出處:【微信號:FPGA開源工坊,微信公眾號:FPGA開源工坊】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

FPGA學習-總結fifo設計中深度H的計算

求助,FPGA fifo深度不夠怎么辦?

FIFO深度怎么設計

如何計算異步FIFO深度和單獨的時鐘源

如何計算Async Fifo Depth

什么是fifo深度?

談談FIFO閾值的閾值設置及深度計算

【教程】“最惡劣”的FIFO深度計算

LabVIEW FPGA模塊實現FIFO深度設定

基于LabVIEW FPGA模塊程序設計特點的FIFO深度設定詳解

你們知道FIFO最小深度計算嗎

如何簡單快速地計算FIFO的最小深度

FIFO的深度應該怎么計算

FIFO的深度應該怎么計算

評論