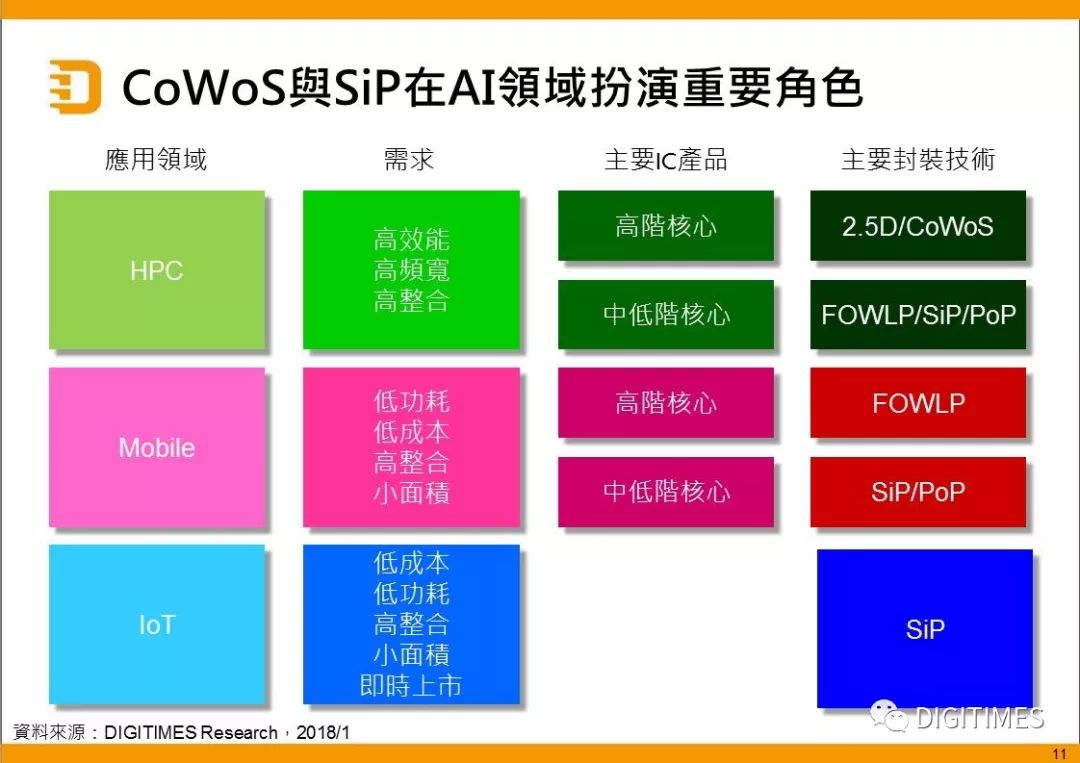

由硬件端來看人工智能架構,涵蓋上游云端(cloud)運算、中游邊緣運算(edge computing),及下游的裝置端(device)。綜合人工智能硬件上中下游所需關鍵芯片進一步分析,對IC制造產業(yè)而言,DIGITIMES Research認為,高效能運算(High Performance Computing;HPC)平臺將成為制程技術研發(fā)的重中之重。

芯片效能的提升,除可透過微縮技術升級與晶體管結構改變等前段技術達成外,后段先進封測技術的導入,亦可以有效提升IC產品效能。其中,臺積電推出2.5D CoWoS(Chip on Wafer on Substrate)制程技術就是導入矽中介層(interposer)材質,并采用矽穿孔(Through Si Via;TSV)技術,透過大幅提高I/O數(shù)的方法提升IC效能,臺積電更于2017年上半年推出采CoWoS技術7納米制程HPC平臺。

除講求效能提升的HPC平臺外,IoT平臺在人工智能的發(fā)展上,也扮演重要角色,物聯(lián)網平臺IC產品以低功耗、低成本、實時上市為主要產品訴求,因此,該平臺IC產品以系統(tǒng)級封裝(System in Package;SiP)為主要封裝技術。

隨人工智能市場興起,IC制造業(yè)者整合前后段技術已成產業(yè)重要趨勢外,DIGITIMES Research認為,為客戶提供一站式服務,IC制造業(yè)者甚至要結合EDA、IP、IC設計服務等業(yè)者,建立完整生態(tài)系統(tǒng)(ecosystem),才有機會在AIoT領域取得致勝先機。(更完整分析請見DIGITIMES Research AI+,IC制造服務「因應高效能與實時上市要求CoWoS與SiP將成人工智能重要封裝技術」研究報告)

-

SiP

+關注

關注

5文章

505瀏覽量

105357 -

AI

+關注

關注

87文章

30979瀏覽量

269253 -

CoWoS

+關注

關注

0文章

139瀏覽量

10498

原文標題:【DIGITIMES Research】CoWoS與SiP成AI芯片重要封裝技術

文章出處:【微信號:gh_44592200c847,微信公眾號:gh_44592200c847】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

CoWoS先進封裝技術介紹

微源半導體LPQ65131芯片在汽車領域的應用

工控主板在工業(yè)控制中扮演什么角色

工業(yè)電腦在智能制造控制領域的應用趨勢分析

Python在AI中的應用實例

RISC-V發(fā)展迅猛,中國扮演重要角色

愛普生差分晶振在光模塊中的重要角色

光電耦合器:航天航空領域的先進連接技術

STM32__UCOSII系統(tǒng)啟動過程中空閑任務和統(tǒng)計任務扮演怎樣的角色?

推拉力測試機在各種工業(yè)應用中,扮演著至關重要的角色

新型電力系統(tǒng)的重要角色:超級電容混合儲能系統(tǒng)

CoWos與SiP在AI領域扮演重要角色

CoWos與SiP在AI領域扮演重要角色

評論