提問(wèn)

能否在 200 ns 內(nèi)開啟或關(guān)閉RF源?

在脈沖雷達(dá)應(yīng)用中,從發(fā)射到接收操作的過(guò)渡期間需要快速開啟/關(guān)閉高功率放大器 (HPA)。典型的轉(zhuǎn)換時(shí)間目標(biāo)可能小于1 μs。傳統(tǒng)上,這是通過(guò)漏極控制來(lái)實(shí)現(xiàn)的。漏極控制需要在28 V至50 V的電壓下切換大電流。已知開關(guān)功率技術(shù)可以勝任這一任務(wù),但會(huì)涉及額外的物理尺寸和電路問(wèn)題。在現(xiàn)代相控陣天線開發(fā)中,雖然要求盡可能低的SWaP(尺寸重量和功耗),但希望消除與HPA漏極開關(guān)相關(guān)的復(fù)雜問(wèn)題。

本文將提出一種獨(dú)特但簡(jiǎn)單的柵極脈沖驅(qū)動(dòng)電路,為快速開關(guān)HPA提供了另一種方法,同時(shí)消除了與漏極開關(guān)有關(guān)的電路。實(shí)測(cè)切換時(shí)間小于200 ns,相對(duì)于 1 μs 的目標(biāo)還有一些裕量。其他特性包括:解決器件間差異的偏置編程能力,保護(hù)HPA免受柵極電壓增加影響的柵極箝位,以及用于優(yōu)化脈沖上升時(shí)間的過(guò)沖補(bǔ)償。

典型漏極脈沖配置

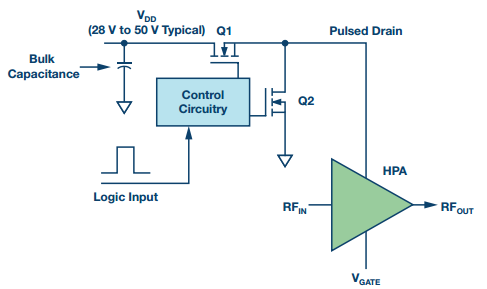

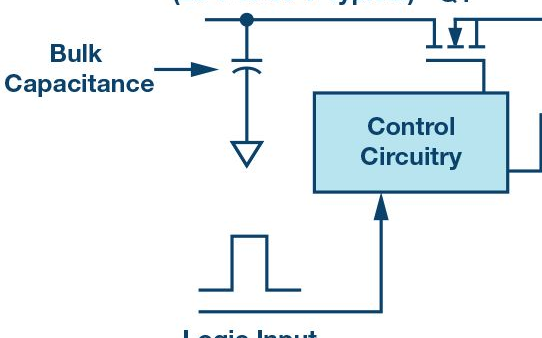

通過(guò)漏極控制開關(guān)HPA的典型配置如圖1所示。一個(gè)串聯(lián)FET開啟輸入HPA的高電壓。控制電路需要將邏輯電平脈沖轉(zhuǎn)換為更高電壓以使串聯(lián)FET導(dǎo)通。

圖1. 傳統(tǒng)HPA脈沖漏極配置

此配置的難點(diǎn)包括:

?大電流的切換要求從大容量電容到HPA漏極引腳的路徑是一條低電感路徑。

?關(guān)閉時(shí),漏極電容保有電荷,需要額外的放電路徑。這是通過(guò)額外的FET Q2來(lái)實(shí)現(xiàn)的,對(duì)控制電路的約束隨之增加:Q1和Q2絕不能同時(shí)使能。

?很多情況下,串聯(lián)FET是N溝道器件。這要求控制電路產(chǎn)生一個(gè)高于HPA漏極電壓的電壓才能開啟。

控制電路的設(shè)計(jì)方法已是眾所周知且行之有效。然而,相控陣系統(tǒng)不斷期望集成封裝并降低SWaP,因此希望消除上述難點(diǎn)。實(shí)際上,人們的愿望是完全消除漏極控制電路。

推薦柵極脈沖電路

柵極驅(qū)動(dòng)電路的目標(biāo)是將邏輯電平信號(hào)轉(zhuǎn)換成合適的GaN HPA柵極控制信號(hào)。需要一個(gè)負(fù)電壓來(lái)設(shè)置適當(dāng)?shù)钠?a href="http://www.xsypw.cn/tags/電流/" target="_blank">電流,以及一個(gè)更大的負(fù)電壓來(lái)關(guān)閉器件。因此,電路應(yīng)接受正邏輯電平輸入并轉(zhuǎn)換為兩個(gè)負(fù)電壓之間的脈沖。電路還需要克服柵極電容影響,提供急速上升時(shí)間,過(guò)沖應(yīng)極小或沒(méi)有。

對(duì)柵極偏置設(shè)置的擔(dān)憂是,偏置電壓的小幅增加可能導(dǎo)致HPA電流的顯著增加。這就增加了一個(gè)目標(biāo),即柵極控制電路應(yīng)非常穩(wěn)定,并有一個(gè)箝位器來(lái)防止受損。另一個(gè)問(wèn)題是,設(shè)置所需漏極電流時(shí),不同器件的最佳偏置電壓有差異。這種差異使得人們更希望有系統(tǒng)內(nèi)可編程?hào)艠O偏置特性。

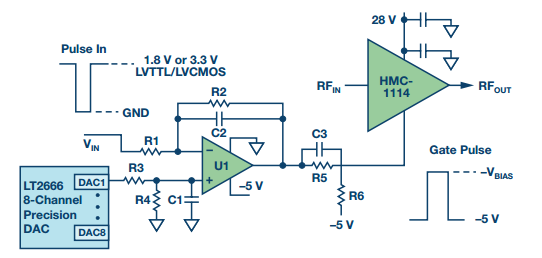

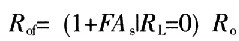

圖2所示電路達(dá)成了所述的全部目標(biāo)。運(yùn)算放大器U1使用反相單負(fù)電源配置。利用一個(gè)精密DAC設(shè)置運(yùn)算放大器基準(zhǔn)電壓,以實(shí)現(xiàn)V+引腳上的增益。當(dāng)邏輯輸入為高電平時(shí),運(yùn)算放大器箝位到負(fù)供電軌。當(dāng)輸入為低電平時(shí),運(yùn)算放大器輸出接近一個(gè)小的負(fù)值,該值由電阻值和DAC設(shè)置決定。反相配置是故意選擇的,目的是當(dāng)邏輯輸入為低電平或接地時(shí)開啟HPA,因?yàn)檫壿嫷碗娖降碾妷翰町愋∮谶壿嫺唠娖健2捎密壍杰夁\(yùn)算放大器,它具有較大壓擺率和足夠的輸出電流驅(qū)動(dòng)能力,適合該應(yīng)用。

圖2. 推薦HPA柵極驅(qū)動(dòng)電路

元件值選擇如下:

◆ R1和R2設(shè)置運(yùn)放增益。

◆ DAC設(shè)置連同R3和R4決定運(yùn)算放大器V+引腳的基準(zhǔn)電壓。C1和R3針對(duì)低通濾波器噪聲而選擇。

◆ R5和R6用于實(shí)現(xiàn)重要的箝位功能。這是因?yàn)檫\(yùn)放的VCC引腳以地為基準(zhǔn),所以這是運(yùn)放輸出的最大值。R5和R6為–5 V電源提供一個(gè)電阻分壓器。

◆ R5的不利影響是由于柵極電容,它會(huì)減慢脈沖響應(yīng)。這要通過(guò)增加C3來(lái)補(bǔ)償,以實(shí)現(xiàn)陡峭的脈沖。

◆ C2的值較小,用以限制運(yùn)放輸出脈沖上升沿的過(guò)沖。

實(shí)測(cè)數(shù)據(jù)

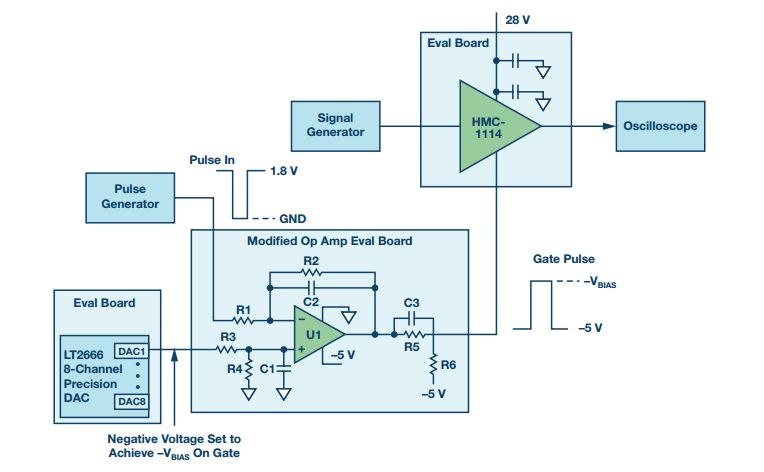

用于驗(yàn)證電路的測(cè)試設(shè)置如圖3所示。對(duì)精密DAC、運(yùn)算放大器和HPA使用評(píng)估板。一個(gè)脈沖發(fā)生器用于模擬1.8 V邏輯信號(hào)。信號(hào)發(fā)生器連續(xù)工作,利用一個(gè)輸入帶寬高于RF頻率的RF采樣示波器測(cè)量HPA對(duì)RF信號(hào)的開啟/關(guān)閉。

圖3. 測(cè)試設(shè)置

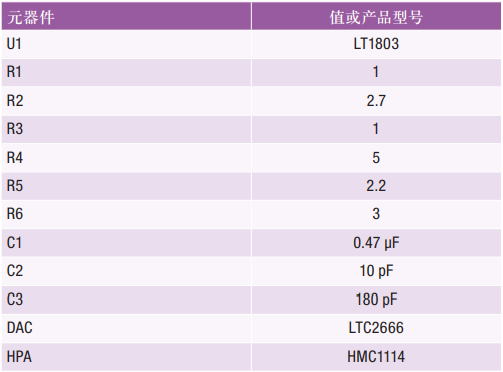

測(cè)試所用的元器件值參見表1。

表1. 所用元器件值

實(shí)測(cè)開啟時(shí)間如圖4所示。時(shí)間標(biāo)度為每格500 ns,RF信號(hào)的上升時(shí)間小于200 ns。對(duì)于測(cè)量從柵極脈沖開始到RF脈沖上升沿結(jié)束的時(shí)間的系統(tǒng),可以看到開啟時(shí)間約為300 ns,這說(shuō)明系統(tǒng)分配1 μs用于發(fā)射到接收轉(zhuǎn)換會(huì)有相當(dāng)可觀的裕量。

圖4. 實(shí)測(cè)HPA開啟時(shí)間

實(shí)測(cè)關(guān)閉時(shí)間如圖5所示。時(shí)間標(biāo)度同樣是每格500 ns,下降時(shí)間明顯快于上升時(shí)間,同樣遠(yuǎn)小于200 ns,說(shuō)明系統(tǒng)分配1 μs用于發(fā)射到接收轉(zhuǎn)換會(huì)有相當(dāng)可觀的裕量。

圖5. 實(shí)測(cè)HPA關(guān)閉時(shí)間

布局考慮

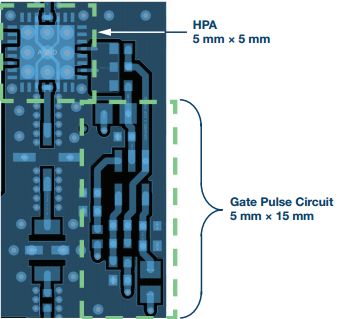

對(duì)一個(gè)代表性布局做了尺寸研究,如圖6所示。柵極脈沖電路的運(yùn)算放大器部分放置在通向HPA輸入的RF路徑附近。精密DAC未顯示出來(lái),假定其放置在控制部分中,為多個(gè)發(fā)射通道提供輸入。布局研究表明,可將該電路添加到實(shí)際的低成本PWB實(shí)現(xiàn)方案中,發(fā)射RF電路所需的額外空間極小。

圖6. 物理尺寸分配

結(jié)語(yǔ)

本文提出了一種獨(dú)特的柵極脈沖電路,并進(jìn)行了HPA快速開/關(guān)評(píng)估。其特性包括:

? 轉(zhuǎn)換時(shí)間小于200 ns。

? 兼容任何邏輯輸入

? 通過(guò)可編程偏置消除器件間差異

? 提供箝位保護(hù)以設(shè)置最大柵極電壓

? 上升時(shí)間/過(guò)沖補(bǔ)償

? 尺寸支持高密度相控陣應(yīng)用

先進(jìn)電子系統(tǒng)集成度不斷提高,要求縮小物理尺寸,因此可以想象,這種電路及其方法的其他變化,將開始在需要快速HPA轉(zhuǎn)換時(shí)間的相控陣應(yīng)用中激增。

-

柵極

+關(guān)注

關(guān)注

1文章

170瀏覽量

20967 -

脈沖電路

+關(guān)注

關(guān)注

3文章

66瀏覽量

35606 -

漏極

+關(guān)注

關(guān)注

0文章

32瀏覽量

10804 -

HPA

+關(guān)注

關(guān)注

1文章

9瀏覽量

8347

原文標(biāo)題:能否在 200 ns 內(nèi)開啟或關(guān)閉RF源?

文章出處:【微信號(hào):analog_devices,微信公眾號(hào):analog_devices】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

一種獨(dú)特但簡(jiǎn)單的柵極脈沖驅(qū)動(dòng)電路

能否在200ns內(nèi)開啟或關(guān)閉RF源?

柵極驅(qū)動(dòng)應(yīng) 支持高功率放大器快速開啟/關(guān)閉

獨(dú)特的柵極驅(qū)動(dòng)應(yīng)用能否在200 ns內(nèi)開啟或關(guān)閉RF源?

DVRFD630-275,開發(fā)板是一種通用電路板,旨在簡(jiǎn)化IXRFD630柵極驅(qū)動(dòng)器的評(píng)估

一種基于DSP的高動(dòng)態(tài)DS FH混合擴(kuò)頻接收機(jī)

一種超寬脈沖發(fā)生器的設(shè)計(jì)

一種測(cè)量微弱信號(hào)的①鎖定放大電路設(shè)計(jì)

一種網(wǎng)絡(luò)安全評(píng)估算法

基于ARM的一種新型BUCK-BOOST電路控制器設(shè)計(jì)

一種給脈沖形成線充電的帶繞式高壓脈沖變壓器

一種用于功率MOSFET的諧振柵極驅(qū)動(dòng)電路

一種可實(shí)現(xiàn)快速響應(yīng)的V/I電路的設(shè)計(jì)方法

獨(dú)特的柵極驅(qū)動(dòng)應(yīng)用可實(shí)現(xiàn)高功率放大器的快速開/關(guān)

一種獨(dú)特的柵極脈沖電路,并進(jìn)行了HPA快速開/關(guān)評(píng)估

一種獨(dú)特的柵極脈沖電路,并進(jìn)行了HPA快速開/關(guān)評(píng)估

評(píng)論