Cadence Allegro系統互連平臺能夠跨集成電路、封裝和PCB協同設計高性能互連。應用平臺的協同設計方法,工程師可以迅速優化I/O緩沖器之間和跨集成電路、封裝和PCB的系統互聯。該方法能避免硬件返工并降低硬件成本和縮短設計周期。約束驅動的Allegro流程包括高級功能用于設計捕捉、信號完整性和物理實現。由于它還得到Cadence Encounter與Virtuoso平臺的支持,Allegro協同設計方法使得高效的設計鏈協同成為現實。

工程師的巨大福利,首款P_C_B分析軟件,點擊免費領取

allegro快速設置柵格點方法

第一步:

新建文檔:xxxxx.txt 寫入代碼:

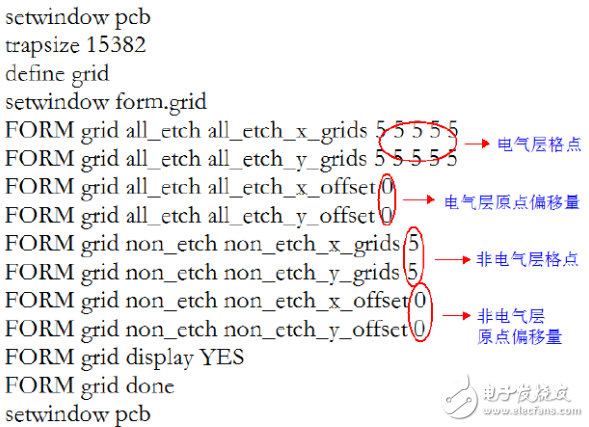

setwindow pcb

trapsize 15382

define grid

setwindow form.grid

FORM grid all_etch all_etch_x_grids 5 5 5 5 5

FORM grid all_etch all_etch_y_grids 5 5 5 5 5

FORM grid all_etch all_etch_x_offset 0

FORM grid all_etch all_etch_y_offset 0

FORM grid non_etch non_etch_x_grids 5

FORM grid non_etch non_etch_y_grids 5

FORM grid non_etch non_etch_x_offset 0

FORM grid non_etch non_etch_y_offset 0

FORM grid display YES

FORM grid done

setwindow pcb

第二步:

將txt文檔保存為邏輯文件:xxxxx.lgc

第三步:

在env文件中寫入調用命令:

alias ~2 replay xxxxx.lgc

第四步:

將xxxxx.lgc文件放入brd文件目錄下

第五步:

按Ctrl+2鍵使用快捷方式實現格點切換

注:

上述格點及切換格點快捷鍵可根據自己習慣任意設置!

-

pcb

+關注

關注

4319文章

23099瀏覽量

397889 -

Cadence

+關注

關注

65文章

921瀏覽量

142137 -

PCB設計

+關注

關注

394文章

4688瀏覽量

85628 -

allegro

+關注

關注

42文章

656瀏覽量

145173 -

可制造性設計

+關注

關注

10文章

2065瀏覽量

15554 -

華秋DFM

+關注

關注

20文章

3494瀏覽量

4521

發布評論請先 登錄

相關推薦

Protel封裝庫轉換到Allegro的方法及步驟

Protel到Allegro格式轉換方法及步驟

Allegro生成鉆孔文件的步驟

DXP設置PCB板中背景柵格的兩種方法

allegro建立焊盤的方法和操作步驟

allegro快速設置柵格點方法步驟介紹

allegro快速設置柵格點方法步驟介紹

評論