Salicide 工藝是指在沒有氧化物覆蓋的襯底硅和多晶硅上形成金屬硅化物,從而得到低阻的有源區和多晶硅。

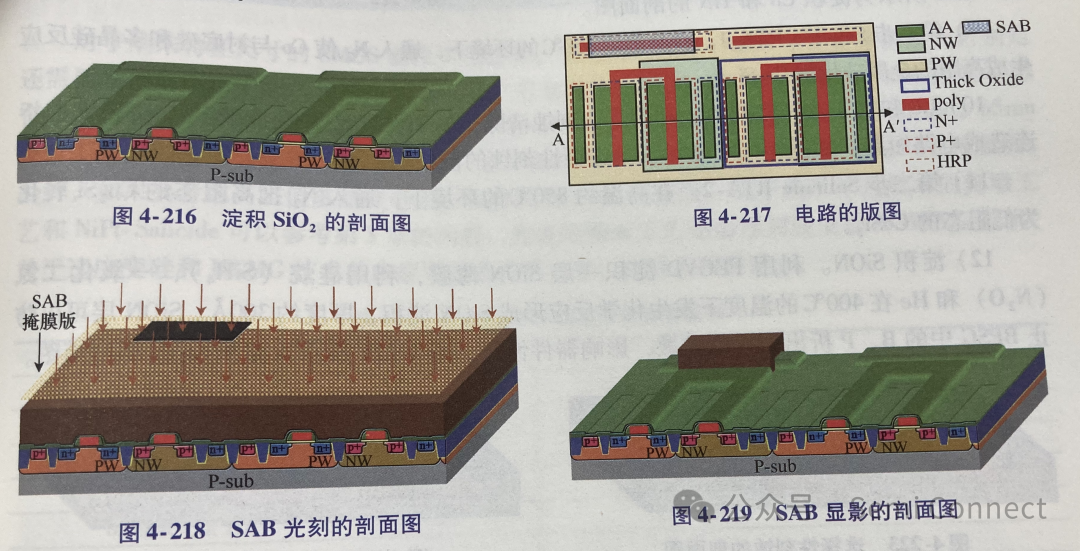

1)淀積 SAB(Salicide Block,金屬硅化物阻擋層)。利用PECVD淀積一層 SiO2,目的是形成 SiO2把不需要形成金屬硅化物(Salicide)的襯底硅和多晶硅覆蓋住,防止形成 Salicide。圖4-216所示為淀積 SiO2的剖面圖。

2) SAB光刻處理。通過微影技術將SAB掩膜版上的圖形轉移到晶圓上,形成SAB 的光刻膠圖案,非SAB區域上保留光刻膠。AA作為SAB光刻曝光對準。圖4-217所示為電路的版圖,工藝的剖面圖是沿 AA'方向,圖4-218所示為SAB 光刻的剖面圖,圖4-219所示為SAB顯影的剖面圖。

3)測量SAB 光刻套刻,收集曝光之后的SAB光刻與 AA的套刻數據。

4)檢查顯影后曝光的圖形。

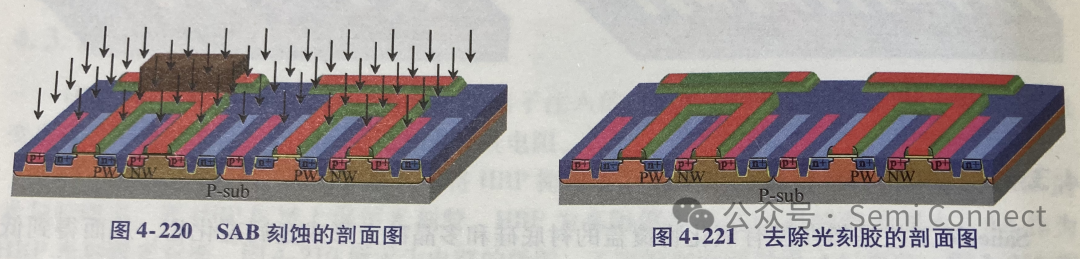

5) SAB 刻蝕處理。干法刻蝕和濕法刻蝕結合,把沒有被光刻膠覆蓋的SiO2清除,裸露出需要形成 Salicide 的襯底硅和多晶硅,為下一步形成 Salicide 做準備。圖4-220所示為SAB刻蝕的剖面圖。

6)去除光刻膠。利用干法刻蝕和濕法刻蝕去除光刻膠。圖4-221 所示為去除光刻膠的剖面圖。

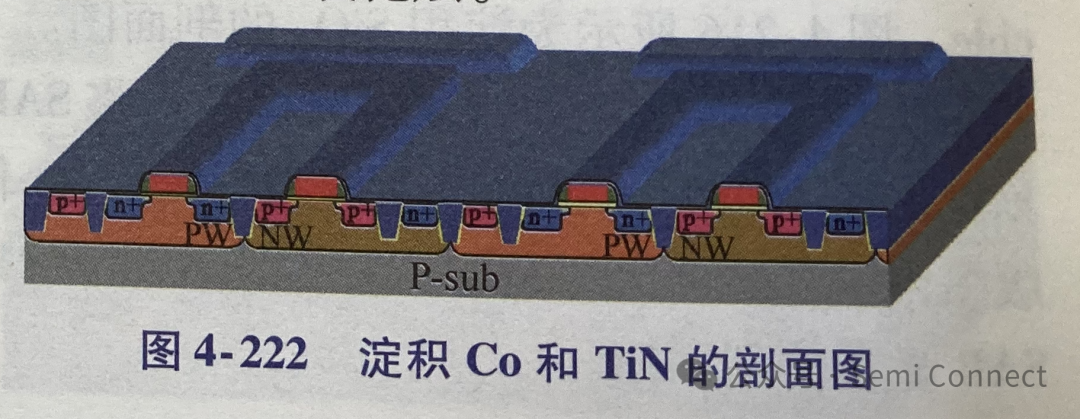

7)清洗自然氧化層。利用化學溶液NH4OH和 HF 清除自然氧化層,因后面一道工藝是淀積Co,把硅表面的氧化物清除的更干凈,使Co跟襯底硅和多晶硅的清清表面接觸,更易的形成金屬硅化物,所以淀積 Co前再過一道酸槽清除自然氧化層。

8)淀積Co和TiN。利用PVD 濺射工藝淀積一層厚度約100A 的Co和厚度約250A 的TiN,TiN的作用是防止Co在 RTA 階段流動導致金屬硅化物厚度不一,電阻值局部不均勻。圖4-222淀積 Co和 TiN 的剖面圖

9)第一步 Salicide RTA-1。在高溫約550°C的環境下,通入N2使Co與襯底硅和多晶硅反應生成高阻的金屬硅化物Co2Si。

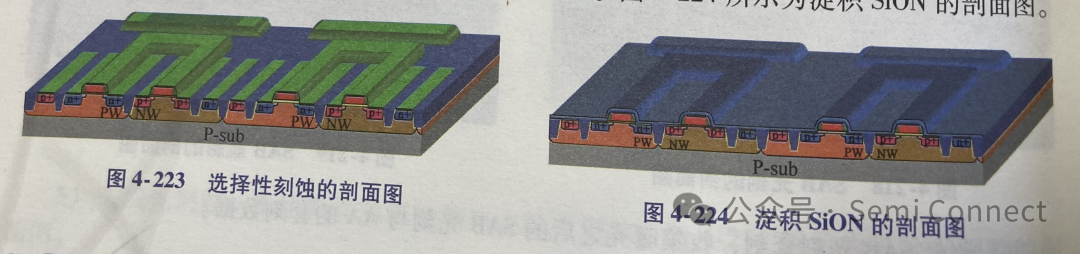

10)Co 和TiN選擇性刻蝕。利用濕法刻蝕清除 TiN 和沒有與Si反應的Co,防止它們橋連造成電路短路。如圖4-223所示,是選擇性刻蝕的剖面圖。

11)第二步 Salicide RTA-2。在高溫約850°C的環境下,通入N2把高阻態的Co2Si轉化為低阻態的CoSi2。

12)淀積 SiON。利用 PECVD淀積一層SiON 薄膜,利用硅烷(SiH4)、一氧化二氮(N2O)和He在400°C的溫度下發生化學反應形成SiON淀積,厚度約300A。SiON 層可以防止 BPSG中的B,P析出向襯底擴散,影響器件性能。圖4-224所示為淀積 SiON的剖面圖。

-

晶圓

+關注

關注

52文章

4912瀏覽量

127994 -

工藝

+關注

關注

4文章

593瀏覽量

28794 -

刻蝕

+關注

關注

2文章

186瀏覽量

13107

原文標題:Salicide 工藝-----《集成電路制造工藝與工程應用》 溫德通 編著

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

雙面柔性PCB板制造工藝及流程

電動汽車電機制造工藝流程圖解

液晶顯示器制造工藝流程基礎技術

雙面印制電路板制造工藝流程

芯片制造工藝流程步驟

MEMS芯片制造工藝流程

闡述電解電容制造工藝流程

Salicide工藝的制造流程

Salicide工藝的制造流程

評論