無論對于芯片設計商還是器件制造商來說,DDR內存可謂是無處不在——除了在服務器、工作站和臺式機中之外,還會內置在消費類電子產品、汽車和其他系統設計中。每一代新的 DDR(雙倍數據速率)SDRAM(同步動態隨機內存)標準都會在許多方面帶來顯著改進,包括速度、尺寸和功率效率。

一、DDR是什么? DDR概述

DDR SDRAM(Double Data Rate Synchronous Dynamic Random Access Memory,雙數據率同步動態隨機存儲器),簡稱為DDR, 簡單的說就是雙倍傳輸速率的SDRAM。普通SDRAM內存的工作方式是在一個時鐘周期的上升沿觸發進行工作。也就是說在一個時鐘周期內,內存將工作一次。而DDR的技術使得內存可以在每一個時鐘周期的上升沿和下降沿分別觸發一次,這樣就使得在一個時鐘周期內內存可以工作兩次,這樣就使得DDR內存在相同的時間內能夠完成普通內存一倍的工作量。

DDR定義里的“同步”是什么意思?

“同步”是指內存工作需要同步時鐘。DDR內部命令的發送與數據傳輸都以它為基準。

DDR的全拼是Double Data Rate SDRAM雙倍數據速率同步動態隨機存取內存, 主要用在電腦的內存。DDR的特點就是走線數量多,速度快,操作復雜,給測試和分析帶來了很大的挑戰。

目前DDR技術已經發展到了DDR5,性能更高,功耗更低,存儲密度更高,芯片容量大幅提升,他的數據速率在3200-6400MT/s。

DDR本質上不需要提高時鐘頻率就能加倍提高SDRAM的速度,它允許在時鐘的上升沿和下降沿讀出數據,因而其速度是標準SDRAM的兩倍,至于地址與控制信號則與傳統SDRAM相同,仍在時鐘上升沿進行數據判斷。

DDR核心技術點就在于雙沿傳輸和預取Prefetch.

DDR的頻率包括核心頻率,時鐘頻率和數據傳輸頻率。核心頻率就是內存的工作頻率;DDR1內存的核心頻率是和時鐘頻率相同的,到了DDR2和DDR3時才有了時鐘頻率的概念,就是將核心頻率通過倍頻技術得到的一個頻率。數據傳輸頻率就是傳輸數據的頻率。

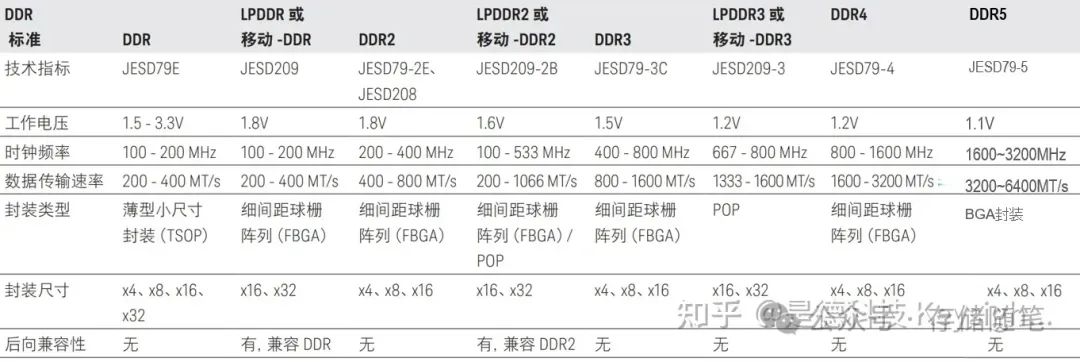

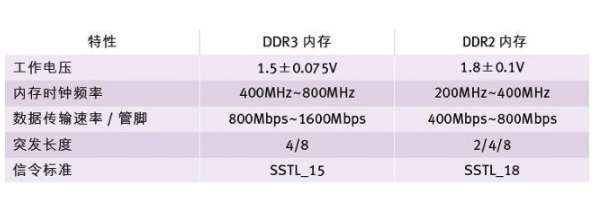

DDR存儲器的身影現在到處可見 — 不僅在服務器、工作站和臺式電腦中使用,還廣泛嵌入在消費電子、汽車和其他系統設計中。每一代 DDR SDRAM(雙倍數據速率同步動態隨機存取存儲器)的推出,都伴隨著速度提升、封裝尺寸減小,以及功耗降低(參見表 1)。這些功能特性方面的改進,也使得設計人員在降低設計裕量、提高信號完整性和互操作性方面面臨更多的挑戰。

表 1 JEDEC 定義了 DDR 規范

DDR內存原理

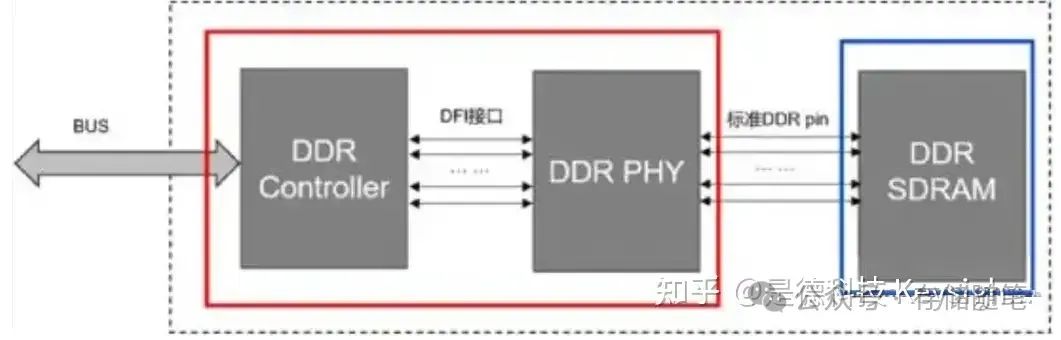

基本DDR subsystem架構圖:DDRC +DDRphy +SDRAM顆粒,DDR IP一般包括DDR Controller和DDR PHY,內部涉及的內容包括但不限于以下幾個方面:數據保序、仲裁、最優調度、協議狀態機設計、防餓死機制、bypass通路、快速切頻、DDR training

DDR工作原理

當時鐘脈沖達到一定頻率時,DDR存儲器才開始工作,此后發生的就是“讀-存-讀”的過程。在此過程中,器件芯片會從主在取數據,然后與入數據在儲區。當寫入操作完成后,再從存儲區中取出數據,並將其傳輸到處理器中,然后根據需要將數據處理,再把最終結果返回到主存。

DDR 的雙倍數據傳輸率其實就是每個時鐘周期內讀寫一次數據,即DDR芯片可以在每個時鐘周期內分別完成“讀-存”和“存-讀”操作,從而提高存儲器的傳輸效率。

DDR內存通過雙倍數據速率的傳輸方式,結合多通道傳輸和數據校驗等技術,提高了數據傳輸效率和可靠性。這使得 DDR 成為了計算機內存的主流技術。

內存芯片 - DDR內存模塊中包含多個內存芯片,每個芯片有自己的存儲單元。每個存儲單元都有一個地址,用于在讀取或寫入數據時進行尋址。

數據總線 - DDR內存模塊連接到計算機的內存控制器,通過數據總線進行數據傳輸。數據總線可以同時傳輸多個數據位,例如 64 位或 128位。

時鐘信號 - DDR內存模塊通過時鐘信號進行同步操作。時鐘信號用來控制數據的傳輸速率,每個時鐘周期內有一個上升沿和一個下降沿。上升沿時,數據從內存芯片傳輸到數據總線;下降沿時,數據從數據總線傳輸到內存芯片。

預充電 - 在開始傳輸數據之前,DDR內存模塊會先進行預充電操作。預充電是將存儲單元中的電荷恢復到初始狀態,以確保接下來的數據傳輸是準確的。

數據傳輸 - DDR 采用了多通道的數據傳輸方式,即同時傳輸多個數據位。這樣可以在每個時鐘周期內傳輸更多的數據。

DDR接口

電子器件工程聯合會(JEDEC)現已針對小功率DDR(LPDDR)或移動設備(移動DDR)推出了全新的 DDR標準。這個標準使用了更低的信號幅度,進一步改善了功耗情況。目前,該標準已經達到了 DDR1 的技術指標。工程師們將無需重新設計器件的鏈路層或協議層,便可享受功耗降低帶來的種種優勢,因為只需很少的投資便能調整系統的電壓電平。

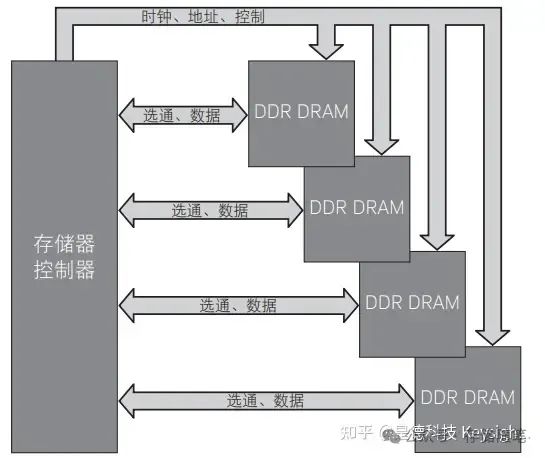

DDR接口可傳輸控制、地址、時鐘、選通和數據信號。如圖 1 所示,時鐘、地址和控制信號從存儲器控制器單向傳輸到 DDR芯片;選通和數據信號為雙向傳輸。在讀取操作中,選通和數據信號從DDR芯片傳輸到存儲器控制器。在寫入操作中,信號沿相反方向傳輸。隨著數據傳輸速率的增加和信號幅度的降低,為了提高信號性能,時鐘和選通信號采用差分信號,這樣可以消除共模噪聲。其他信號仍然在單端模式下操作,更容易受到噪聲、串擾和干擾的影響。

存儲器分類

存儲器分為內部存儲器(內存),外部存儲器(外存),緩沖存儲器(緩存)以及閃存這幾個大類。

內存也稱為主存儲器,位于系統主機板上,可以同CPU直接進行信息交換。其主要特點是:運行速度快,容量小。

外存也稱為輔助存儲器,不能與CPU之間直接進行信息交換。其主要特點是:存取速度相對內存要慢得多,存儲容量大。

內存與外存本質區別是,一個是內部運行提供緩存和處理的功能,也可以理解為協同處理的通道;而外存主要是針對儲存文件、圖片、視頻、文字等信息的載體,也可以理解為儲存空間。緩存就是數據交換的緩沖區 (稱作Cache),當某一硬件要讀取數據時,會首先從緩存中查找需要的數據,如果找到了則直接執行,找不到的話則從內存中找。由于緩存的運行速度比內存快得多,故緩存的作用就是幫助硬件更快地運行。

閃存 (Flash Memory)是一種長壽命的非易失性的存儲器,數據刪除不是以單個的字節為單位而是以固定的區塊為單位。閃存是電子可擦除只讀存儲器(EEPROM) 的變種,閃存與EEPROM不同的是,EEPROM能在字節水平上進行刪除和重寫而不是整個芯片擦寫,而閃存的大部分芯片需要塊擦除。由于其斷電時仍能保存數據,閃存通常被用來保存設置信息,如在電腦的B1OS(基本程序)、PDA(個人數字助理)、數碼相機中保存資料等。

存儲器主要分為只讀存儲器ROM 和隨機存取存儲器RAM(random access memory)兩大類

ROM:只讀存儲器 - ROM 所存數據,一般是裝入整機前事先寫好的,整機工作過程中只能讀出,ROM所存數據穩定,斷電后所存數據也不會改變。

RAM:隨機存取存儲器 (random access memory) - RAM 是與 CPU 直接交換數據的內部存儲器,它可以隨時讀寫,速度快,通常作為操作系統或其他正在運行中的程序的臨時數據存儲媒介,當電源關閉時 RAM 不能保留數據。

DDR SDRAM 在系統時鐘的上升沿和下降沿都可以進行數據傳輸 - DDR SDRAM在 SDRAM 的基礎上發展而來,這種改進型的 DRAM和 SDRAM 是基本一樣的,不同之處在于它可以在一個時鐘讀寫兩次數據,這樣就使得數據傳輸速度加倍了,也是目前電腦中用得最多的內存,而且具有成本優勢。DDR 已經發展至今已經進化到 DDR5,與 DDR4相比,DDR5 在強大的封裝中帶來了全新的架構。

如何計算DDR帶寬?

內存帶寬計算公式1:

帶寬=內存核心頻率×倍增系數×(內存總線位數/8)

內存帶寬計算公式2:

帶寬=標稱頻率×線寬 ÷ 8

SDRAM和DDR區別是什么?

DDR=雙倍速率同步動態隨機存儲器,是內存的其中一種。DDR取消了主板與內存兩個存儲周期之間的時間間隔,每隔2個時鐘脈沖周期傳輸一次數據,大大地縮短了存取時間,使存取速度提高百分之三十。

SDRAM是 "Synchronous Dynamic random access memory”的縮寫,意思是“同步動態隨機存儲器”,就是我們平時所說的“同步內存”。從理論上說,SDRAM與CPU頻率同步,共享一個時鐘周期。SDRAM內含兩個交錯的存儲陣列,當CPU從一個存儲陣列訪問數據的同時,另一個已準備好讀寫數據,通過兩個存儲陣列的緊密切換,讀取效率得到成倍提高。

通常DRAM是有一個異步接口的,這樣它可以隨時響應控制輸入的變化。而SDRAM有一個同步接口,在響應控制輸入前會等待一個時鐘信號,這樣就能和計算機的系統總線同步。時鐘被用來驅動一個有限狀態機,對進入的指令進行管線操作。這使得SDRAM與沒有同步接口的異步DRAM(asynchronous DRAM)相比,可以有一個更復雜的操作模式。

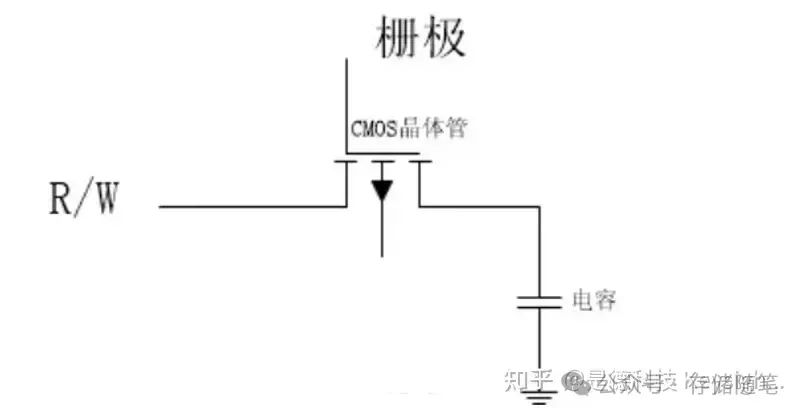

DRAM單元(cell)

DDR SDRAM,是一種雙數據速率(DDR)同步動態隨機存取存儲器(SDRAM)。DDR是SDRAM的更新換代產品,采用5伏工作電壓,允許在時鐘脈沖的上升沿和下降沿傳輸數據,這樣不需要提高時鐘的頻率就能加倍提高SDRAM的速度,并具有比SDRAM多一倍的傳輸速率和內存帶寬。

作為現代數字系統里最重要的核心部件之一,應用十分廣泛。從消費類電子到商業工業類設備,從終端產品到數據中心,用于CPU進行數據處理運算的緩存。近20多年來,經歷了從SDRAM發展到DDR RAM,又從DDR發展到目前的DDR5,每一代 DDR 技術在帶寬、性能和功耗等各個方面都實現了顯著的進步,極大地推動了計算性能的提升。

二 DDR標準發展和DDR5簡介

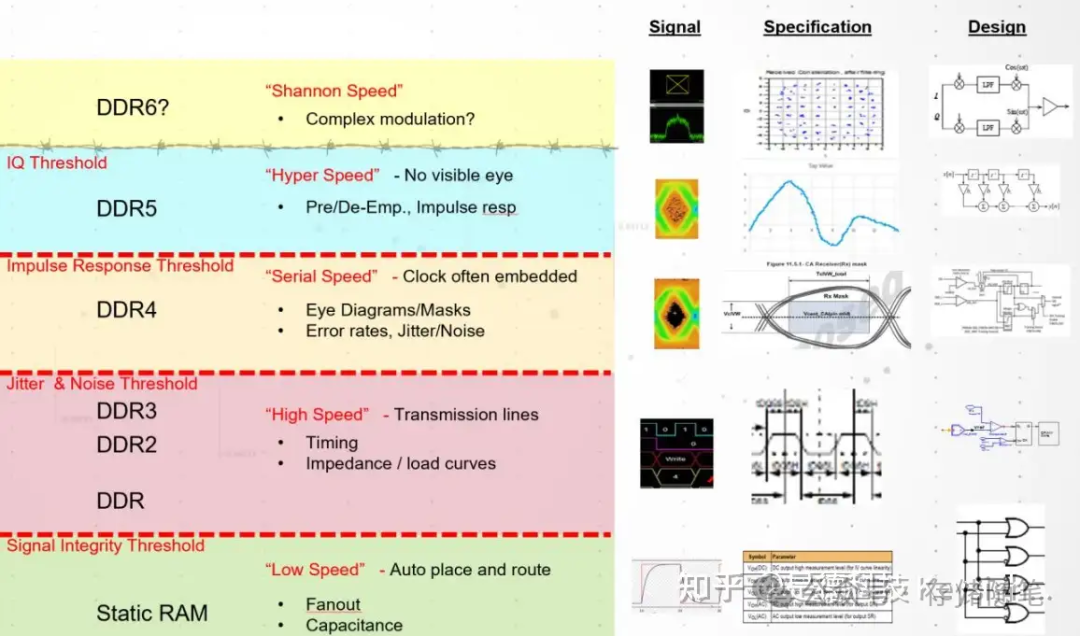

圖1展示的是RAM(Random Access Memory)20多年來的發展歷程和信號特點。在SRAM時代,由于較低的信號速率,我們更多關心的是信號的扇出以及走線所帶來的容性負載。在DDR1/2/3時代,信號速率的不斷提升,傳統的使用集總參數方式來進行電路分析已越發顯得不足,我們更關心的是信號的建立保持時間,以及信號線之間的延遲skew。來到DDR4時代,有限帶寬的PCB、連接器等傳輸通道,把原始信號里的高頻分量削弱或者完全去掉,使得信號在時域波形上的表現為邊沿變緩、出現振鈴或者過沖。我們要像分析傳統串行數據那樣去更加關心數據的眼圖,接收端模板和誤碼率。隨著AI、機器學習以及5G的發展,以往的DDR4技術,開始顯得力不從心。如今DDR5的第5代高速I/O數據傳輸開始大規模走向市場化。

2.1 DDR5和DDR4性能差別 - DDR5的新特性

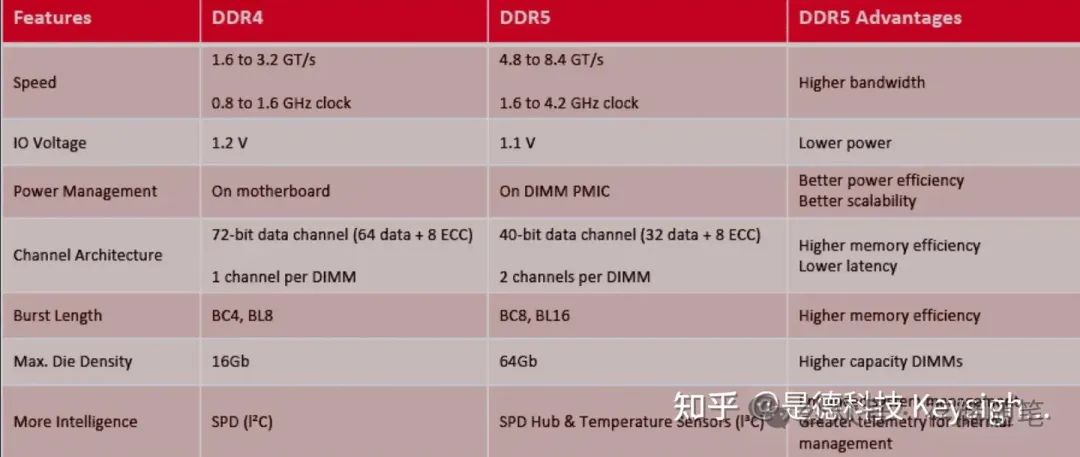

如下表所示,DDR5相比DDR4而言,帶來了一系列關鍵的性能提升,同時也帶來了新的設計挑戰。

表1 DDR4和DDR5比較(源自Rambus)

2.1.1 速率的提升

近年來,內存與CPU性能發展之間的剪刀差越來越大,對內存帶寬的需求日益迫切。DDR4在1.6GHz的時鐘頻率下最高可達 3.2 GT/s的傳輸速率,最初的 DDR5則將帶寬提高了 50%,達到 4.8 GT/s傳輸速率。DDR5 內存的數據傳輸速率最終將會達到 8.4 GT/s。

2.1.2 電壓的降低

降低工作電壓(VDD),有助于抵消高速運行帶來的功耗增加。在 DDR5 DRAM 中,寄存時鐘驅動器 (RCD) 電壓從 1.2 V 降至 1.1 V。命令/地址 (CA) 信號從 SSTL 變為 PODL,其優點是當引腳處于高電平狀態時不會消耗靜態功率。

2.1.3 DIMM 新電源架構

DIMM是什么?

DIMM全稱Dual-Inline-Memory-Modules,中文名叫雙列直插式存儲模塊,是指奔騰CPU推出后出現的新型內存條,它提供了64位的數據通道。

DDR5改善了DIMM的工作電壓,將供電電壓從DDR4的1.2V降至1.1V,從而進一步提升了內存的能效。

使用 DDR5 DIMM 時,電源管理將從主板轉移到 DIMM 本身。DDR5 DIMM 將在 DIMM 上安裝一個 12 V 電源管理集成電路(PMIC),使系統電源負載的顆粒度更細。PMIC 分配1.1 V VDD 電源,通過更好地在 DIMM 上控制電源,有助于改善信號完整性和噪音。

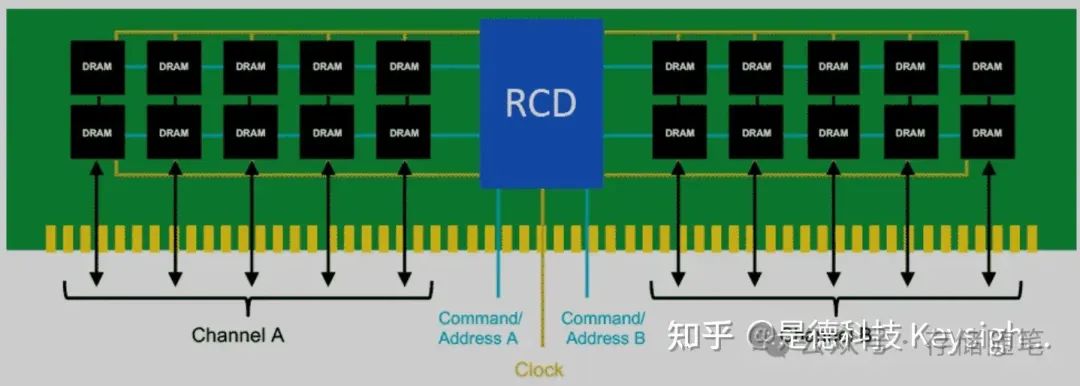

2.1.4 DIMM通道架構

DDR4 DIMM 具有 72 位總線,由 64 個數據位和 8 個 ECC 位組成。在 DDR5 中,每個 DIMM 都有兩個通道。每個通道寬 40 位,32 個數據位和 8 個 ECC 位。雖然數據寬度相同(共 64 位),但兩個較小的獨立通道提高了內存訪問效率。因此,使用 DDR5 不僅能提高速度,還能通過更高的效率放大更高的傳輸速率。

2.1.5 更長的突發長度

DDR4 的突發長度為4或者8。對于 DDR5,突發長度將擴展到8和16,以增加突發有效載荷。突發長度為16(BL16),允許單個突發訪問 64 字節的數據,這是典型的 CPU 高速緩存行大小。它只需使用兩個獨立通道中的一個通道即可實現這一功能。這極大地提高了并發性,并且通過兩個通道提高了內存效率。

2.1.6 更大容量的 DRAM

DDR4 在單芯片封裝(SDP)中的最大容量為16 Gb DRAM。而DDR5的單芯片封裝最大容量可達64 Gb,組建的DIMM 容量則翻了兩番,達到驚人的 256 GB。

2.2 DDR5 設計面臨的挑戰

2.2.1 采用分離式全速率時鐘,對應6400M T/s頻率的時鐘速率高達3.2GHz(未來會支持到8400M T/s)。

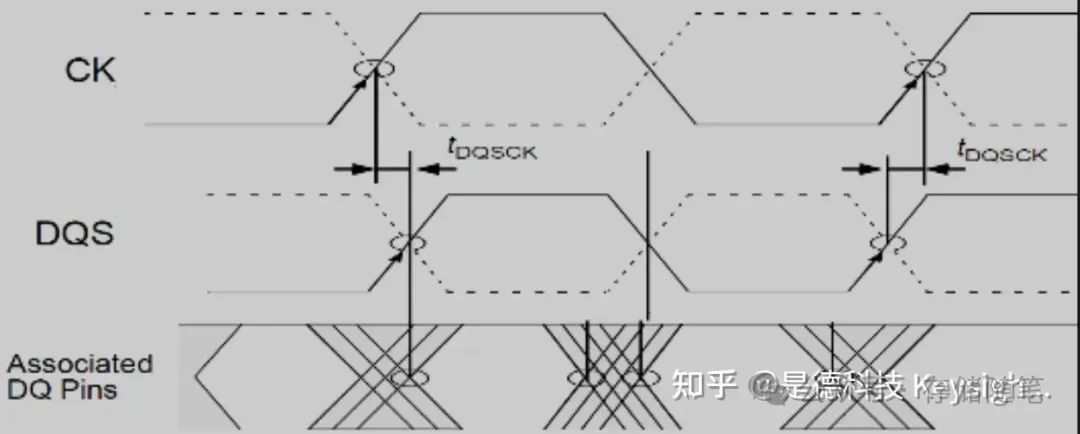

DDR5 DQS控制DQ讀寫時序

時鐘控制命令信號,選通信號控制數據。對時鐘信號抖動的要求更加嚴格,對各種命令信號與數據和地址信號的時序要求也更高。

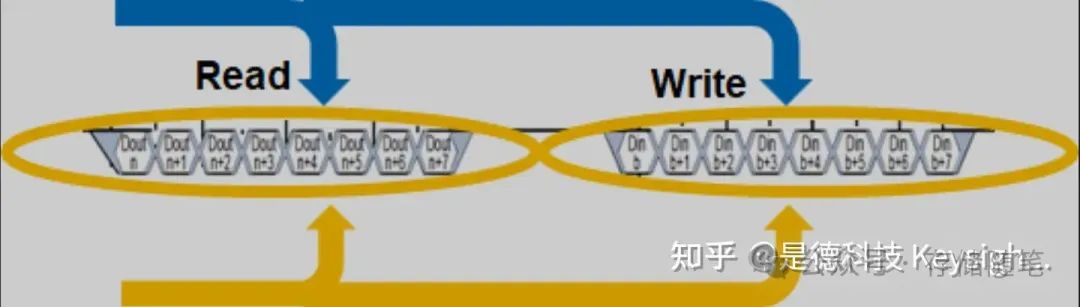

2.2.2 雙向復用的數據總線,讀寫數據分時復用鏈路。

由于有限的鏈路通道和布板空間等資源讀寫操作繼續采用共享總線,因此需要分時操作。從驗證測試角度來看也需要分別對讀和寫信號進行分離以檢查其是否滿足規范。

DDR5讀寫共享總線

2.2.3 突發DQS和DQ信號在更高速率的背景下在有限帶寬的鏈路傳輸時帶來更多ISI效應問題。

在DQS讀寫前導位,突發的第一個bit等等均有不同的效應和表現。此外考慮到存儲電路在設計上不同于串行電路存在較多的阻抗不匹配,因此反射問題或干擾帶來的ISI也會更嚴重。

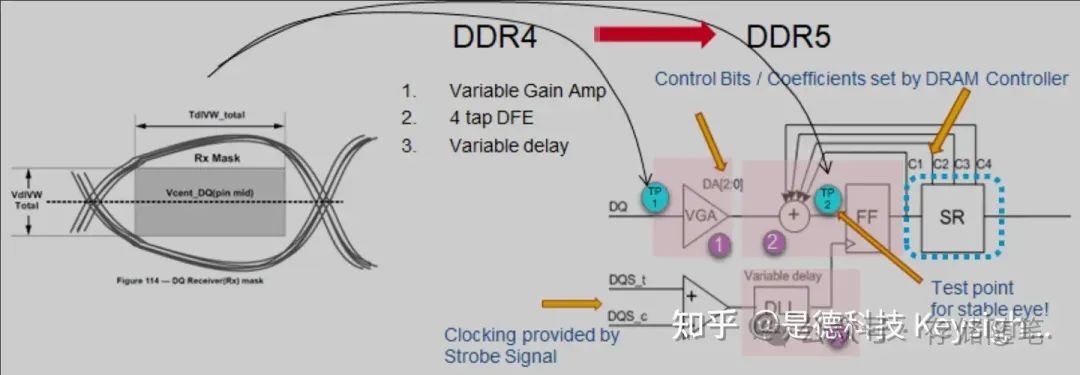

DDR5在接收端采用更多的類似高速串行總線的信號處理

因此在接收側速率大于3600MT/s時采用類似高速串行電路和標準總線中已經成熟的DFE均衡技術,可變增益放大(VGA)則通過MR寄存器配置,以補償在更高速率傳輸時鏈路上的損耗。DDR4標準采用的CTLE作為常用的線性均衡放大,雖然簡單易實現但是其放大噪聲的副產品也更為常見,考慮到DDR5總線里的反射噪聲比沒有采用。另外考慮到并行總線的串擾和反射等各信號抖動的定義和分析也會隨之變化。從測試角度來看,示波器是無法得到TP2點即均衡后的信號的,而僅能得到TP1點的信號,然后通過集成在示波器上的分析軟件里的均衡算法對信號進行均衡處理以得到張開的眼圖。眼圖分析的參考時鐘則來自基于時鐘信號的DQS信號。另外眼圖測試也從以往僅對DQ進行擴展到包括CMD/ADDR總線。

-

DDR

+關注

關注

11文章

712瀏覽量

65419 -

內存

+關注

關注

8文章

3040瀏覽量

74171

原文標題:一文讀懂DDR內存基礎知識|值得收藏

文章出處:【微信號:Rocker-IC,微信公眾號:路科驗證】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

一文讀懂DDR內存基礎知識

一文讀懂DDR內存基礎知識

評論