據麥姆斯咨詢報道,法國研究機構CEA-Leti開發出了一種結合混合鍵合和高密度硅通孔(TSV)的新工藝,可用于在CMOS圖像傳感器(CIS)中嵌入人工智能(AI)。

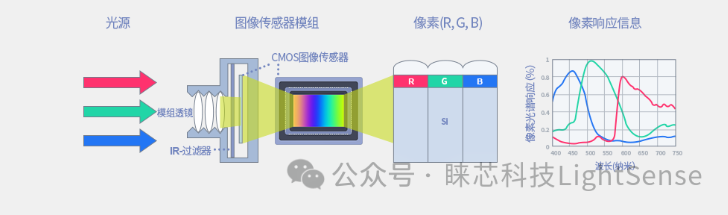

將人工智能整合到新一代CMOS圖像傳感器中,可以利用所有成像數據感知場景、了解環境狀況并進行干預。

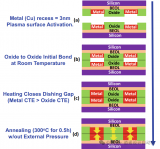

CEA-Leti開發了一種三層測試版芯片,具有兩個嵌入式銅-銅混合鍵合界面(F2F和F2B),其中一片晶圓包含高密度TSV。

CEA-Leti在美國丹佛舉行的ECTC 2024會議上展示了該技術的一些細節,該成果基于之前三片300毫米硅晶圓堆疊的研究基礎。

由于智能手機、數碼相機、汽車和醫療器械等具有高性能成像能力,因此對智能CMOS圖像傳感器的需求正在迅速成長。這種通過嵌入式人工智能提高成像質量和功能的需求,為終端設備制造商在不增加器件尺寸的情況下提高圖像傳感器性能提出了挑戰。

CEA-Leti研究員Renan Bouis說:“通過堆疊多個芯片來構建三維架構(如三層堆疊式圖像傳感器),引領了圖像傳感器設計范式的轉變。”

他說:“不同層級之間的電氣連通需要先進的互連技術,而混合鍵合技術憑借其微米甚至亞微米級非常精細的間距,可以滿足這一要求。”

高密度硅通孔具有相近的密度,能夠通過中間層進行信號傳輸。這兩種技術都有助于減少布線長度,而這正是提高三維堆疊架構性能的關鍵。

CEA-Leti項目經理兼IRT Nanoelec智能圖像傳感器項目主任Eric Ollier說:“該研究成果介紹了制造三維多層智能圖像傳感器所必須的關鍵技術,進而滿足需要嵌入式人工智能的新應用。”CEA-Leti研究所是IRT Nanoelec的主要合作伙伴。

研究員Stéphane Nicolas說:“在CMOS圖像傳感器中結合混合鍵合和高密度硅通孔,有利于圖像傳感器陣列、信號處理電路和存儲元件等各種元件的集成,實現無與倫比的精度和緊湊性。”

CEA-Leti制造的測試版芯片代表了一項重要里程碑,因為它既證明了每個技術模塊的可行性,也證明了集成工藝流程的可行性。他說:“該成果為展示功能齊全的三層堆疊式智能CMOS圖像傳感器奠定了基礎,其邊緣人工智能技術能夠解決高性能語義分割和物體檢測應用。”

去年,CEA-Leti的科學家們報道了一款雙層堆疊式測試版芯片,結合了高10微米、直徑1微米的高密度硅通孔和高度可控的混合接合技術,兩者均以F2B配置組裝。最近的這項研究成果又將高密度硅通孔縮短到6微米高,進而開發出一種不僅具有低分散電氣性能,還能簡化制造過程的雙層堆疊式測試版芯片。

研究員Stéphan Borel說:“與1微米 x 10微米高密度硅通孔相比,我們的1微米 x 6微米高密度硅通孔具有更好的電阻和隔離性能,這要歸功于優化的減薄工藝,它使我們能夠以良好的均勻性降低襯底厚度。”

“高度降低使電阻減少了40%,與長度的減少成正比。”他補充說,“同時降低的深寬比增加了隔離襯墊的臺階覆蓋,從而提供了更好的耐壓性。”

“憑借這些成果,CEA-Leti占據了這一新領域的全球領先地位,正致力于為下一代智能CMOS圖像傳感器做好準備。”Ollier說,“邊緣人工智能將提高CMOS圖像傳感器的性能,實現許多新的應用。這些新型三維多層智能圖像傳感器在傳感器端實現了邊緣人工智能,正成為成像領域的真正突破。”

-

CMOS

+關注

關注

58文章

5718瀏覽量

235513 -

圖像傳感器

+關注

關注

68文章

1902瀏覽量

129554 -

人工智能

+關注

關注

1791文章

47279瀏覽量

238511

原文標題:混合鍵合+高密度硅通孔,實現三層堆疊式圖像傳感器嵌入AI

文章出處:【微信號:MEMSensor,微信公眾號:MEMS】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

高密度Interposer封裝設計的SI分析

什么是高密度DDR芯片

mpo高密度光纖配線架解析

FPGA在人工智能中的應用有哪些?

簡單認識CMOS圖像傳感器

高密度光纖配線架怎么安裝

TIDA-010083-適用于機器視覺攝像機和視覺傳感器的高密度隔離式PoE 和 GigE PCB layout 設計

混合鍵合+高密度硅通孔,可用于在CMOS圖像傳感器中嵌入人工智能

混合鍵合+高密度硅通孔,可用于在CMOS圖像傳感器中嵌入人工智能

評論