1.開機和開軟件

開機啟動后是這個畫面

賬號:

密碼:

右鍵屏幕左擊open terminal

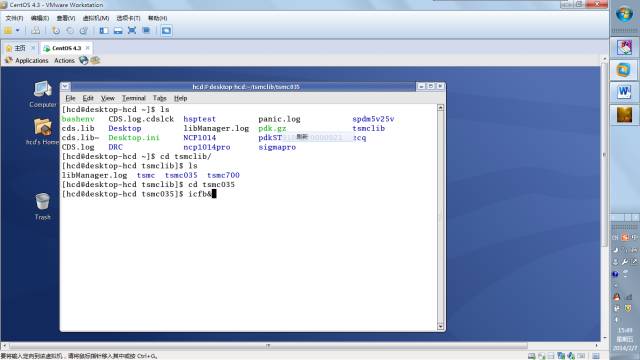

命令行里面打入如下圖的命令

ls 和 cd 是linux里面的命令。作用你就去網上查一下。

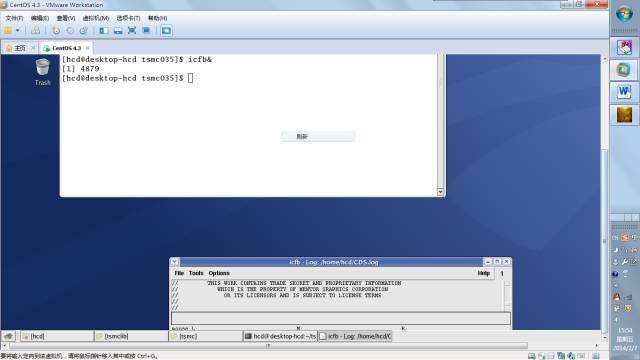

icfb&是打開cadence的命令。屏幕的底部會出現這么一個圖像界面。

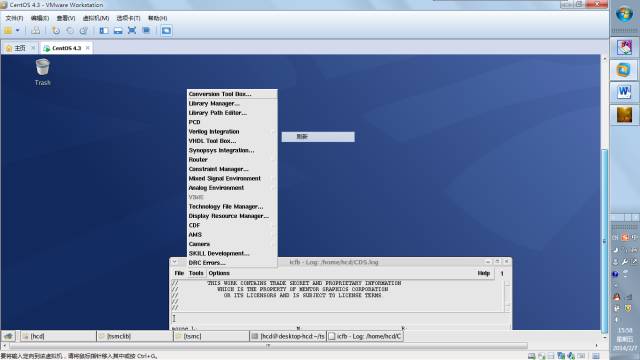

點擊圖形界面的Tools,會彈出下面這東西,點擊Library Manager

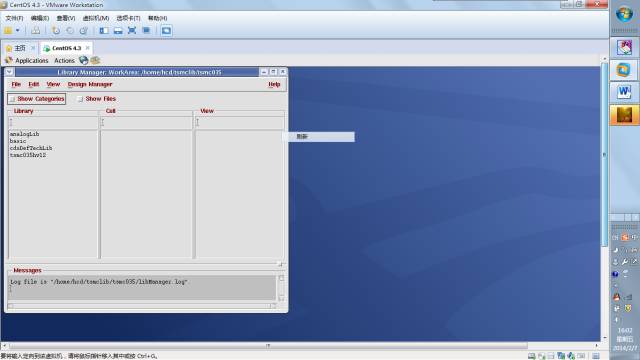

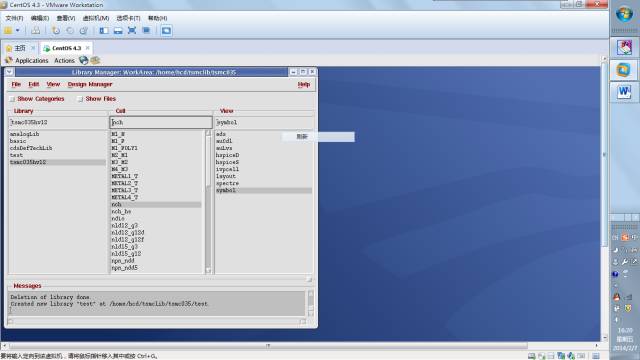

點擊后彈出如下圖所示的框圖

Library manager里面管理的時候分三個欄目。

Library,一般取自己的名字,拼音都可以

Cell,一般是你要設計的電路的名字

View,一個cell對應著不同的view,有版圖Layout,有原理圖schematics,等等。

2.軟件的library manager使用

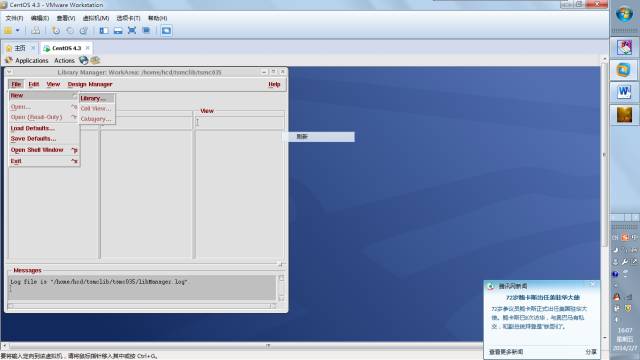

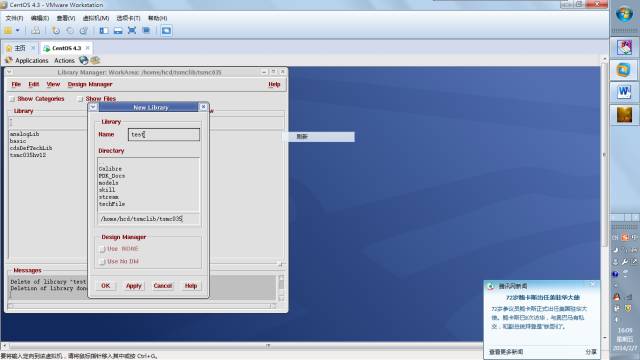

下一步首先創建自己的庫

OK后庫里面就有相應自己的庫了,自己做的電路可以放到里面管理,不要和其他的庫混著用。

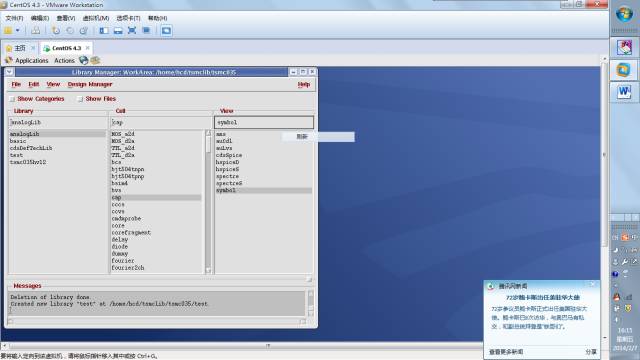

來看下軟件自帶的analogLib里都有哪些cell。

圖上選中的是cap,就是理想電容,對應的view有很多了,畫原理圖的時候,調用選用的view是symbol。

analogLib庫里面還有其他常用的元件:地gnd,直流電源vdc,直流電源idc,電流控制電壓源ccvs,理想電阻res等。這個自己去網上查到底有哪些。

庫tsmc035hv12是臺積電的.35的工藝庫(庫涉密,不鼓勵外傳)。這個庫里面我們用到的就是nch和pch,分別是nmos和pmos的模型名字。畫原理圖的時候,調用該cell的symbol。

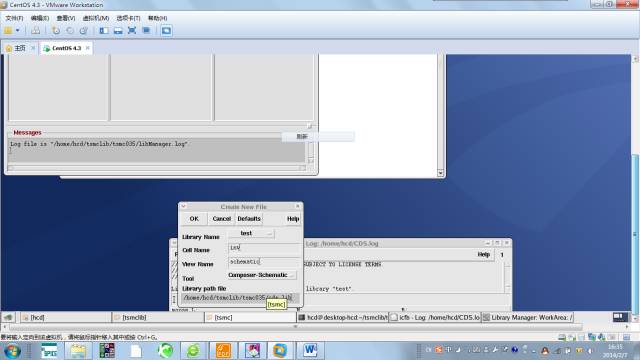

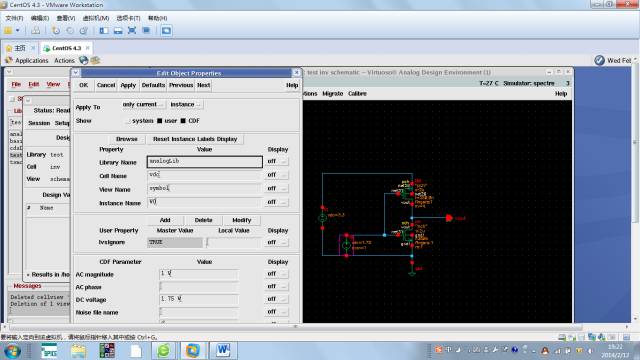

好了,下一步要創建自己的cell了。先選到自己新建的庫test。之后再點file->new->cellview

在屏幕下方會產生這樣的對話框,填入cell的名字,當畫原理圖時tool選圖中的這個。畫layout就選virtuoso,可以嘗試變一下。當然我們這選composer-schematic。

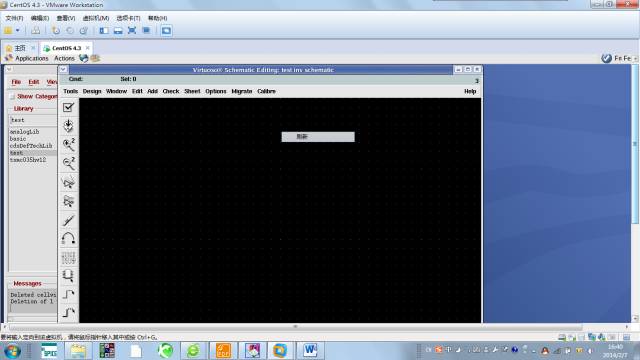

OK后會彈出這個窗口,用來畫原理圖。

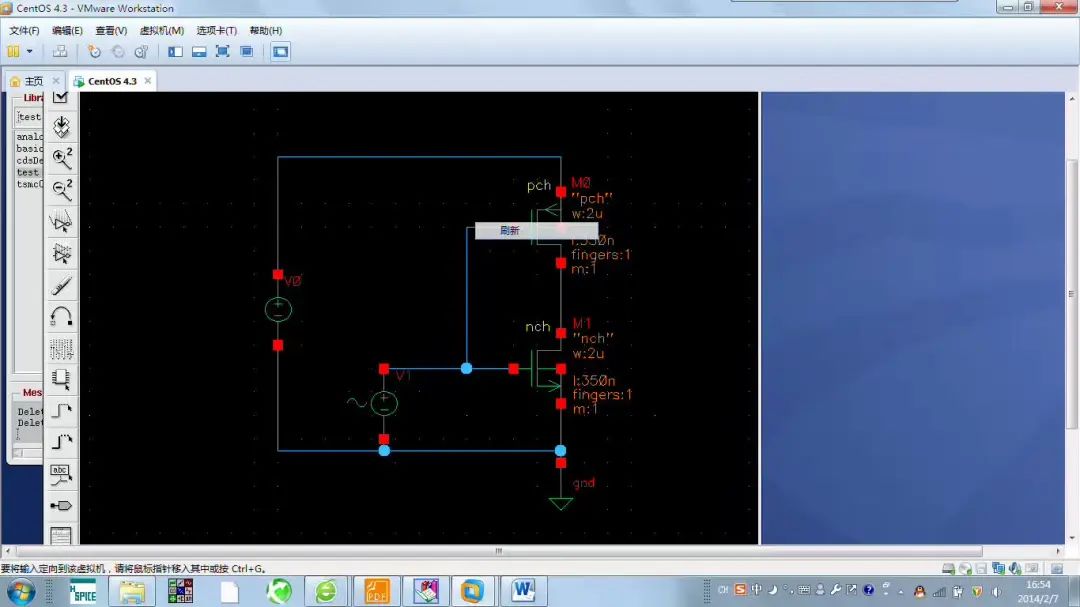

切換到英文輸入法,快捷鍵i是放置元件的意思 instance。我們需要nch,pch,gnd,電源vdc,還有信號源vsin。

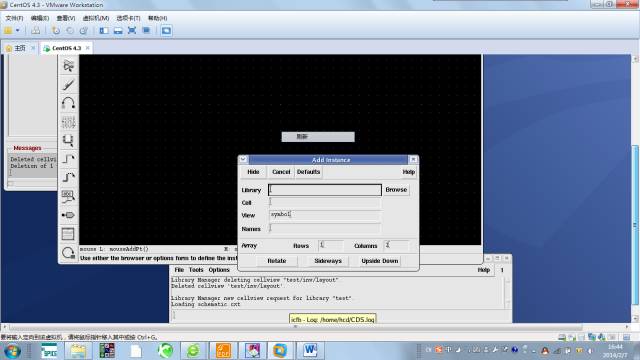

屏幕下面會彈出這個框框

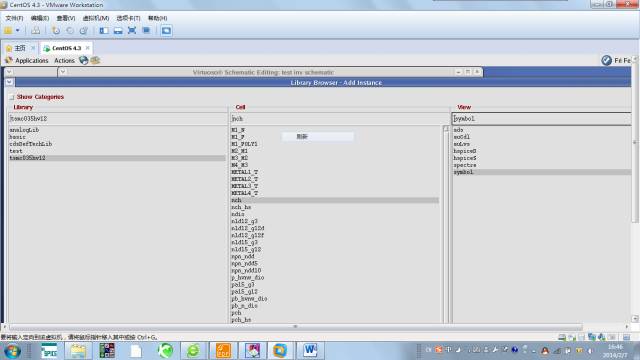

按browse選擇如下圖所示,這樣也就選中了nch,選其他元件也是這樣的方法。

只不過gnd,vdc,vsin是在analoglib里面找。

最小化該窗口,鼠標移動到schematic窗口,點擊就可以放下元件。

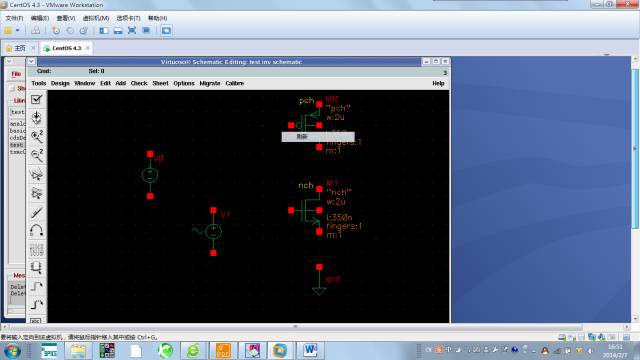

這樣就放置好元件了,按下快捷鍵w可以連線。

接著就是設置信號源和電壓源的信號幅度。

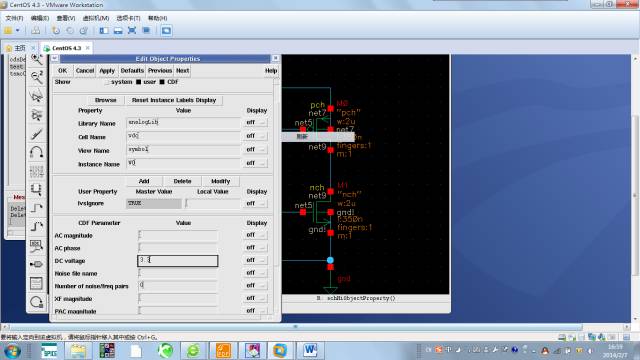

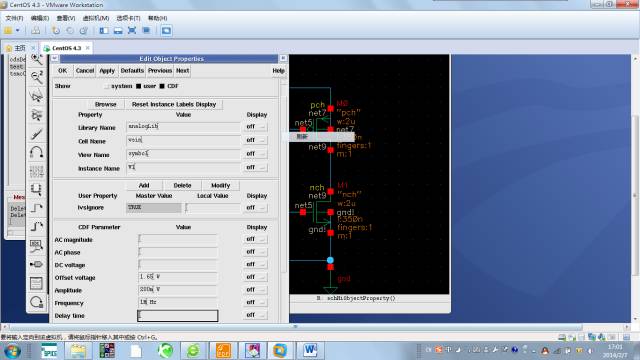

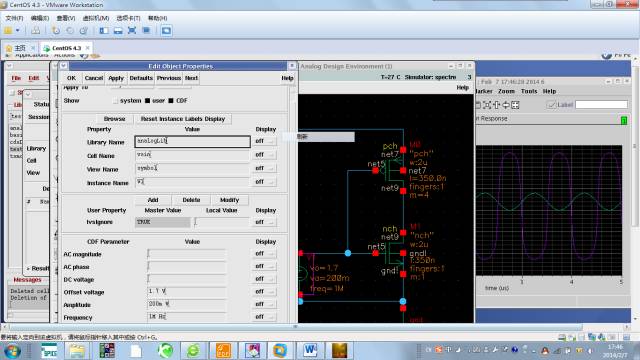

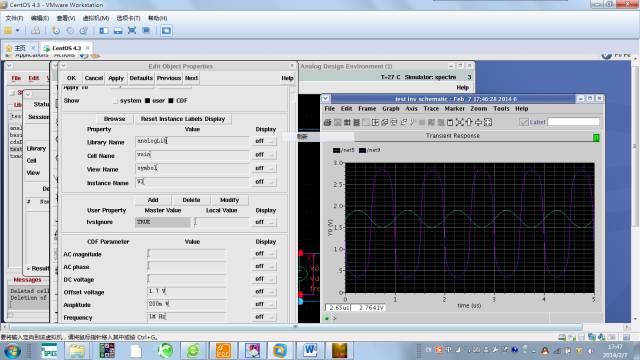

先選中元件v0,快捷鍵q可以查看和設置其參數。

V0設置直流電壓3.3V

V1設置offset電壓1.65V,正弦信號幅度200m,頻率1Mhz。注意:輸入這些值的時候,不需要輸入單位。200mV只需要輸入200m就可以了。1Mhz同理。

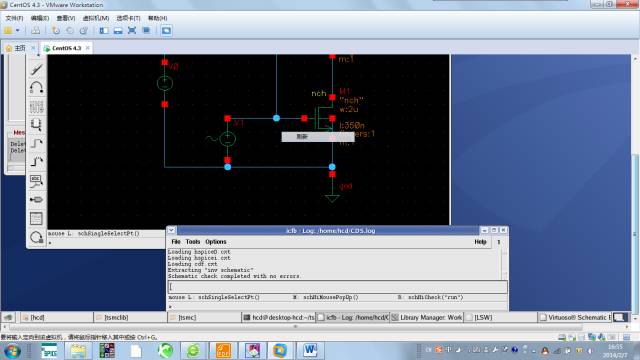

OK,這樣就連好了,按下快捷鍵x檢查電路是否連接完整和設置正確。如果無誤,在我們一開始的對話框里會有這么一句幾個字No errors。

這樣就可以仿真了。

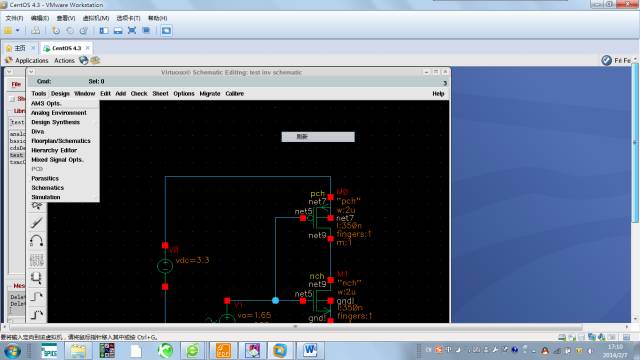

3.仿真工具使用

Analog environment就可以進入仿真了。

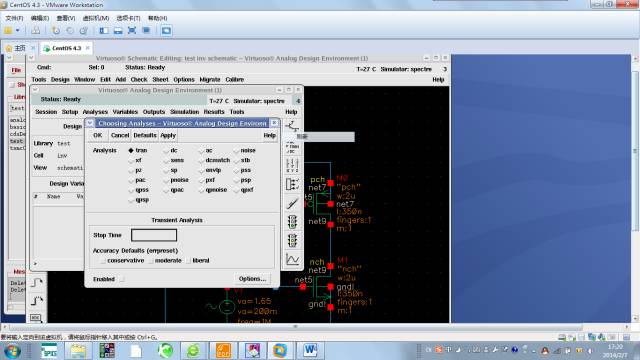

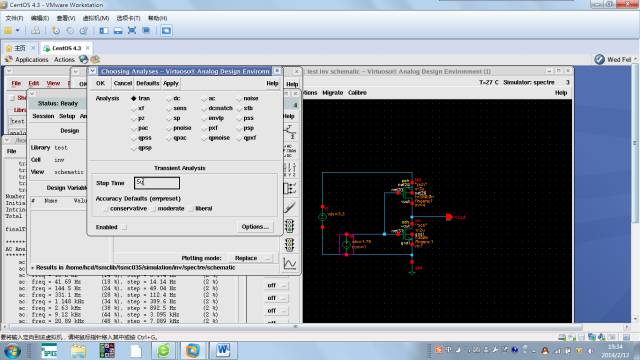

Analyses->choose彈出如下的畫面。

選擇瞬態仿真tran,Stop time 選5us,accuracy 可以不用選 enable選上。

其他常用的仿真如dc,ac自己可以查資料研究下。

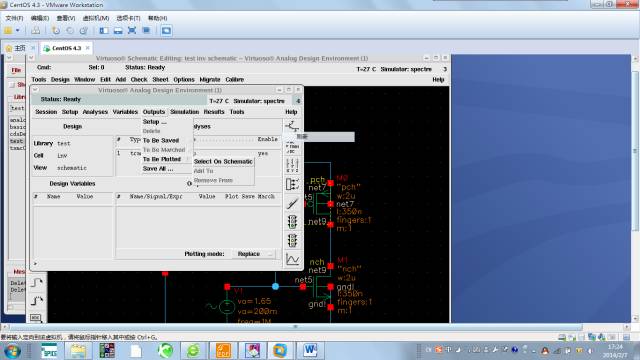

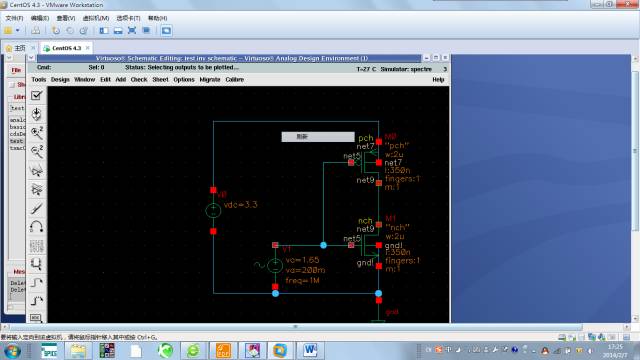

輸出信號這樣選擇outputs->tobe plotted->select on schematic

點擊上面的按鈕后窗口會自動彈到原理圖的窗口。點擊到連線上是查看該點的電位,點擊節點(紅色的地方)是查看改點的電流。選擇完之后會顯示出和其他不一樣的框框。按esc鍵退出選擇。我們選擇輸入和輸出節點。

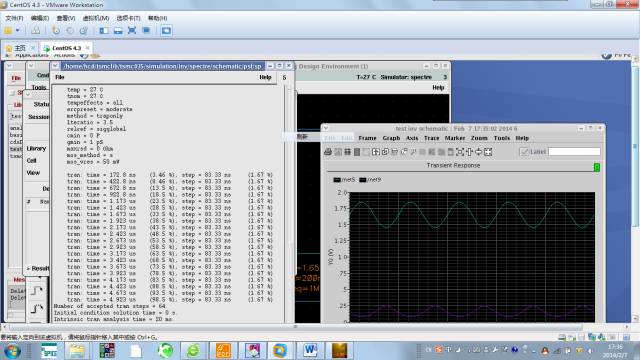

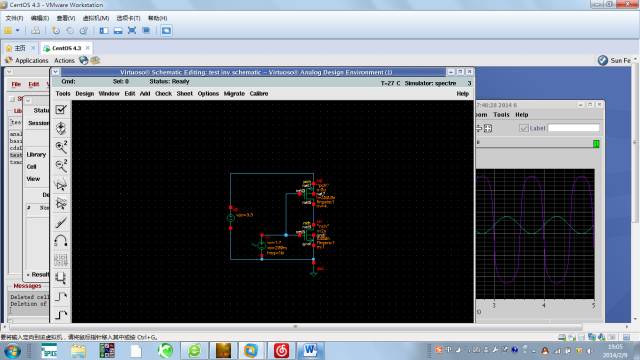

TRAN仿真

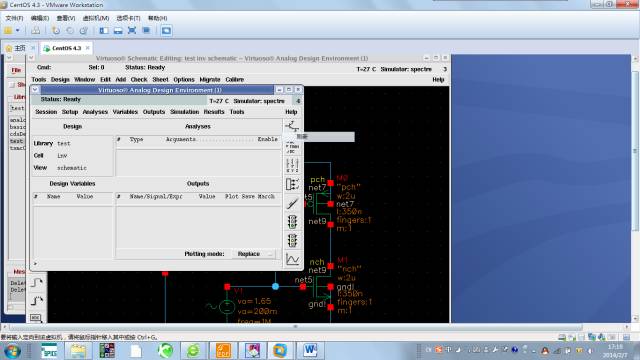

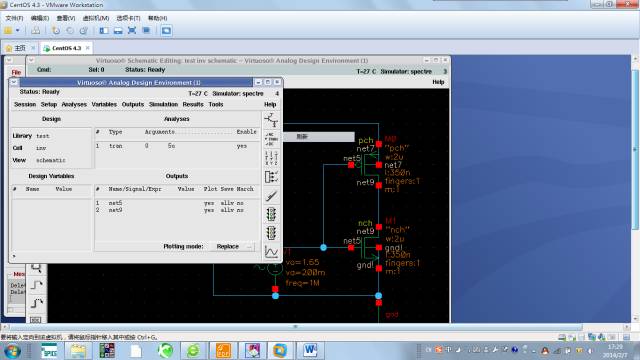

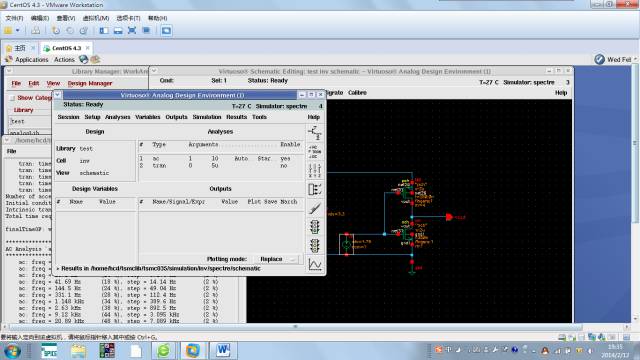

現在仿真窗口就變成這樣了

一個是仿真方案是tran仿真,輸出有兩個節點。按下右下腳最后第三個按鈕,有綠燈的那個按鈕就可以仿真了。

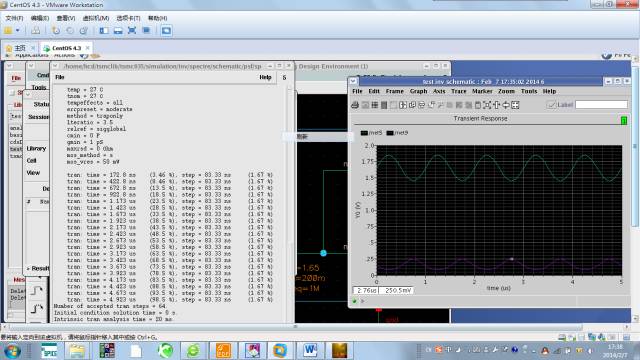

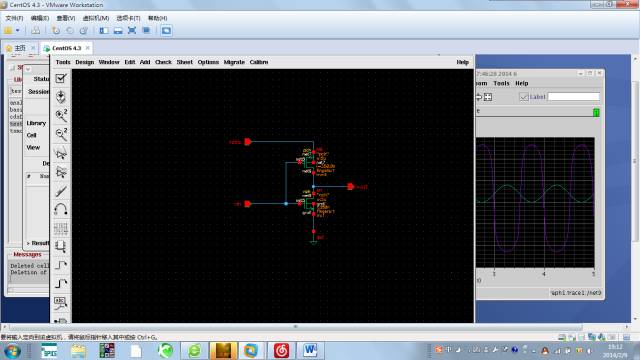

仿真出來有兩個圖,前一個類似hspice仿真后的lis文件。后面這個圖是輸出的結果圖。

顯然我們希望的反向器可定不可以這樣。所以要再原來的電路改進下。

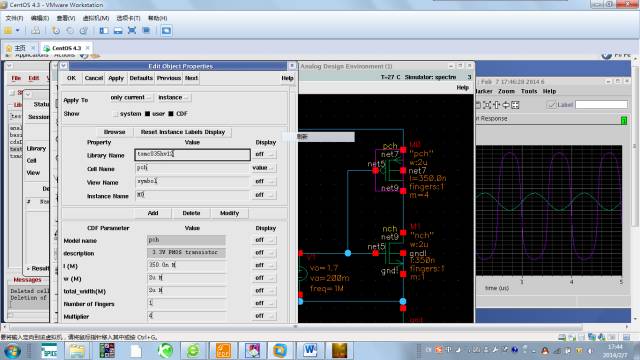

調整:M0管子要變動,Multiplier=4,這個就是并聯的個數的意思。

V1的offset電壓變成1.7.

再仿真,得出結果

這個是我們希望的反向器的結果。

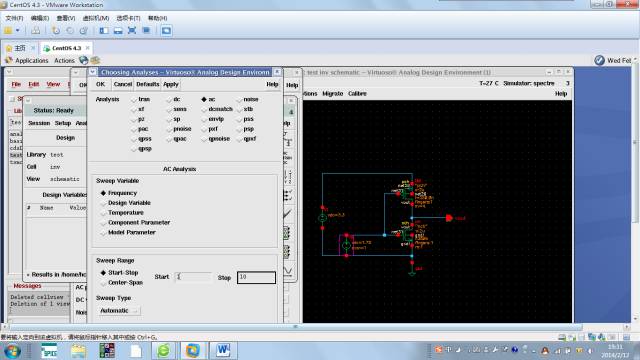

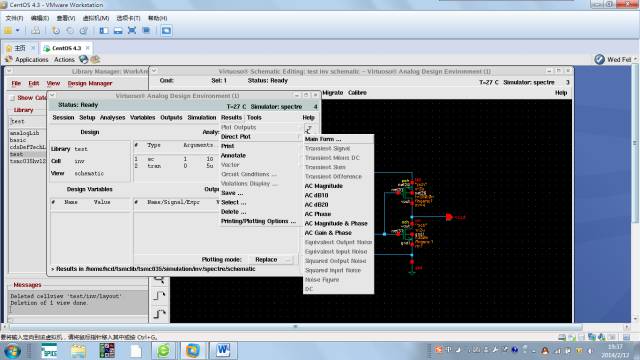

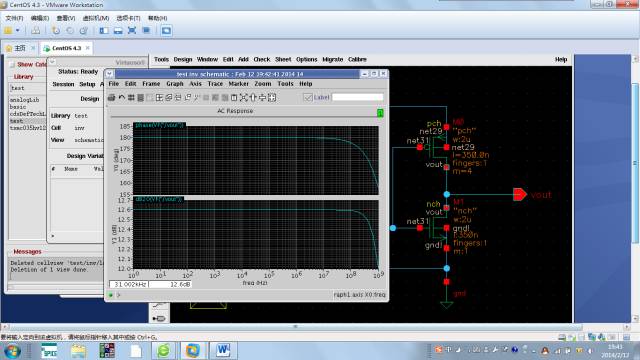

Ac仿真

仿真界面設置成如下圖所示的 analyses->choose

仿真選ac,start =1hz,stop=1Ghz,hz可以不用寫的

Tran仿真的enable選項不選擇

最后整個界面成下圖所示:

Ac 的enable 是yes的。Tran的enable是no。

點有綠色燈的按鍵進行仿真。

選擇ac magnitude&phase,窗口自動彈到原理圖界面,選擇輸出端口。

選擇了就有了邊框的顏色。

按esc鍵就可以看輸出結果。

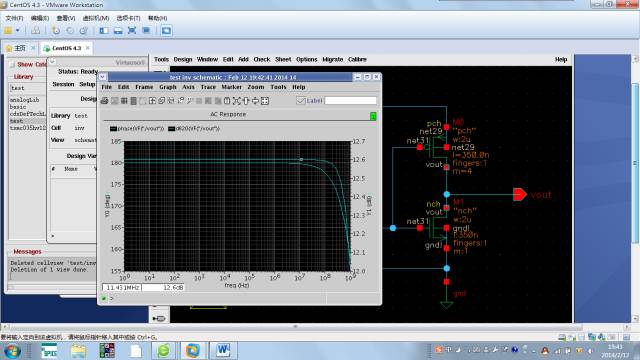

按圖片上從左到右第4個按鍵是將相位和增益曲線分開。分開后如下圖所示。

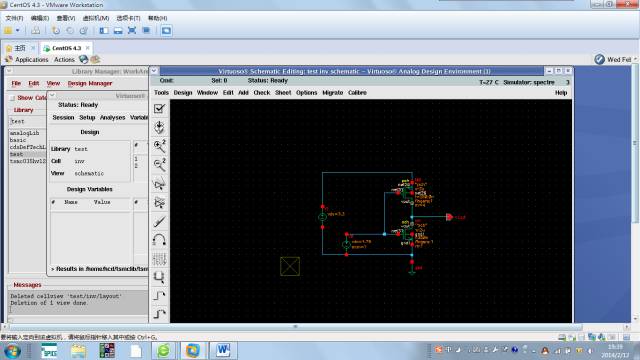

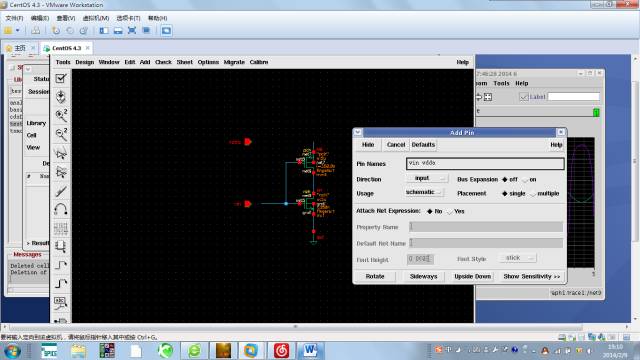

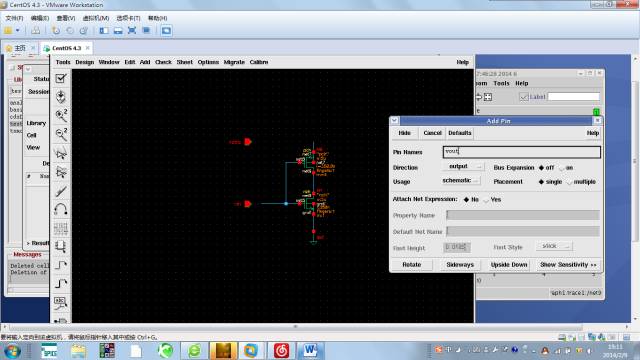

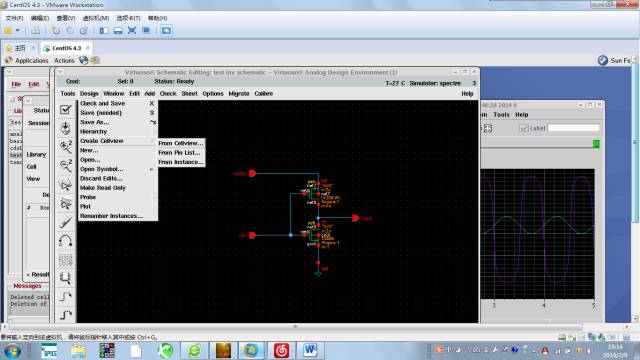

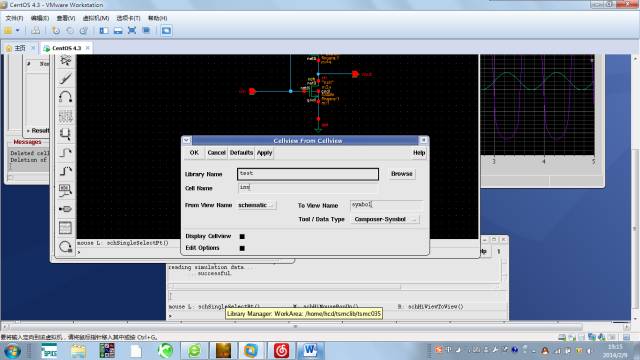

4.端口的添加和symbol的生成

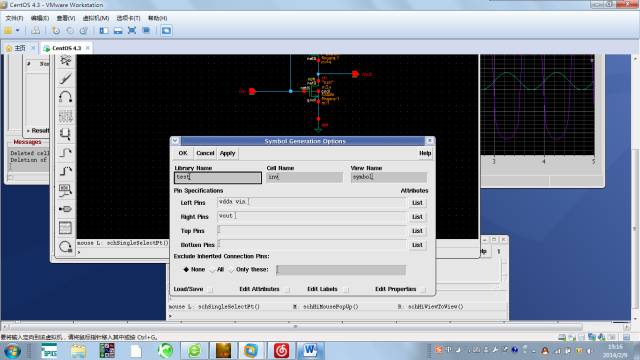

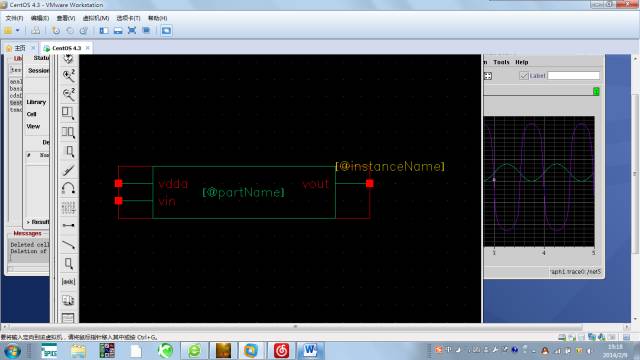

刪掉信號源,按快捷鍵p添加端口(port)。需要三個端口,輸入端口:vin,vdda;

輸出端口:vout(電源端口)。

這樣就完成了添加端口。之后是創建cellview。Design->create cellview->from pin list

選OK就可以了

這里的端口可以隨便放置,但一般的原則是輸入在左邊,輸出在右邊。點OK,得下圖。

紅色的框不可以刪除的,綠色的框可以任意修改。

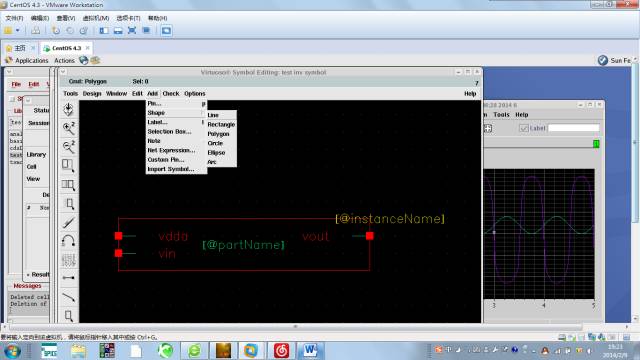

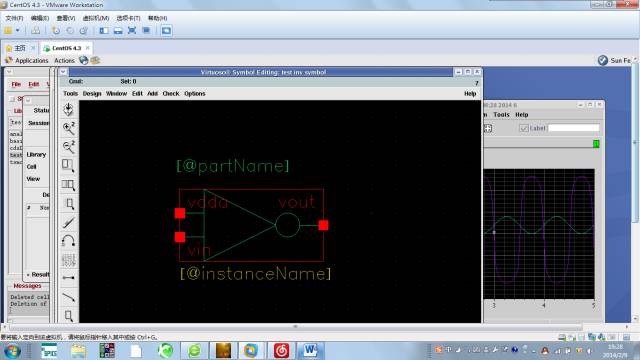

Add->shape->polygon可以畫多邊形,Add->shape->circle可以畫圓

還有經常用的:選中一個圖案后,按M鍵可以移動它。最后的樣子

Partname和instancename可以隨便放吧,盡量離圖形近一點。

5.總結

電路設計也就是如何調節元件參數使得信號得到處理。

-

電路設計

+關注

關注

6687文章

2487瀏覽量

207029 -

Cadence

+關注

關注

65文章

942瀏覽量

143170

原文標題:cadence的簡單操作流程

文章出處:【微信號:feifeijiehaha,微信公眾號:電路和微電子考研】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

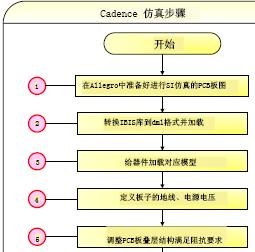

電源直流壓降的的仿真操作流程

Cadence仿真流程

Giantec采用Cadence技術統一數字流程生產其混合信號芯片

Cadence提供新一代Encounter RTL-to-GDSII流程

Cadence PCB封裝制作流程

Cadence 推出經過認證的創新背面實現流程,以支持 Samsung Foundry SF2 技術

Cadence 數字、定制/模擬設計流程通過認證,Design IP 現已支持 Intel 16 FinFET 制程

評論