內(nèi)存(DRAM-Random Access Memory)作為當(dāng)代數(shù)字系統(tǒng)最主要的核心部件之一,從各種終端設(shè)備到核心層數(shù)據(jù)處理 和存儲設(shè)備,從各種消費(fèi)類電子設(shè)備到社會各行業(yè)專用設(shè)備,是各種級別的 CPU 進(jìn)行數(shù)據(jù)處理運(yùn)算和緩存的不可或缺的周轉(zhuǎn)“倉庫”,一個強(qiáng)大的核心處理單元也必須配備一個高速運(yùn)轉(zhuǎn)的寬通路的數(shù)據(jù)訪問和存儲單元。

存儲芯片基本分類。存儲器主要分為只讀存儲器 ROM 和隨機(jī)存取存儲器 RAM (random access memory) 兩大類。

-ROM:只讀存儲器 - ROM 所存數(shù)據(jù),一般是裝入整機(jī)前事先寫好的,整機(jī)工作過程中只能讀出,ROM所存數(shù)據(jù)穩(wěn)定,斷電后所存數(shù)據(jù)也不會改變。

-RAM:隨機(jī)存取存儲器 (random access memory) - RAM 是與 CPU 直接交換數(shù)據(jù)的內(nèi)部存儲器,它可以隨時讀寫,速度快,通常作為操作系統(tǒng)或其他正在運(yùn)行中的程序的臨時數(shù)據(jù)存儲媒介,當(dāng)電源關(guān)閉時 RAM 不能保留數(shù)據(jù)。

-DDR SDRAM 在系統(tǒng)時鐘的上升沿和下降沿都可以進(jìn)行數(shù)據(jù)傳輸 - DDR SDRAM在 SDRAM 的基礎(chǔ)上發(fā)展而來,這種改進(jìn)型的 DRAM和 SDRAM 是基本一樣的,不同之處在于它可以在一個時鐘讀寫兩次數(shù)據(jù),這樣就使得數(shù)據(jù)傳輸速度加倍了,也是目前電腦中用得最多的內(nèi)存,而且具有成本優(yōu)勢。DDR 已經(jīng)發(fā)展至今已經(jīng)進(jìn)化到 DDR5,與 DDR4相比,DDR5 在強(qiáng)大的封裝中帶來了全新的架構(gòu)。

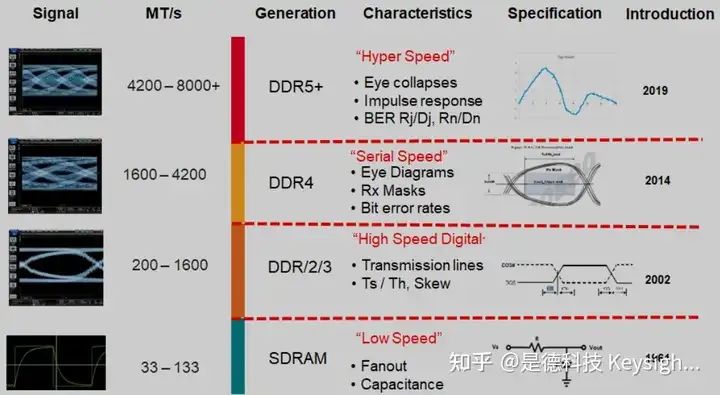

近 20 多年來,DRAM也快速地從 20 世紀(jì)末期的 SDRAM 發(fā)展到 21 世紀(jì) DDR RAM。在 21 世紀(jì)的前10 年,DDR標(biāo)準(zhǔn)主要是個人信息處理終端的代表設(shè)備----PC 和個人工作站類驅(qū)動,快速從 DDR1 演進(jìn)到 DDR3。而近 10 年來,進(jìn)入移動互聯(lián)時代后海量數(shù)據(jù)爆發(fā),AI 和深度學(xué)習(xí)以及 5G驅(qū)動,在個人信息終端上基本可以勝任的 DDR4標(biāo)準(zhǔn),明顯顯得力不從心。今天 DDR5正在昂首闊步地配合以 PCIE5.0 32Gbps 為代表的第5代高速 I/O 數(shù)據(jù)傳輸走向最終的市場化。

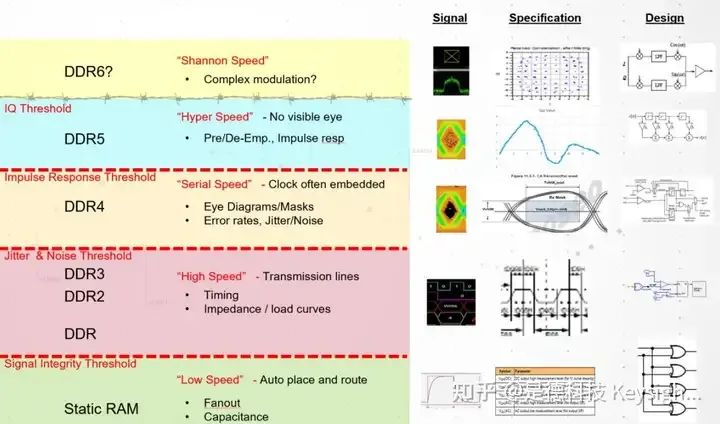

下圖展示的是內(nèi)存 RAM 20多年來的發(fā)展和信號特點(diǎn)以及設(shè)計演進(jìn)。

DDR標(biāo)準(zhǔn)發(fā)展和信號特點(diǎn)演進(jìn)

一些DDR基本概念

DDR是什么?

DDR的全拼是Double Data Rate SDRAM雙倍數(shù)據(jù)速率同步動態(tài)隨機(jī)存取內(nèi)存, 主要用在電腦的內(nèi)存。DDR的特點(diǎn)就是走線數(shù)量多,速度快,操作復(fù)雜,給測試和分析帶來了很大的挑戰(zhàn)。

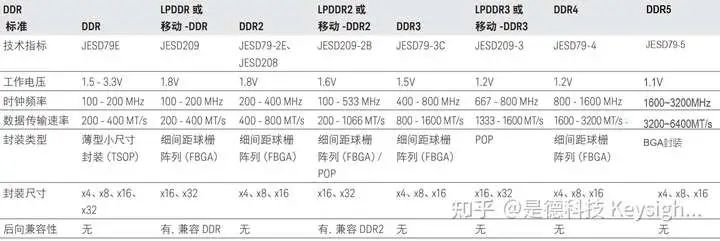

目前DDR技術(shù)已經(jīng)發(fā)展到了DDR5,性能更高,功耗更低,存儲密度更高,芯片容量大幅提升,他的數(shù)據(jù)速率在3200-6400MT/s。

DDR本質(zhì)上不需要提高時鐘頻率就能加倍提高SDRAM的速度,它允許在時鐘的上升沿和下降沿讀出數(shù)據(jù),因而其速度是標(biāo)準(zhǔn)SDRAM的兩倍,至于地址與控制信號則與傳統(tǒng)SDRAM相同,仍在時鐘上升沿進(jìn)行數(shù)據(jù)判斷。

DDR核心技術(shù)點(diǎn)就在于雙沿傳輸和預(yù)取Prefetch.

DDR的頻率包括核心頻率,時鐘頻率和數(shù)據(jù)傳輸頻率。核心頻率就是內(nèi)存的工作頻率;DDR1內(nèi)存的核心頻率是和時鐘頻率相同的,到了DDR2和DDR3時才有了時鐘頻率的概念,就是將核心頻率通過倍頻技術(shù)得到的一個頻率。數(shù)據(jù)傳輸頻率就是傳輸數(shù)據(jù)的頻率。

JEDEC 定義了 DDR 規(guī)范

DDR SDRAM(Double Data Rate Synchronous Dynamic Random Access Memory,雙數(shù)據(jù)率同步動態(tài)隨機(jī)存儲器),簡稱為DDR, 簡單的說就是雙倍傳輸速率的SDRAM。普通SDRAM內(nèi)存的工作方式是在一個時鐘周期的上升沿觸發(fā)進(jìn)行工作。也就是說在一個時鐘周期內(nèi),內(nèi)存將工作一次。而DDR的技術(shù)使得內(nèi)存可以在每一個時鐘周期的上升沿和下降沿分別觸發(fā)一次,這樣就使得在一個時鐘周期內(nèi)內(nèi)存可以工作兩次,這樣就使得DDR內(nèi)存在相同的時間內(nèi)能夠完成普通內(nèi)存一倍的工作量。(文末有DDR術(shù)語解釋)

DDR內(nèi)存原理

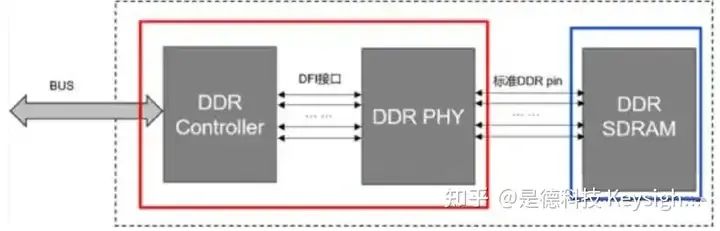

基本DDR subsystem架構(gòu)圖:DDRC +DDRphy +SDRAM顆粒,DDR IP一般包括DDR Controller和DDR PHY,內(nèi)部涉及的內(nèi)容包括但不限于以下幾個方面:數(shù)據(jù)保序、仲裁、最優(yōu)調(diào)度、協(xié)議狀態(tài)機(jī)設(shè)計、防餓死機(jī)制、bypass通路、快速切頻、DDR training

DDR工作原理

當(dāng)時鐘脈沖達(dá)到一定頻率時,DDR存儲器才開始工作,此后發(fā)生的就是“讀-存-讀”的過程。在此過程中,器件芯片會從主在取數(shù)據(jù),然后與入數(shù)據(jù)在儲區(qū)。當(dāng)寫入操作完成后,再從存儲區(qū)中取出數(shù)據(jù),並將其傳輸?shù)?a target="_blank">處理器中,然后根據(jù)需要將數(shù)據(jù)處理,再把最終結(jié)果返回到主存。

DDR 的雙倍數(shù)據(jù)傳輸率其實就是每個時鐘周期內(nèi)讀寫一次數(shù)據(jù),即DDR芯片可以在每個時鐘周期內(nèi)分別完成“讀-存”和“存-讀”操作,從而提高存儲器的傳輸效率。

DDR內(nèi)存通過雙倍數(shù)據(jù)速率的傳輸方式,結(jié)合多通道傳輸和數(shù)據(jù)校驗等技術(shù),提高了數(shù)據(jù)傳輸效率和可靠性。這使得 DDR 成為了計算機(jī)內(nèi)存的主流技術(shù)。

內(nèi)存芯片 -DDR內(nèi)存模塊中包含多個內(nèi)存芯片,每個芯片有自己的存儲單元。每個存儲單元都有一個地址,用于在讀取或?qū)懭霐?shù)據(jù)時進(jìn)行尋址。

數(shù)據(jù)總線 -DDR內(nèi)存模塊連接到計算機(jī)的內(nèi)存控制器,通過數(shù)據(jù)總線進(jìn)行數(shù)據(jù)傳輸。數(shù)據(jù)總線可以同時傳輸多個數(shù)據(jù)位,例如 64 位或 128位。

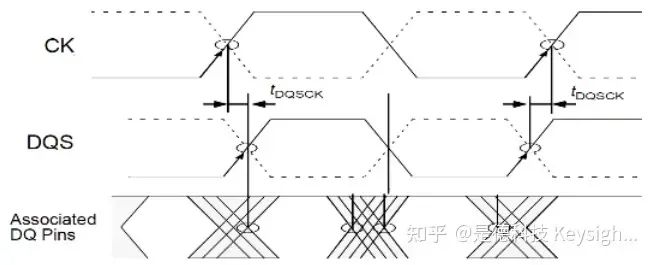

時鐘信號 -DDR內(nèi)存模塊通過時鐘信號進(jìn)行同步操作。時鐘信號用來控制數(shù)據(jù)的傳輸速率,每個時鐘周期內(nèi)有一個上升沿和一個下降沿。上升沿時,數(shù)據(jù)從內(nèi)存芯片傳輸?shù)綌?shù)據(jù)總線;下降沿時,數(shù)據(jù)從數(shù)據(jù)總線傳輸?shù)絻?nèi)存芯片。

預(yù)充電 -在開始傳輸數(shù)據(jù)之前,DDR內(nèi)存模塊會先進(jìn)行預(yù)充電操作。預(yù)充電是將存儲單元中的電荷恢復(fù)到初始狀態(tài),以確保接下來的數(shù)據(jù)傳輸是準(zhǔn)確的。

數(shù)據(jù)傳輸 -DDR 采用了多通道的數(shù)據(jù)傳輸方式,即同時傳輸多個數(shù)據(jù)位。這樣可以在每個時鐘周期內(nèi)傳輸更多的數(shù)據(jù)。

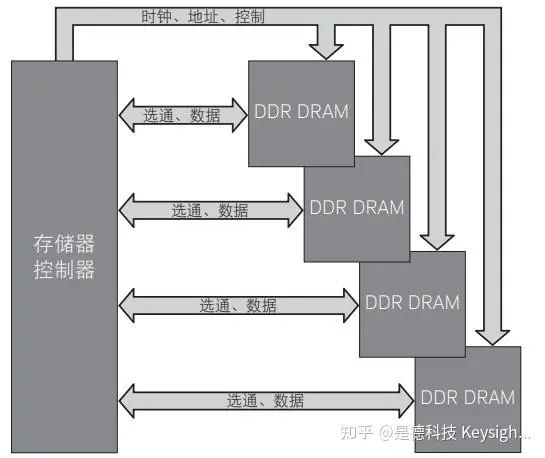

DDR接口可傳輸控制、地址、時鐘、選通和數(shù)據(jù)信號。如圖所示,時鐘、地址和控制信號從存儲器控制器單向傳輸?shù)?DDR芯片;選通和數(shù)據(jù)信號為雙向傳輸。在讀取操作中,選通和數(shù)據(jù)信號從DDR芯片傳輸?shù)酱鎯ζ骺刂破鳌T趯懭氩僮髦校盘栄叵喾捶较騻鬏敗kS著數(shù)據(jù)傳輸速率的增加和信號幅度的降低,為了提高信號性能,時鐘和選通信號采用差分信號,這樣可以消除共模噪聲。其他信號仍然在單端模式下操作,更容易受到噪聲、串?dāng)_和干擾的影響。

存儲器分類

存儲器分為內(nèi)部存儲器(內(nèi)存),外部存儲器(外存),緩沖存儲器(緩存)以及閃存這幾個大類。

內(nèi)存也稱為主存儲器,位于系統(tǒng)主機(jī)板上,可以同CPU直接進(jìn)行信息交換。其主要特點(diǎn)是:運(yùn)行速度快,容量小。

外存也稱為輔助存儲器,不能與CPU之間直接進(jìn)行信息交換。其主要特點(diǎn)是:存取速度相對內(nèi)存要慢得多,存儲容量大。

內(nèi)存與外存本質(zhì)區(qū)別是,一個是內(nèi)部運(yùn)行提供緩存和處理的功能,也可以理解為協(xié)同處理的通道;而外存主要是針對儲存文件、圖片、視頻、文字等信息的載體,也可以理解為儲存空間。緩存就是數(shù)據(jù)交換的緩沖區(qū) (稱作Cache),當(dāng)某一硬件要讀取數(shù)據(jù)時,會首先從緩存中查找需要的數(shù)據(jù),如果找到了則直接執(zhí)行,找不到的話則從內(nèi)存中找。由于緩存的運(yùn)行速度比內(nèi)存快得多,故緩存的作用就是幫助硬件更快地運(yùn)行。

閃存 (Flash Memory)是一種長壽命的非易失性的存儲器,數(shù)據(jù)刪除不是以單個的字節(jié)為單位而是以固定的區(qū)塊為單位。閃存是電子可擦除只讀存儲器(EEPROM) 的變種,閃存與EEPROM不同的是,EEPROM能在字節(jié)水平上進(jìn)行刪除和重寫而不是整個芯片擦寫,而閃存的大部分芯片需要塊擦除。由于其斷電時仍能保存數(shù)據(jù),閃存通常被用來保存設(shè)置信息,如在電腦的B1OS(基本程序)、PDA(個人數(shù)字助理)、數(shù)碼相機(jī)中保存資料等。

如何計算DDR帶寬?

SDRAM和DDR區(qū)別是什么?

DDR=雙倍速率同步動態(tài)隨機(jī)存儲器,是內(nèi)存的其中一種。DDR取消了主板與內(nèi)存兩個存儲周期之間的時間間隔,每隔2個時鐘脈沖周期傳輸一次數(shù)據(jù),大大地縮短了存取時間,使存取速度提高百分之三十。

SDRAM是 "Synchronous Dynamic random access memory”的縮寫,意思是“同步動態(tài)隨機(jī)存儲器”,就是我們平時所說的“同步內(nèi)存”。從理論上說,SDRAM與CPU頻率同步,共享一個時鐘周期。SDRAM內(nèi)含兩個交錯的存儲陣列,當(dāng)CPU從一個存儲陣列訪問數(shù)據(jù)的同時,另一個已準(zhǔn)備好讀寫數(shù)據(jù),通過兩個存儲陣列的緊密切換,讀取效率得到成倍提高。

DDR是SDRAM的更新?lián)Q代產(chǎn)品,采用5伏工作電壓,允許在時鐘脈沖的上升沿和下降沿傳輸數(shù)據(jù),這樣不需要提高時鐘的頻率就能加倍提高SDRAM的速度,并具有比SDRAM多一倍的傳輸速率和內(nèi)存帶寬。

DDR標(biāo)準(zhǔn)發(fā)展和信號特點(diǎn)演進(jìn)

DDR4和DDR5的性能差距?

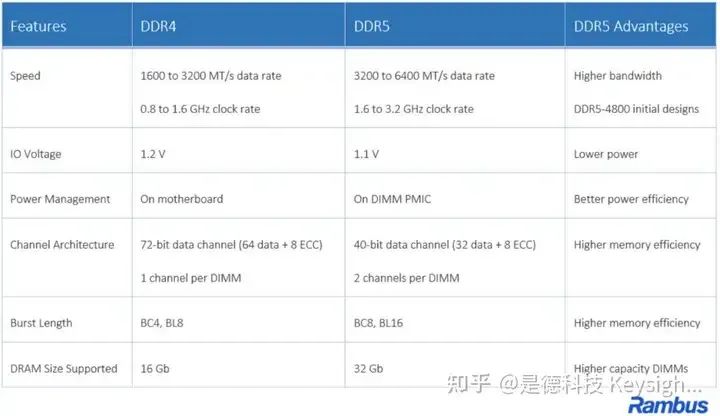

作為當(dāng)前市場主流的 DDR4標(biāo)準(zhǔn)和業(yè)界正在集中攻關(guān)的 DDR5標(biāo)準(zhǔn),對比有何差異呢?

如下表所列,從芯片開發(fā)到電路系統(tǒng)設(shè)計角度來看相比,DDR5 為了實現(xiàn)更高帶寬和吞吐量進(jìn)一步提升讀寫速率和改變通道架構(gòu)以及猝發(fā)讀寫長度,目前規(guī)劃的最高速率達(dá) 8400M T/s。

為了實現(xiàn)更低功耗和電源管理 I/O 電壓降到 1.1V,并在 DIMM 條上完成電源管理工作以實現(xiàn)更高 的電源效率(主要是縮短電源傳輸路徑以降低損耗和減小潛在的干擾)。為了提高數(shù)據(jù)帶寬,不僅 提升速率同時采用雙通道架構(gòu),提升讀寫效率,采用雙通道 32 data + 8 ECC,Burst Length 也從 4/8 提高到 8/16,最后還支持更高容量的 DRAM 器件,從 DDR4 16 Gb 加倍到 32 Gb。總之,DDR5 作為業(yè)界備受期望的第 5 代 I/O 的內(nèi)部數(shù)據(jù)共享和傳輸標(biāo)準(zhǔn)將與 PCI Express 5.0 乃至 6.0 等高速接口標(biāo)準(zhǔn)一起重塑 iABC 時代的大數(shù)據(jù)流的高速公路。

DDR4 和 DDR5 比較(源自 Rambus)

1.1 速率的提升

近年來,內(nèi)存與CPU性能發(fā)展之間的剪刀差越來越大,對內(nèi)存帶寬的需求日益迫切。DDR4在1.6GHz的時鐘頻率下最高可達(dá) 3.2 GT/s的傳輸速率,最初的 DDR5則將帶寬提高了 50%,達(dá)到 4.8 GT/s傳輸速率。DDR5 內(nèi)存的數(shù)據(jù)傳輸速率最終將會達(dá)到 8.4 GT/s。

1.2 電壓的降低

降低工作電壓(VDD),有助于抵消高速運(yùn)行帶來的功耗增加。在 DDR5 DRAM 中,寄存時鐘驅(qū)動器 (RCD) 電壓從 1.2 V 降至 1.1 V。命令/地址 (CA) 信號從 SSTL 變?yōu)?PODL,其優(yōu)點(diǎn)是當(dāng)引腳處于高電平狀態(tài)時不會消耗靜態(tài)功率。

1.3 DIMM新電源架構(gòu)

使用 DDR5 DIMM 時,電源管理將從主板轉(zhuǎn)移到 DIMM 本身。DDR5 DIMM 將在 DIMM 上安裝一個 12 V 電源管理集成電路(PMIC),使系統(tǒng)電源負(fù)載的顆粒度更細(xì)。PMIC 分配1.1 V VDD 電源,通過更好地在 DIMM 上控制電源,有助于改善信號完整性和噪音。

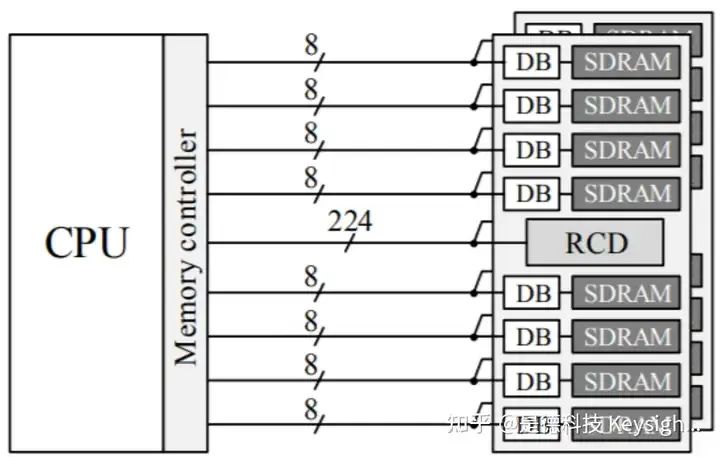

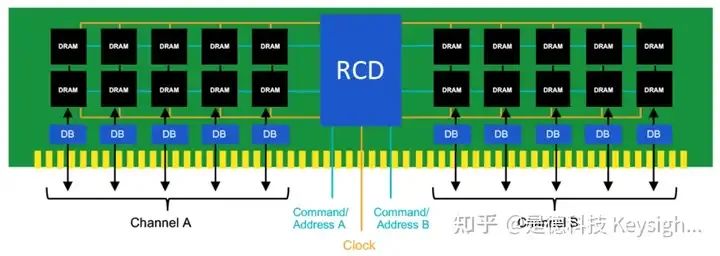

1.4 DIMM通道架構(gòu)

DDR4 DIMM 具有 72 位總線,由 64 個數(shù)據(jù)位和 8 個 ECC 位組成。在 DDR5 中,每個 DIMM 都有兩個通道。每個通道寬 40 位,32 個數(shù)據(jù)位和 8 個 ECC 位。雖然數(shù)據(jù)寬度相同(共 64 位),但兩個較小的獨(dú)立通道提高了內(nèi)存訪問效率。因此,使用 DDR5 不僅能提高速度,還能通過更高的效率放大更高的傳輸速率。

DDR5總線架構(gòu)和標(biāo)準(zhǔn)DDR5 RDIMM 內(nèi)存條

1.5 更長的突發(fā)長度

DDR4 的突發(fā)長度為4或者8。對于 DDR5,突發(fā)長度將擴(kuò)展到8和16,以增加突發(fā)有效載荷。突發(fā)長度為16(BL16),允許單個突發(fā)訪問 64 字節(jié)的數(shù)據(jù),這是典型的 CPU 高速緩存行大小。它只需使用兩個獨(dú)立通道中的一個通道即可實現(xiàn)這一功能。這極大地提高了并發(fā)性,并且通過兩個通道提高了內(nèi)存效率。

1.6 更大容量的 DRAM

DDR4 在單芯片封裝(SDP)中的最大容量為16 Gb DRAM。而DDR5的單芯片封裝最大容量可達(dá)64 Gb,組建的DIMM 容量則翻了兩番,達(dá)到驚人的 256 GB。

DDR5主要特點(diǎn)

從物理層信號角度來看,DDR5主要有如下特點(diǎn):

1.采用分離式全速率時鐘,對應(yīng) 6400M T/s 頻率最高達(dá) 3.2GHz。

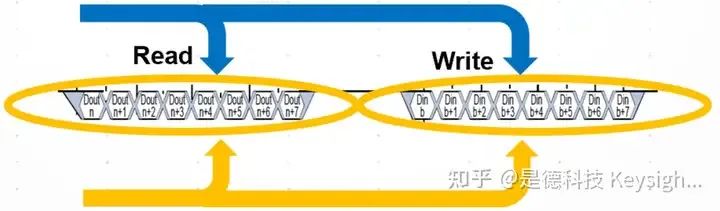

時鐘控制命令信號,選通信號控制數(shù)據(jù),如上圖示。 對時鐘信號抖動的要求更加嚴(yán)格,對各 種命令信號與數(shù)據(jù)和地址信號的時序要求也更高。2.更寬的總線,單端信號,從 RCD(Registering Clock Drivers)芯片來看采用 Multi-Drop 架構(gòu)。基于今天更寬的總線需求,在一塊刀片服務(wù)器上可能支持 1000+個并行數(shù)據(jù)通道。且由于 繼續(xù)采用單端信號且速率倍增,傳統(tǒng)只在串行差分電路上考慮的損耗問題也開始困擾 DDR5。因此 在 DDR5設(shè)計和驗證測試上,不僅需要考慮傳統(tǒng)的串?dāng)_問題還增加了對電路損耗問題的考慮。3.雙向復(fù)用的數(shù)據(jù)總線,讀寫數(shù)據(jù)分時復(fù)用鏈路。囿于有限的鏈路通道和布板空間等資源讀寫操作繼續(xù)采用共享總線,因此需要分時操作。從驗證測試角度來看也需要分別對讀和寫信號進(jìn)行分離以檢查其是否滿足規(guī)范。

DDR5 讀寫共享總線

4.猝發(fā) DQS 和 DQ 信號在更高速率的背景下在有限帶寬的鏈路傳輸時帶來更多 ISI 效應(yīng)問題。

在 DQS 讀寫前導(dǎo)位,猝發(fā)第一個 bit 等等均有不同的效應(yīng)和表現(xiàn)。此外考慮到存儲電路在設(shè)計上不同于串行電路存在較多的阻抗不匹配,因此反射問題或干擾帶來的 ISI 也會更嚴(yán)重。

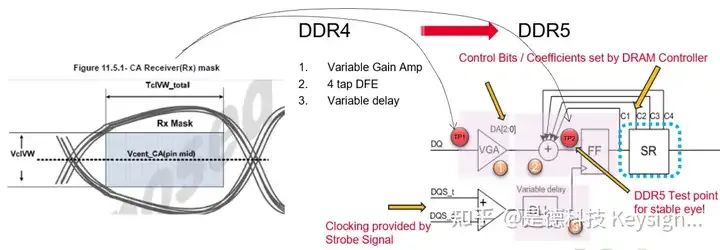

DDR5 在接收端采用更多的類似高速串行總線的信號處理

因此在接收側(cè)速率大于 3600M T/s 時采用類似高速串行電路和標(biāo)準(zhǔn)總線中已經(jīng)成熟的DFE均衡技術(shù),可變增益放大(VGA)則通過 MR 寄存器配置,以補(bǔ)償在更高速率傳輸時鏈路上的損耗。DDR4標(biāo)準(zhǔn)采用的 CTLE 作為常用的線性均衡放大,雖然簡單易實現(xiàn)但是其放大噪聲的副產(chǎn)品也更 為常見,考慮到 DDR5總線里的反射噪聲比沒有采用。另外考慮到并行總線的串?dāng)_和反射等各信 號抖動的定義和分析也會隨之變化。 從測試角度來看,示波器是無法得到 TP2點(diǎn)即均衡后的信號的,而僅能得到 TP1點(diǎn)的信 號,然后通過集成在示波器上的分析軟件里的均衡算法對信號進(jìn)行均衡處理以得到張開的眼圖。眼圖分析的參考時鐘則來自基于時鐘信號的 DQS 信號。另外眼圖測試也從以往僅對 DQ 進(jìn)行擴(kuò)展 到包括 CMD/ADDR總線。

DDR術(shù)語

DDR- Double Data Rate 雙倍速率

SDRAM- Synchronous Dynamic Random Access Memory的縮寫,即同步動態(tài)隨機(jī)存取存儲器。

DDR SDRAM- Double Data Rate SDRAM的縮寫,是雙倍速率同步動態(tài)隨機(jī)存儲器的意思。

Channel- 簡單理解一個通道對應(yīng)一個DDR控制器,每個通道擁有一組地址線、控制線和數(shù)據(jù)線

DIMM- DIMM全稱Dual-Inline-Memory-Modules,中文名叫雙列直插式存儲模塊,是指奔騰CPU推出后出現(xiàn)的新型內(nèi)存條,它提供了64位的數(shù)據(jù)通道。是主板上的一個內(nèi)存插槽,一個channel可以包含多個DIMM。

Rank- 一組可以被一個內(nèi)存通道同時訪問的芯片組合稱作一個rank,一個rank中的每個芯片都共用內(nèi)存通道提供的地址線、控制線和數(shù)據(jù)線,同時每個芯片都提供一組輸出線,這些輸出線組合起來就是內(nèi)存條的輸出線。簡單來說rank是一組內(nèi)存芯片集合,當(dāng)芯片位寬*芯片數(shù)=64bit(內(nèi)存總位寬)時,這些芯片組成一個Rank,存儲64bit的數(shù)據(jù)。一般每個芯片位寬是8bit,然后內(nèi)存條每面8個芯片,那么每面就構(gòu)成了一個Rank,這兩面的Rank通過一根地址線來區(qū)分當(dāng)前要訪問的是哪一面。同一個Rank中所有的芯片協(xié)作來讀取一個地址(1個Rank,8個芯片*8bit=64bit),這個地址的不同bit,每8個一組分散在這個Rank上的不同芯片上。設(shè)計Rank的原因是為了減少每個芯片的位寬(在CPU總位寬確定的前提下,比如64bit),降低復(fù)雜度。

Chip- 是內(nèi)存條上的一個芯片,由多個bank組成,大多數(shù)是4bit/8bit/16bit,多個chip做成一個rank,配合完成一次訪問的位寬。

Bank- 是一個邏輯上的概念。一個bank可以分散到多個chip上,一個chip也可以包含多個bank。DDR4以前是沒有Bank Group的,所以該值就表示整個顆粒中Bank數(shù)量。但是在DDR4和DDR5中,就表示每個Bank Group中Bank的數(shù)量,整個顆粒Bank數(shù)量 = Bank Group * Bank。

8陣列bank

Row、Column組成的memory array- 可以簡單的理解bank為一個二維bit類型的數(shù)組。每個bank對應(yīng)一個bit,8個bank組成8bit的數(shù)據(jù)。

Voltage(VDDQ)- 存儲芯片(顆粒)的輸出緩沖供電電壓。

Device Width- 顆粒位寬,常見為4/8/16bit。一個Memory Array中由行地址和列地址的交叉選中一個位,若2個Array疊加在一起,就同時選中了2個Bit,位寬是X2。若4個Array疊加到一起,就能夠同時選中4個Bit,位寬則是X4。也就是說,對一個X4位寬的DDR 顆粒,如果給出行地址和列地址,就會同時輸出4個Bit到DQ(數(shù)據(jù)輸入、輸出:雙向數(shù)據(jù)總線)數(shù)據(jù)線上。

Die Density- 顆粒密度,也就是容量,隨著DDR迭代,容量越來越大。

Data rates- MT/s指每秒傳輸多少個數(shù)據(jù)(Mega-transfer per second),和時鐘頻率是兩個不同的概念。DDR(dual data rate)是雙邊沿傳輸數(shù)據(jù)。因此MT/s是IO時鐘頻率的兩倍。

Prefetch- 在一個時鐘周期中,同時將相鄰列地址的數(shù)據(jù)一起取出來,并行取出DRAM數(shù)據(jù),再由列地址0/1/2(DDR1使用列0,DDR2使用列0和列1,DDR3/DDR4使用列0,1和2)選擇輸出。2n/4n/8n。這里的數(shù)字指的就是并行取出的位數(shù)。這里的n,就是DQ位寬,即上面的device width(x4/x8/x16)。所以DDR3 16bit SDRAM內(nèi)存顆粒,16bit指的是位寬,其一次讀寫訪問的數(shù)據(jù)量是8*16=128bit

Bank Group- Bank分組數(shù)量,該特性只存在于DDR4和DDR5中

Burst Length- 指突發(fā)長度,突發(fā)是指在同一行中相鄰的存儲單元連續(xù)進(jìn)行數(shù)據(jù)傳輸?shù)姆绞剑B續(xù)傳輸所涉及到存儲單元(列)的數(shù)量就是突發(fā)長度,在DDR SDRAM中指連續(xù)傳輸?shù)闹芷跀?shù)。一般對應(yīng)預(yù)取bit數(shù)目。

Core frequency- 顆粒核心頻率,即內(nèi)存cell陣列的工作頻率,它讀取數(shù)據(jù)到IO Buffer的頻率。它是內(nèi)存頻率的基礎(chǔ),其他頻率都是在該頻率的基礎(chǔ)上得出來的。

IO clk Frequency- 內(nèi)存的數(shù)據(jù)傳輸速率。它和內(nèi)存的prefetch有關(guān)。對于DDR,一個時鐘周期的上升沿和下降沿都在傳輸數(shù)據(jù),即一個時鐘周期傳輸2bit的數(shù)據(jù),所以DDR的prefetch為2bit。對于DDR2,IO時鐘頻率是其核心頻率的兩倍,同時也是雙沿傳輸數(shù)據(jù),因此DDR2的prefetch為2×2bit=4bit。對于DDR3,IO時鐘頻率是其核心頻率的四倍,同時也是雙沿傳輸數(shù)據(jù),因此DDR3的prefetch為4×2bit=8bit。

Arbitration CMD priority- 仲裁器,仲裁CMD的優(yōu)先級。會對來自各端口的請求進(jìn)行仲裁,并將請求發(fā)送給控制器,仲裁其從端口收到的每個事務(wù),每個事務(wù)都有一個相對應(yīng)的優(yōu)先級。端口仲裁邏輯會根據(jù)優(yōu)先級進(jìn)行處理,從而確定如何向控制器發(fā)出請求。以Cadence Denali內(nèi)存控制器為例,它有幾種仲裁策略:

Round Robin- 每個端口對應(yīng)一個獨(dú)立的計數(shù)器,當(dāng)端口上有請求被接受的時候,計數(shù)器就會增加,然后仲裁器會針對計數(shù)器非0的端口的請求進(jìn)行輪流仲裁,每仲裁執(zhí)行一次,相應(yīng)端口的計數(shù)器減一,直到端口接受請求計數(shù)器變?yōu)?。

帶寬分配/優(yōu)先級輪流操作- 結(jié)合輪流操作、優(yōu)先級、帶寬和端口帶寬保持等,根據(jù)用戶分配的命令優(yōu)先級,將傳入的命令按優(yōu)先級分組。在每個優(yōu)先級組內(nèi),仲裁器評估請求的端口、命令隊列和請求的優(yōu)先級,從而確定優(yōu)先級。當(dāng)控制器繁忙時,超過其帶寬分配的端口,可能會接受較低的優(yōu)先級服務(wù)。

加權(quán)優(yōu)先級循環(huán)- 是一種面向服務(wù)質(zhì)量的算法,結(jié)合了循環(huán)操作、優(yōu)先級、相對優(yōu)先級、端口排序的功能。根據(jù)命令的優(yōu)先級或該類型命令的相關(guān)端口的優(yōu)先級,將傳入的命令分成優(yōu)先級組。具有較高權(quán)重的端口可能會更頻繁的接受仲裁,從而更容易被運(yùn)行到

DDR SDRAM Control- DDR SDRAM的控制。包含了一個命令隊列,接受來自仲裁器的命令。該命令隊列使用一個重排算法來決定命令的放置順序。重排邏輯遵循一些規(guī)則,通過考慮地址碰撞、源碰撞、數(shù)據(jù)碰撞、命令類型和優(yōu)先級,來確定命令插入到命令隊列的位置。重排邏輯還通過命令分組和bank分割,來提高控制器的效率。當(dāng)命令進(jìn)入命令隊列后,選擇邏輯掃描命令隊列中的命令進(jìn)行運(yùn)行。若較高優(yōu)先級的命令還沒有準(zhǔn)備好運(yùn)行,較低優(yōu)先級的命令不與命令隊列中排在前面的命令沖突,那么這個較低優(yōu)先級的命令,可以先于該沒準(zhǔn)備好的高優(yōu)先級命令運(yùn)行。此外,控制器還包含一個仲裁塊,支持軟件可編程接口、外部引腳及計數(shù)器的低功耗控制。另外,控制器支持調(diào)頻功能,用戶可以通過操作寄存器組,調(diào)整ddr的工作頻率。

Transaction Processing- 事務(wù)處理用于處理命令隊列中的命令。該邏輯會重排命令,使DRAM的讀寫帶寬吞吐最大化。

-

DDR

+關(guān)注

關(guān)注

11文章

712瀏覽量

65341 -

內(nèi)存

+關(guān)注

關(guān)注

8文章

3025瀏覽量

74047

原文標(biāo)題:硬件必懂DDR內(nèi)存原理(值得收藏)

文章出處:【微信號:mcu168,微信公眾號:硬件攻城獅】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

什么是DDR SDRAM內(nèi)存

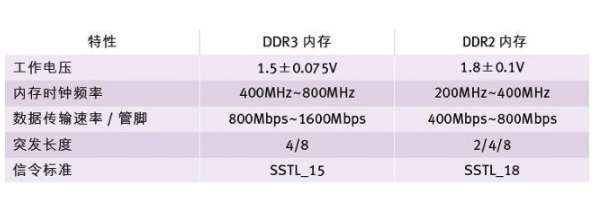

ddr4和ddr3內(nèi)存的區(qū)別,可以通用嗎

一文了解內(nèi)存DDR的頻率

DDR4和DDR3內(nèi)存都有哪些區(qū)別?

一文看懂從DDR1到DDR5的主要區(qū)別和特點(diǎn)

什么是DDR4內(nèi)存的工作頻率

一文讀懂DDR內(nèi)存基礎(chǔ)知識

一文看懂DDR內(nèi)存的原理

一文看懂DDR內(nèi)存的原理

評論