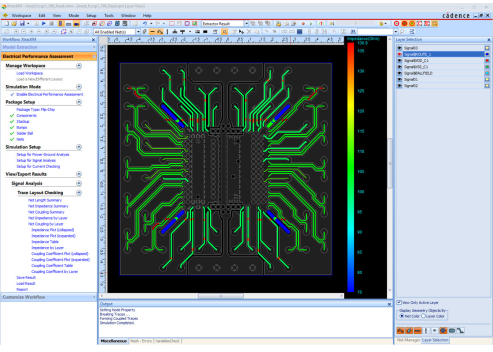

Cadence Allegro Package Designer Plus提供了一個完整的原理圖驅動的封裝基板布局布線環境。用于FlipChip,Wirebonding,SiP模塊等多種形式的封裝物理設計。這包括基板布局和布線,芯片、基板和系統級別上最終的連接優化,生產準備,全面的設計驗證和流片。

它還集成了I/O規劃協同設計能力(面向數字IC)和三維晶元堆疊結構生成與編輯功能。它支持所有的封裝類型,包括PGA、BGA、uBGA、芯片級封裝、倒裝芯片和鍵合芯片封裝。

在所有相關的設計構造中,可實現管理設計元件之間的物理實現、電氣和制造規則,讓設計師可以對整個系統的互聯進行權衡和優化。實時設計規則檢查(DRC)可支持層壓、陶瓷、及鍍膜技術間各種組合的復雜和獨特的規則要求。APD+額外的選項包還支持多重腔體、復雜形狀與交互式和自動化引線鍵合。

功能說明

-

封裝

+關注

關注

128文章

8206瀏覽量

144055 -

allegro

+關注

關注

42文章

673瀏覽量

146204 -

基板

+關注

關注

2文章

292瀏覽量

23289

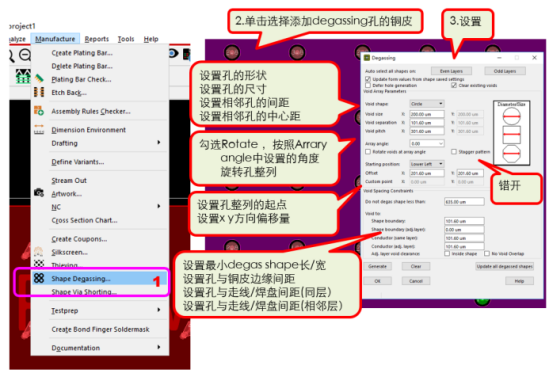

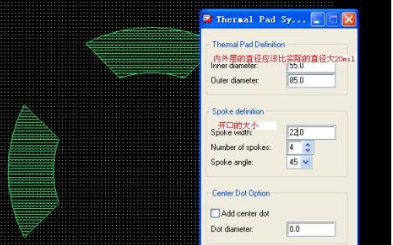

原文標題:【技術指南】Allegro Package Designer Plus中設置Degassing向導

文章出處:【微信號:封裝與高速技術前沿,微信公眾號:封裝與高速技術前沿】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

【eda經驗分享】如何使用Altium Designer導入Allegro的brd文件

Allegro中的Package Keepin區域外怎樣放置元件封裝

Allegro中建立異形焊盤

在Altium Designer中怎么導入ALLEGRO的brd文件

Altium Designer PCB與Allegro PCB相互轉換

Altium Designer為什么沒有TSSOP封裝向導

【Altium小課專題 第139篇】Allegro PCB如何轉換成Altium Designer PCB?

Allegro Package Designer

ALLEGRO PACKAGE DESIGNER 620/A

Allegro中尺寸標注參數的設置

如何使用Allegro中的Pad Designer制作焊盤詳細教程免費下載

評論