本文翻譯轉(zhuǎn)載于:Cadence blog

作者:Paul Graykowski

混合信號設(shè)計在半導體設(shè)計飛速發(fā)展的過程中發(fā)揮著關(guān)鍵作用。混合信號設(shè)計將模擬與數(shù)字電路無縫集成至一個 SoC 上,為用戶提供了顯著的性能、尺寸和能效優(yōu)勢。

從廣義上講,混合信號集成電路是指結(jié)合了模擬與數(shù)字功能的集成電路(IC),不僅指這些域之間的接口,還指同時包含模擬和數(shù)字功能的組件的集成電路。它的應(yīng)用范圍涵蓋了電源管理系統(tǒng)、用戶接口(如觸覺反饋),以及手機、筆記本電腦充電器、游戲控制器和 GPS 系統(tǒng)中找到的射頻應(yīng)用。

合二為一

模擬系統(tǒng)和數(shù)字系統(tǒng)屬于不同的開發(fā)領(lǐng)域,開發(fā)工具和方法論也各不相同。數(shù)字設(shè)計工程師使用 Verilog、SystemVerilog 和 VHDL 等硬件描述語言(HDLs),以及數(shù)字邏輯仿真器和硬件仿真器進行創(chuàng)建和驗證他們的設(shè)計。而模擬設(shè)計工程師則使用 SPICE 或 FastSPICE 等專業(yè)仿真器來分析和驗證模擬組件。盡管數(shù)字設(shè)計工程師和模擬設(shè)計工程師都是專業(yè)人士,但他們都對對方領(lǐng)域的技術(shù)了解有限,如建模語言、仿真器和仿真技術(shù)。

混合信號設(shè)計旨在將這兩個獨立系統(tǒng)集成為一個 SoC 上的整體。要實現(xiàn)這一目標,就必須進行全面的系統(tǒng)驗證,以確保系統(tǒng)功能正常。

設(shè)計驗證

數(shù)字驗證(DV)工程師通常使用以下先進工具和方法進行設(shè)計驗證,其中包括通用驗證方法學(UVM)、SystemVerilog 斷言(SVA)、統(tǒng)一電源格式(UPF)和度量驅(qū)動驗證(MDV)。這些工具和方法助力 DV 工程師生成測試激勵、評估覆蓋率、調(diào)試設(shè)計并無縫地運行回歸測試。

然而,如何將這些技術(shù)擴展應(yīng)用于模擬領(lǐng)域,以實現(xiàn)全面驗證呢?雖然可以通過連接模擬與數(shù)字仿真器來進行模擬混合信號(AMS)仿真,但大量的進程間通信會大幅降低仿真運行速度,使其比純數(shù)字驗證慢很多。因此,AMS 仿真不總是適用于執(zhí)行回歸測試和 MDV 流程等任務(wù)。

驗證的局限性

DV 工程師采用的傳統(tǒng)解決方案是創(chuàng)建簡單的存根模型(stub model)來隔離任何模擬和混合信號單元的數(shù)字部分,而不是運行 AMS 仿真。

借助存根模型,工程師可專注于數(shù)字部分的一維驗證。然而,模擬工程師與數(shù)字工程師關(guān)于模擬-數(shù)字接口方面的看法分歧可能導致一些可以避免的工作失誤,進而導致設(shè)計失敗或代價高昂的硅片返工。此類工作失誤包括引腳連接錯誤、極性反轉(zhuǎn)、總線排序不當以及電源域連接錯誤。

實數(shù)建模(RNM)解決方案

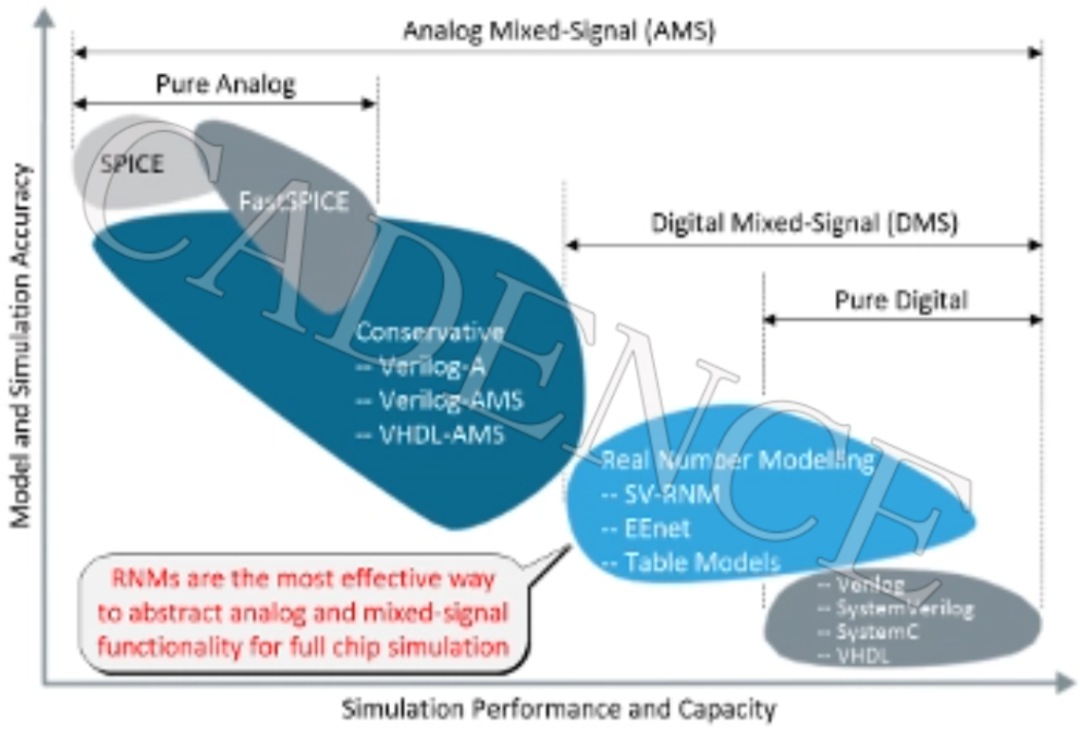

實數(shù)建模借鑒了模擬和數(shù)字仿真領(lǐng)域的理念。最重要的是,實數(shù)模型使用 DV 工程師熟悉的語言,例如 SV-RNMs 中使用的 SystemVerilog 語言。如下圖 1 所示,該模型可使 DV 工程師使用邏輯仿真器和硬件仿真器進行數(shù)字混合信號(DMS)驗證。

圖 1:混合信號仿真的模型和仿真精度 vs. 性能與容量

DV 工程師可利用 RNMs 能夠創(chuàng)建處理多于二態(tài)的模型,這些模型可以使用復雜的數(shù)學公式和實數(shù)值(如 3.142 或 16.893)。例如,DV 工程師可設(shè)計一個簡化的 RNM,即模擬數(shù)字轉(zhuǎn)換器。通過使用 RNM,工程師可以避免模擬電路中的許多復雜難題,只需專注于實數(shù)輸入和整數(shù)輸出即可。

此外,通過用 SystemVerilog 實現(xiàn) RNM,DV 工程師可以利用熟悉的語言對混合信號接口進行細致和精確的建模,這不僅能提高驗證流程的效率和精度、彌合模擬與數(shù)字領(lǐng)域之間的鴻溝,還使得在混合信號場景下應(yīng)用 UVM 和功能覆蓋成為可能。

值得注意的是,RNM 的應(yīng)用范圍十分廣泛,不僅能用于電路模型,還能用于旋轉(zhuǎn)和振動檢測傳感器,以及激光與光子處理器之間的的接口建模。

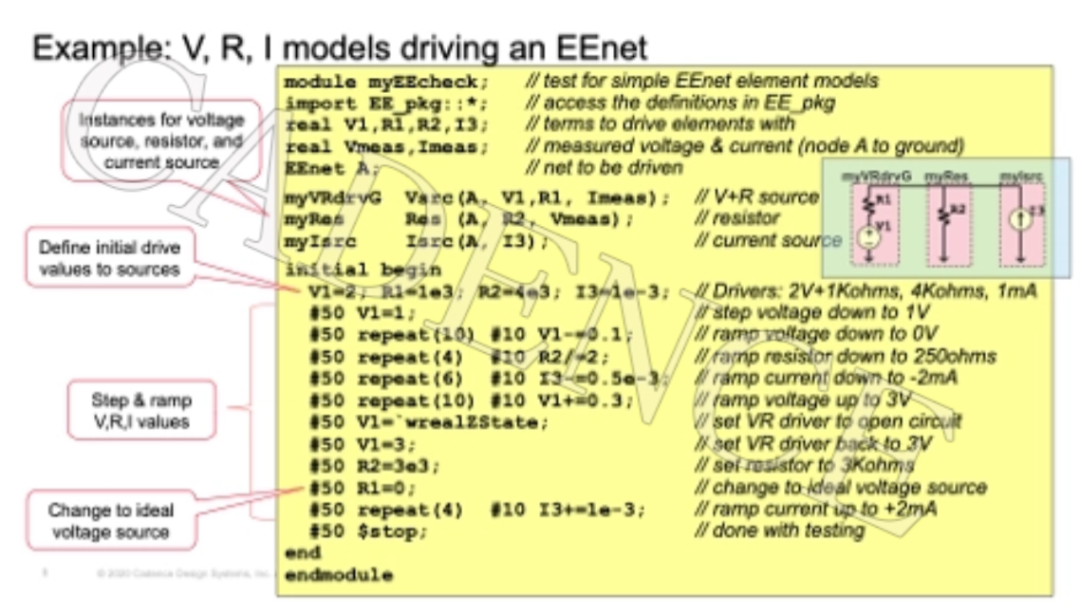

EEnet

在多數(shù)情況下,DV 工程師通常希望提高具體模擬和混合信號功能仿真的逼真程度。Cadence 的 Xcelium 與 Xcelium Mixed-Signal App 結(jié)合,可提供一個定制的參數(shù)化 RNMs EEnet 庫,其中包含電阻、電感器、電容器、二極管、晶體管及運算放大器等 RNMs。DV 工程師可借助這些工具在 SystemVerilog 中精確構(gòu)建模擬電路模型。事實證明,EEnet 模型可以實現(xiàn)高達 5 倍的運行效率,而且與 SPICE 模型相比,在精確度方面與后者只有 0.5% 的差距。

圖 2:EEnet 模塊

結(jié)論

RNMs 可以通過 DMS 仿真或硬件仿真簡化數(shù)字領(lǐng)域的驗證流程,使驗證速度遠超過 AMS 驗證。同樣值得注意的是,DV 工程師使用的所有標準工具和技術(shù),如 UVM、SVA、UPF 和 MDV,均能夠兼容應(yīng)對設(shè)計中的模擬和混合信號問題。

總之,RNMs 可使 DV 工程師利用熟悉領(lǐng)域中的現(xiàn)有資源進行高效而全面的混合信號驗證。

-

集成電路

+關(guān)注

關(guān)注

5409文章

11771瀏覽量

365314 -

半導體

+關(guān)注

關(guān)注

335文章

28142瀏覽量

227101 -

混合信號

+關(guān)注

關(guān)注

0文章

487瀏覽量

65146 -

Cadence

+關(guān)注

關(guān)注

65文章

942瀏覽量

143170 -

數(shù)字電路

+關(guān)注

關(guān)注

193文章

1635瀏覽量

81204

原文標題:利用實數(shù)建模簡化混合信號驗證流程

文章出處:【微信號:gh_fca7f1c2678a,微信公眾號:Cadence楷登】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

工程師不得不懂的MCU混合信號驗證策略和挑戰(zhàn)

基于FPGA的混合信號驗證流程

關(guān)于功能驗證、時序驗證、形式驗證、時序建模的論文

第32章 實數(shù)FFT的實現(xiàn)

Saber軟件功率MOSFET自建模與仿真驗證

求一種有限元分析中PCBA的簡化建模方法

簡單介紹一下數(shù)模混合信號建模語言Verilog-AMS

基于FPGA的混合信號驗證流程

CadMOS Simplex構(gòu)建簡化的信號完整性流程

混合信號FPGA的智能型驗證流程

混合信號示波器電源測試基本流程

評論