一、ISP算法及架構分析介紹

ISP即Image Signal Processor,是一種圖像處理架構,不是我們用的下載器。

ISP其實算是圖像處理的一個特例,一般應用于前端設備(相對于SENSOR),從結果上看就是將RAW數據轉換成壓縮后的RGB(一般)數據,供后續CPU使用(識別、壓縮等)。

市面上很少有直接介紹ISP的書籍或者資料,今天我們主要是聊一聊ISP算法的架構,這樣大家就能明白為什么很少有專用的書籍對這方面進行介紹了。

二、ISP算法介紹

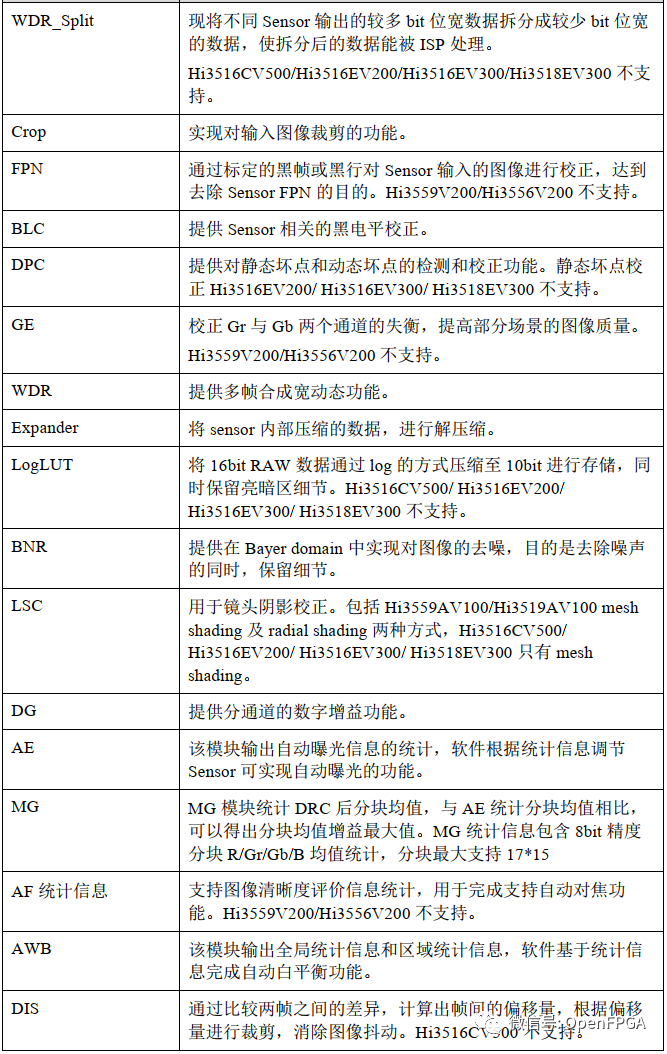

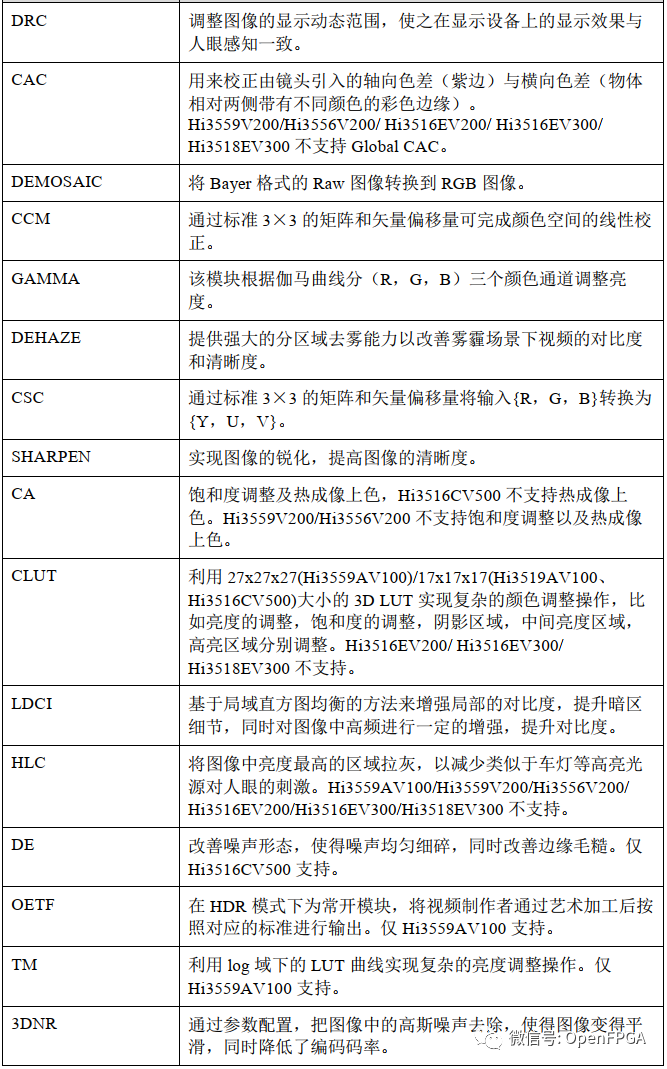

ISP是一類算法統稱,這一類算法通常包含下列算法:

三、海思架構

海思IC是國內很成熟的芯片了,其針對前端的芯片也是在業內廣受好評,我們先看看海思內部的ISP架構(Hi3559A為例,其他芯片有功能增減)。

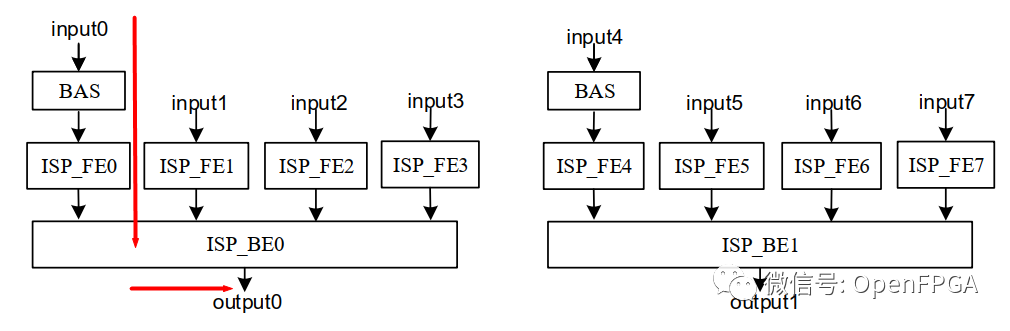

Hi3559A(下稱3559A)ISP的整體結構如下:

ISP 整體結構圖(Hi3559AV100)

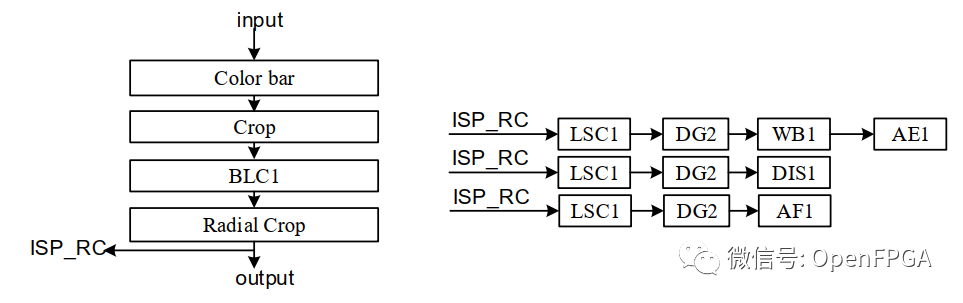

因為3559A是個多攝像頭輸入的SoC,所以有多路ISP集合,我們只關心最左邊紅線線路。繼續拆分,下圖是ISP FE架構(上圖中的ISP_FE0):

ISP_FE 結構圖(Hi3559AV100)

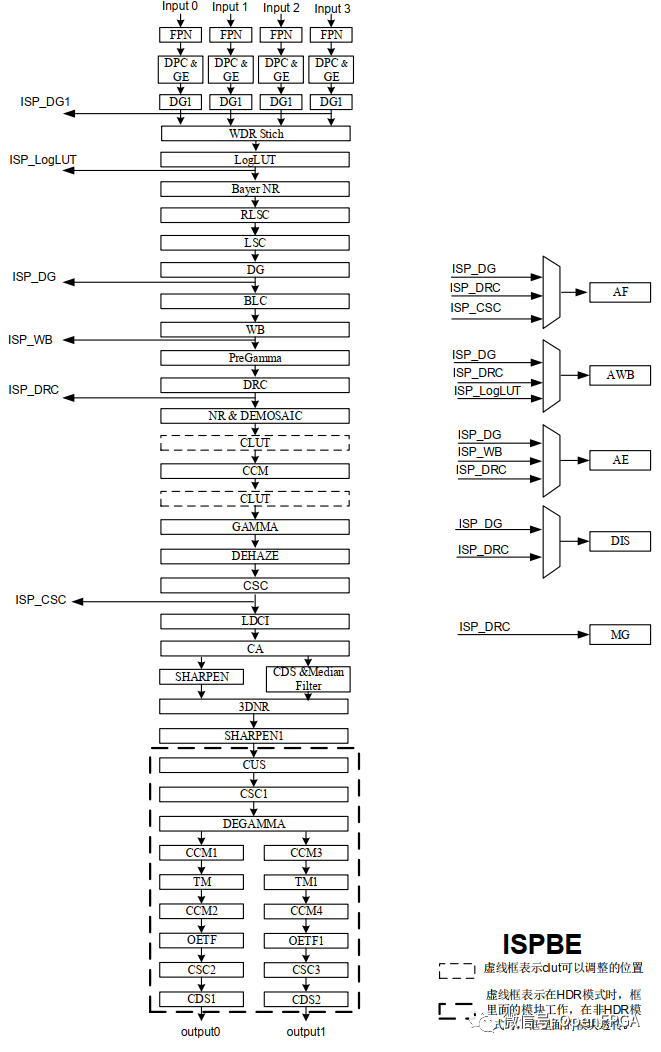

下圖是ISP BE結構圖:

ISP_BE 結構圖(Hi3559AV100)

圖中 CSC1,CSC2,CSC3 功能和 CSC 一致。

圖中 OTEF1 功能和 OETF 一致。

圖中 DG1,DG2 功能和 DG 一致。

圖中 CCM1, CCM2, CCM3, CCM4 功能和 CCM 一致。

圖中 TM1 功能和 TM 一致。

圖中 CD1,CDS2 功能和 CDS 一致。

圖中 AF1 功能和 AF 一致。

圖中 AE1 功能和 AE 一致。

圖中 DIS1 功能和 DIS 一致。

圖中 LSC1 功能和 LSC 一致。

圖中 WB1 功能和 WB 一致。

圖中 SHARPEN1 功能和 SHARPEN 一致。

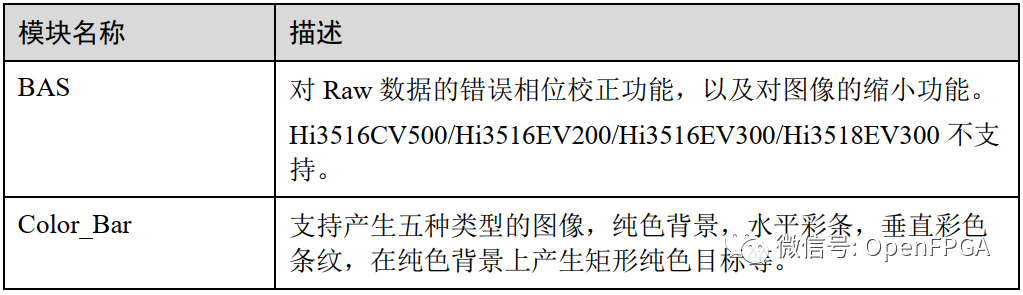

上面都是一些專用術語的縮寫,所以接下來簡單介紹一下這些縮寫:

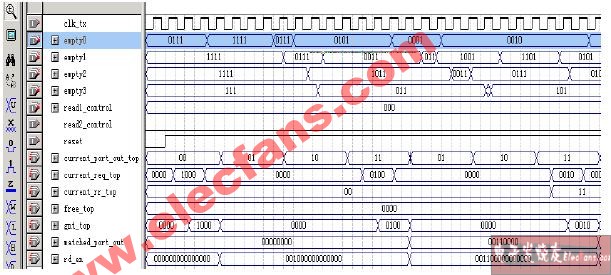

ISP 術語簡介(Hi3559AV100)

上圖中是一些術語簡介,因為一些特殊原因只能截圖,請忽略一些特殊的字符。源文檔會在文末提供(只用于學習,切勿商用)。

3559A是一個通用ISP,所以功能很全,如果用FPGA去實現這些,估計沒有幾個能做出來,ISP的特殊點就是針對不同的鏡頭、環境、Sensor等不同去調整需要實現的算法。

上面的介紹只是一個開頭,只是想讓大家知道ISP主要包含哪些算法以及一些專用術語(建議保存),下面才開始我們的介紹,用FPGA實現ISP的通用架構分析。

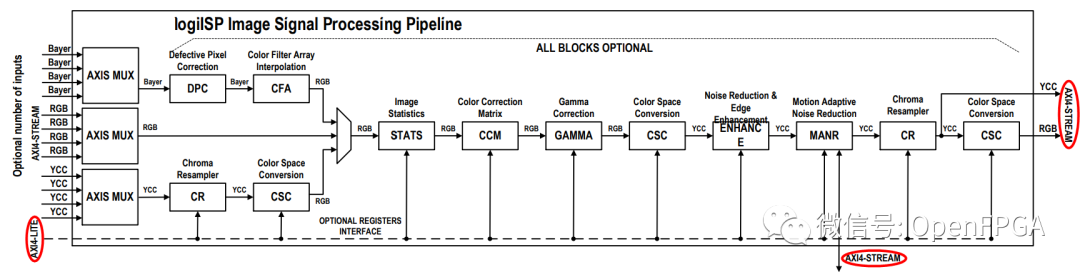

四、利用AXI總線實現ISP通用架構

在Xilinx FPGA中AXI總線應用的比較多,尤其針對多模塊互聯的情況,下面給出一個Xilinx FPGA使用的較通用的ISP架構:

Xilinx FPGA ISP 整體結構示意圖

所有的算法串行運行,利用AXI-lite總線進行管理,這樣可以大大增加系統的靈活性(后續調參方便),至于內部算法需要針對自己應用選配,按照目前的架構可以很方便的進行增加或者減少算法種類。

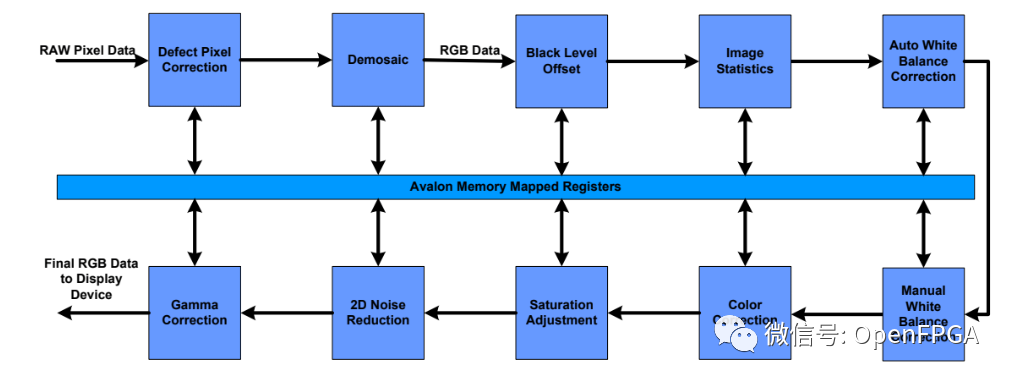

五、利用Avalon總線實現ISP通用架構

利用Avalon總線和上一節的AXI總線效果一樣,功能一樣。

其中3A算法的實現也有多種方式實現,可以直接FPGA內部硬件實現,也可以在外面放置單片機實現,最通用的可能就是內部MicroBlaze/Nios去管理也大大減少了開發難度。

六、總結

因為ISP算法的特殊性,很少有專用書籍去介紹這一類知識,但是今天帶領大家了解一下通用架構后大家應該就可以根據自己的需求去找自己系統里需要的算法知識就可以了。

同時上面針對Xilinx或者Intel廠家FPGA的ISP架構,只是一個通用算法架構示意圖,每個公司都有自己的架構,也有全HDL實現的方案,只不過不適合我們本篇文章去解析。

最后還是說明一下,ISP中所有的算法都是圖像算法,大家需要先學習圖像算法,同時切記一定要使用一些高級語言先驗證自己的算法再去轉換成HDL,而不是直接上來就是我先實現個“ISP”。

-

FPGA

+關注

關注

1641文章

21912瀏覽量

611754 -

架構

+關注

關注

1文章

525瀏覽量

25795 -

ISP算法

+關注

關注

0文章

3瀏覽量

6394

原文標題:?ISP算法及架構分析介紹

文章出處:【微信號:FPGA研究院,微信公眾號:FPGA研究院】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

TI電機模塊算法資料大全(39個算法分析)

量化算法介紹及其特點分析

SVPWM算法架構介紹

ISP和IAP介紹和比較

基于變長交換的ISP算法

介紹幾個關于ISP算法架構的項目

CMOS圖像傳感器的ISP算法

自動駕駛算法軟件架構介紹

開源ISP(Infinite-ISP)介紹

評論