本篇主要討論Vivado中DDRX控制器(mig)ip核配置中關(guān)于命令序號(hào)選擇和地址映射說(shuō)明(一)

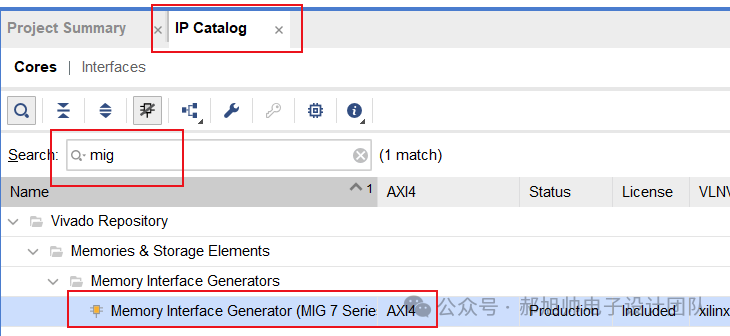

利用Xilinx 7系列FPGA開(kāi)發(fā)時(shí),經(jīng)常需要驅(qū)動(dòng)外部存儲(chǔ)器--DDRX。Xilinx提供了mig(存儲(chǔ)器接口生成器)這個(gè)ip用以驅(qū)動(dòng)外部存儲(chǔ)器。

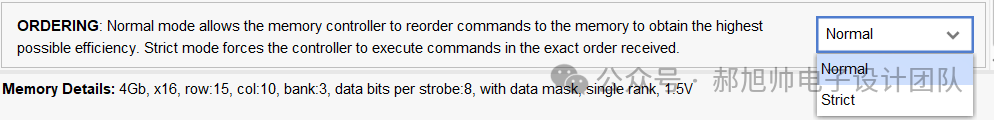

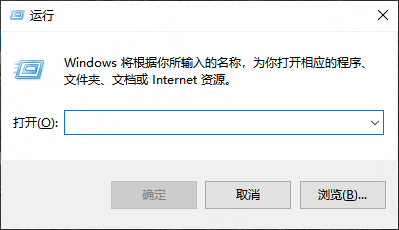

在配置中有一項(xiàng)命令序號(hào)模式的選擇:

mig這個(gè)ip可以接收多個(gè)命令(在第一個(gè)命令還沒(méi)有執(zhí)行時(shí),就可以接收后續(xù)的幾個(gè)命令。并不是接收一個(gè)命令,執(zhí)行完后才可以接收下一個(gè)命令)。

上述選擇兩個(gè)模式的區(qū)別為:

正常模式允許存儲(chǔ)器控制器重新編序收到的命令的順序,以或者更高的性能(例:收到的命令順序?yàn)锳1,A2,A3,但是發(fā)現(xiàn)按照A1,A3,A2的順序執(zhí)行,不妨礙功能,并且擁有更高的性能)。

嚴(yán)格模式強(qiáng)制要求控制器按照收到的命令順序去執(zhí)行。

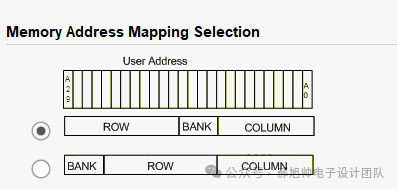

在配置時(shí),還有一項(xiàng)地址映射模式選擇:

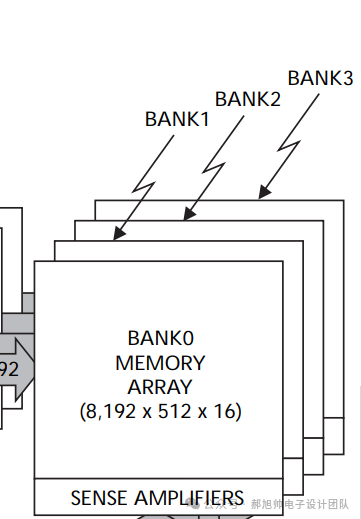

DDRXSDRAM是一種按照M行,N列湊成一個(gè)片(BANK),然后多個(gè)片構(gòu)成的一個(gè)存儲(chǔ)器。在使用時(shí)需要提供BANK地址,行地址,列地址,才能夠指定對(duì)應(yīng)的訪問(wèn)位置(特別注意:每個(gè)位置存儲(chǔ)一個(gè)字(需要看存儲(chǔ)器的寬度),并不是一個(gè)字節(jié)(8個(gè)bit))。

注:此圖為SDR SDRAM的內(nèi)部結(jié)構(gòu)圖,只為方便理解。

在使用mig時(shí),我們需要提供一個(gè)地址,那么這個(gè)地址的各個(gè)位對(duì)應(yīng)的DDRX SDRAM的bank地址,行地址,列地址的模式是按照上述選擇的。

例:(不考慮RANK地址),假設(shè)行地址13位,列地址10位,BANK地址3位,無(wú)論我們選擇哪一種模式,我們的地址都是給一個(gè)26位的地址。如果選擇ROW,BANK,COL的模式,那么地址的25:13位會(huì)給到行地址,12:10會(huì)給到BANK地址,9:0會(huì)給到列地址。如果選擇BANK,ROW,COL的模式,那么地址的25:23位會(huì)給到BANK地址,22:10會(huì)給到行地址,9:0會(huì)給到列地址。

那么這兩個(gè)地方我們應(yīng)該選擇哪個(gè)呢?

這個(gè)和內(nèi)部結(jié)構(gòu)以及工作原理有關(guān)系,并且也和我們平時(shí)使用的方式 有一定的關(guān)系。

內(nèi)部結(jié)構(gòu)在上述已經(jīng)簡(jiǎn)單的敘述過(guò)了,下面簡(jiǎn)述一下工作原理:

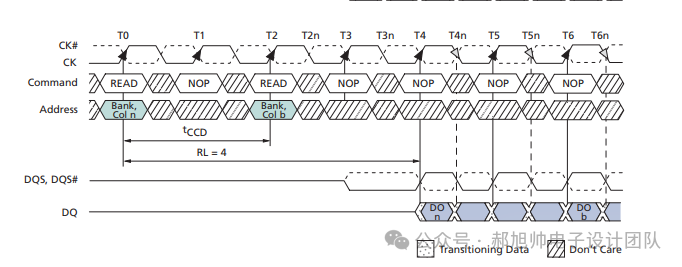

在訪問(wèn)時(shí),我們首先需要激活訪問(wèn)地址對(duì)應(yīng)的BANK里面的對(duì)應(yīng)的那一行,然后才可以進(jìn)行讀寫(xiě)。

下面給出SDRAM中的幾個(gè)特性:

· 在SDRAM中某一行激活了,是需要關(guān)閉的(有時(shí)間的限制)。

·在SDRAM中如果第二個(gè)操作和第一個(gè)操作是同一個(gè)bank,同一行,那么第一個(gè)操作完成后,可以不關(guān)閉此行,第二個(gè)操作也不用激活,此時(shí)提高了訪問(wèn)效率。

. 在SDRAM中同一個(gè)BANK只能激活一行。例:如果第二個(gè)操作和第一個(gè)操作是同一個(gè)bank,但是不同行,那么就只能將第一個(gè)操作的行關(guān)閉,然后再將第二個(gè)行激活。

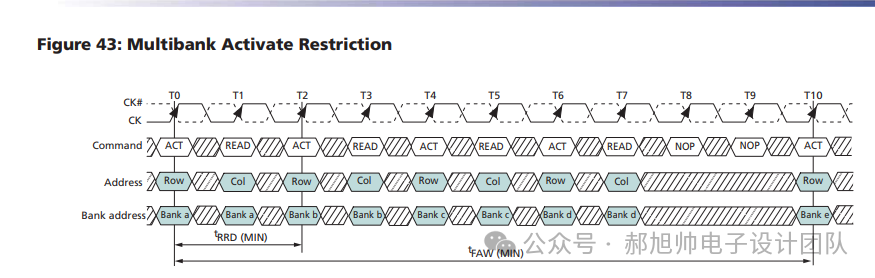

. 在SDRAM中,不同的BANK是可以同時(shí)激活使用者想要訪問(wèn)的行。例:如果第二個(gè)操作和第一個(gè)操作不在同一個(gè)bank,那么就可以在關(guān)閉第一個(gè)操作對(duì)應(yīng)的bank的同時(shí),激活第二個(gè)操作對(duì)應(yīng)的BANK,那么此時(shí)相當(dāng)于節(jié)省了一段時(shí)間,提高了訪問(wèn)的效率。

知道了這幾個(gè)特性,我們來(lái)考慮上述的兩個(gè)選擇項(xiàng)的問(wèn)題:

首先考慮命令是否允許重新編號(hào);假設(shè)第一個(gè)操作為BANK A,ROW A,第二個(gè)操作為BANK A, ROW B, 第三個(gè)操作為BANK A, ROW A。如果按照嚴(yán)格順序執(zhí)行,那么只能夠進(jìn)行激活、操作一,關(guān)閉,激活、操作二、關(guān)閉、激活、操作三、關(guān)閉。共需要九步完成所有的命令。如果把操作二和操作三對(duì)調(diào),那么將執(zhí)行激活、操作一、操作三、關(guān)閉、激活、操作二、關(guān)閉。共需要七步即可完成,提高了一定的效率,所以此選項(xiàng)建議選擇正常模式。

下面考慮地址映射的選項(xiàng):

這個(gè)需要考慮一個(gè)使用者的方式:一般我們使用時(shí),是一段連續(xù)的地址;例:0到10000。

如果選擇BANK,ROW,COL的模式,就是利用第一個(gè)bank的第一行,然后第二行,第三行,········, 直到第一個(gè)bank利用完畢,才可以利用下一個(gè)bank。

如果選擇ROW,BANK,COL的模式,就是利用第一個(gè)bank的第一行,完事后,利用第二個(gè)bank的第一行,然后是第三個(gè)bank的第一行····直到所有的bank的第一行全部利用完事后,才會(huì)利用第二行。

那么在當(dāng)一行利用完畢時(shí),BANK,ROW,COL的模式下一個(gè)用的是第二行就必須等第一行關(guān)閉后,才可以激活第二行。如果選擇ROW,BANK,COL的模式下一個(gè)用的是其他的bank的行,所以不需要等待關(guān)閉就可以激活,相當(dāng)于節(jié)省了一段時(shí)間,提高了訪問(wèn)效率。

-

FPGA

+關(guān)注

關(guān)注

1629文章

21748瀏覽量

603954 -

控制器

+關(guān)注

關(guān)注

112文章

16384瀏覽量

178352 -

地址映射

+關(guān)注

關(guān)注

0文章

6瀏覽量

2064

原文標(biāo)題:Vivado中DDRX控制器(mig)ip核配置中關(guān)于命令序號(hào)選擇和地址映射說(shuō)明(一)

文章出處:【微信號(hào):HXSLH1010101010,微信公眾號(hào):FPGA技術(shù)江湖】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

開(kāi)疆智能Ethernet/IP轉(zhuǎn)Profinet網(wǎng)關(guān)連接納博特控制器配置案例

快速上手:設(shè)備IP地址配置技巧與注意事項(xiàng)

怎么綁定IP地址和MAC地址

Vivado中FFT IP核的使用教程

恒訊科技分析:香港服務(wù)器centos修改ip地址的方法有哪些?

IP地址小分享

Vivado中DDRX控制器(mig)ip核配置中關(guān)于命令序號(hào)選擇和地址映射說(shuō)明

Vivado中DDRX控制器(mig)ip核配置中關(guān)于命令序號(hào)選擇和地址映射說(shuō)明

評(píng)論