以下文章來源于Cadence楷登PCB及封裝資源中心,作者Cadence

本文要點

3D 集成電路從平面工藝發(fā)展而來,創(chuàng)造了具有多個特征層的多層半導(dǎo)體封裝。

3D 集成電路主要在三個方面具有優(yōu)勢,分別是功耗、信號時序和混合信號集成。

3D 集成是異構(gòu)集成的基礎(chǔ),將更多不同的功能整合到一個單一的封裝中。

3D 集成電路的優(yōu)勢有目共睹,因此現(xiàn)代芯片中也使用了 3D 結(jié)構(gòu),以提供現(xiàn)代高速計算設(shè)備所需的特征密度和互連密度。隨著越來越多的設(shè)計集成了廣泛的功能,并需要一系列不同的特征,3D 集成將與異構(gòu)集成逐漸融合,將不同的芯片設(shè)計整合到一個單一的封裝。本文將概述3D 集成電路的優(yōu)勢,以及它們?nèi)绾沃ξ磥淼南冗M(jìn)設(shè)備實現(xiàn)異構(gòu)集成。

1 3D 集成電路的結(jié)構(gòu)

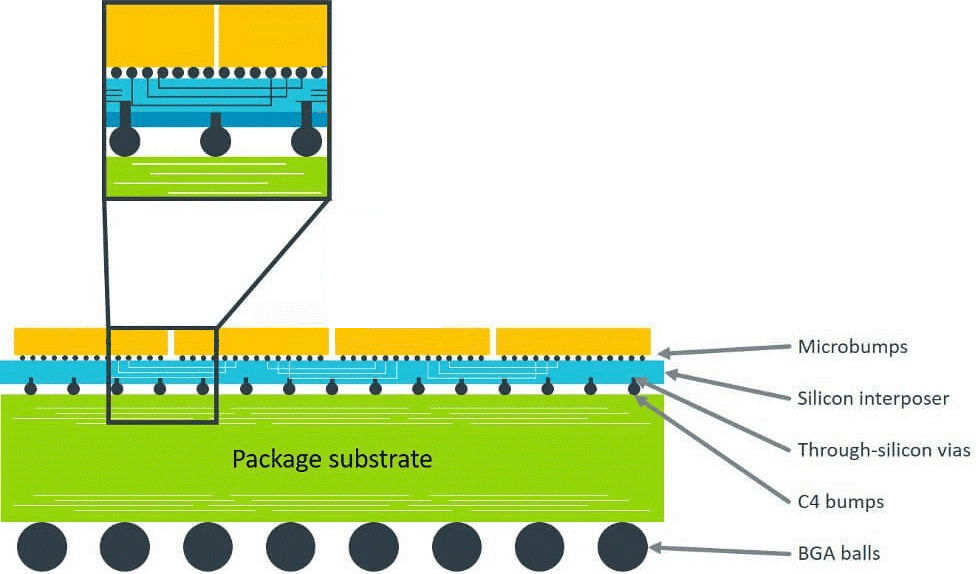

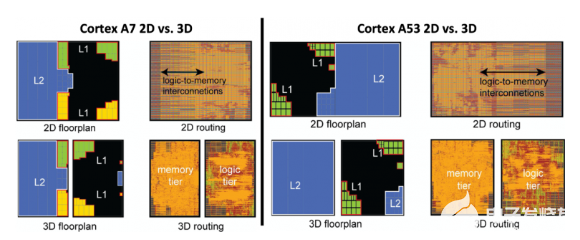

在 VLSI 設(shè)計中,3D 集成電路的一般結(jié)構(gòu)相對簡單,如下圖所示。在這種類型的系統(tǒng)中,集成電路是通過將特征層堆疊在一起而構(gòu)成的。通過垂直堆疊單個裸片/晶圓層,在兩個電路之間傳遞電信號所需的連接長度就會縮短。這種更短的互連造就了 3D 集成電路的優(yōu)勢。

3D 集成電路的結(jié)構(gòu);圖片來源:ARM

2 3D 集成電路的四大優(yōu)勢

功耗更低

自 20 世紀(jì) 90 年代末以來,為了降低功耗,設(shè)計人員開始縮小封裝尺寸,采用新穎的互連設(shè)計。在某種程度上,在集成電路中縮小封裝尺寸的唯一方法是以 3D 方式堆疊設(shè)計。

縮短互連長度可以降低功耗,因為互連長度上的直流電阻損耗較低。這一點非常重要,因為設(shè)計已經(jīng)擴(kuò)展到更小的技術(shù)節(jié)點,需要更薄的互連和更大的直流電阻。

信號轉(zhuǎn)換更快

由于在這些設(shè)計中使用了較短的互連,垂直互連的總電容比水平互連的要小。這意味著互連中的信號將具有較低的 RC 時間常數(shù),可以在接通和斷開狀態(tài)之間進(jìn)行更快的轉(zhuǎn)換。

此外,由于總的寄生電容較低,互連上的信號延遲也較低,確保了開關(guān)從輸入到輸出的傳播速度。得益于這些因素,數(shù)字信號的串行數(shù)據(jù)速率更快。

3D 集成可以將模擬和數(shù)字電路塊集成到同一個封裝中,減少了信號完整性問題,而且不會大幅度增加封裝尺寸。在這些封裝中,數(shù)字和模擬模塊可以通過平面排列的方式彼此分開。

盡管如此,在不過度增加封裝尺寸的情況下,仍然可以在垂直方向上為每個模塊添加更多的功能。通過將模塊隔離到各自的區(qū)域內(nèi),更容易控制串?dāng)_和噪聲耦合,在設(shè)計中不會產(chǎn)生重大的信號問題。

節(jié)省空間

最后,由于封裝尺寸更小,最明顯的優(yōu)勢是可以節(jié)省空間。垂直堆疊的 3D 集成電路可以做到非常薄,與將電路模塊分散在半導(dǎo)體裸片的廣闊空間內(nèi)相比,3D 集成頗具優(yōu)勢。

因此,更多的元件和功能可以整合在一塊 PCB 上,實現(xiàn)密度更高的設(shè)計和高級封裝。

盡管這些封裝很實用,在信號完整性方面也有優(yōu)勢,但仍需要使用仿真工具來確保設(shè)計按預(yù)期運行。在電路層面,通過 SPICE 仿真來評估可靠性,并通過場求解器應(yīng)用來進(jìn)行物理布局和封裝層面的仿真。先進(jìn)的封裝應(yīng)采用多物理場分析方法,以評估熱可靠性。集成電路設(shè)計師最好能在原型設(shè)計前發(fā)現(xiàn)封裝問題,并盡早優(yōu)化設(shè)計。

3 異構(gòu)集成的未來發(fā)展

2019 年,三家 IEEE 協(xié)會(電子封裝協(xié)會、光子學(xué)會和電子器件協(xié)會)共同發(fā)布了異構(gòu)集成路線圖 (Heterogeneous Integration Roadmap,即HIR) 。該路線圖規(guī)定了異構(gòu)集成系統(tǒng)的性能基準(zhǔn),其中多個電路和器件集成到一個半導(dǎo)體封裝中。此類設(shè)計是真正的系統(tǒng)級封裝 (systems-in-package,即SiP),其中多個半導(dǎo)體裸片器件集成到同一個封裝內(nèi)。

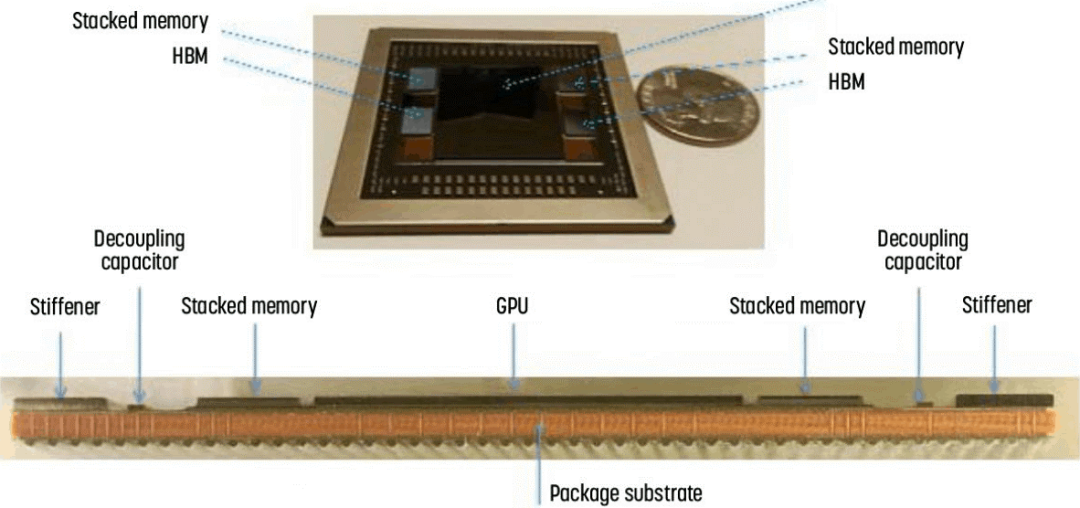

AMD Fiji GPU 中使用的異構(gòu)架構(gòu);圖片來源:Design007,2020 年 10 月刊

這種新形式的 IC 設(shè)計看起來和 PCB 設(shè)計工程師在電路板上所做的工作一樣。這些器件已經(jīng)利用了 3D 集成的優(yōu)勢,即多個 3D 集成電路被組合并連接到同一個封裝中。集成電路設(shè)計師可以采取更加模塊化的方式進(jìn)行半導(dǎo)體設(shè)計,將不同裸片上的多個器件用硅基板、玻璃基板或在晶圓上作為單片集成電路集成到同一封裝中。

實現(xiàn)這種模塊和功能集成主要歸功于硅通孔 (through-silicon via,即 TSV)。最早在中介層上用 TSV 實現(xiàn)芯片堆疊的器件之一是 CMOS 成像傳感器。TSV 被用來通過傳感器上的中介層形成互連,以連接片上讀出電路。高速計算處理器可以采用類似的封裝方式;這方面的第一個例子是 AMD 的 Fiji GPU(見上文),該產(chǎn)品已于 2017 年發(fā)布,使用 TSV 中介層將內(nèi)存和圖形處理器集成在一個封裝中。

隨著封裝技術(shù)越來越先進(jìn),這種類型的集成預(yù)計將繼續(xù)發(fā)展完善。芯片、裸片-晶圓/裸片-裸片結(jié)構(gòu)和多芯片模塊都體現(xiàn)了現(xiàn)代集成電路中的 3D 集成和更大的特征密度。

如果想為專門的應(yīng)用開發(fā)更先進(jìn)的器件,設(shè)計師將繼續(xù)采用帶有異構(gòu)集成的 3D 設(shè)計方法。如果想在設(shè)計中實現(xiàn) 3D 集成電路的所有優(yōu)勢,可以使用 Cadence 的全套系統(tǒng)分析工具。VLSI 設(shè)計師可以將多個特征模塊集成到新的設(shè)計中,并定義連接,實現(xiàn)持續(xù)集成和擴(kuò)展。強大的場求解器提供全套軟件仿真功能,與電路設(shè)計和 PCB 布局軟件集成,打造完整的系統(tǒng)設(shè)計工具包,適用于各類應(yīng)用和各種復(fù)雜程度的設(shè)計。

-

集成電路

+關(guān)注

關(guān)注

5388文章

11547瀏覽量

361805 -

3D

+關(guān)注

關(guān)注

9文章

2878瀏覽量

107535 -

封裝

+關(guān)注

關(guān)注

126文章

7901瀏覽量

142951 -

異構(gòu)集成

+關(guān)注

關(guān)注

0文章

34瀏覽量

1890

原文標(biāo)題:技術(shù)博客 I 3D-IC 和異構(gòu)集成的優(yōu)勢

文章出處:【微信號:gh_fca7f1c2678a,微信公眾號:Cadence楷登】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

音樂集成電路的結(jié)構(gòu)及基本工作原理

3D集成電路如何實現(xiàn)

3D集成電路的結(jié)構(gòu)和優(yōu)勢

3D集成電路的結(jié)構(gòu)和優(yōu)勢

評論