CMOS 工藝技術平臺的電容包括 MIM 和 PIP (Poly Insulator Poly)。PIP 主要應用在0.35μm及以上的亞微米及微米工藝技術,MIM 主要應用在0.35μm 及以下的深亞微米工藝技術,納米工藝技術會用到 MOM(Metal Oxide Metal),本節內容沒有講述 MOM。它們的測試結構版圖尺寸是依據工藝技術平臺的設計規則設計的。

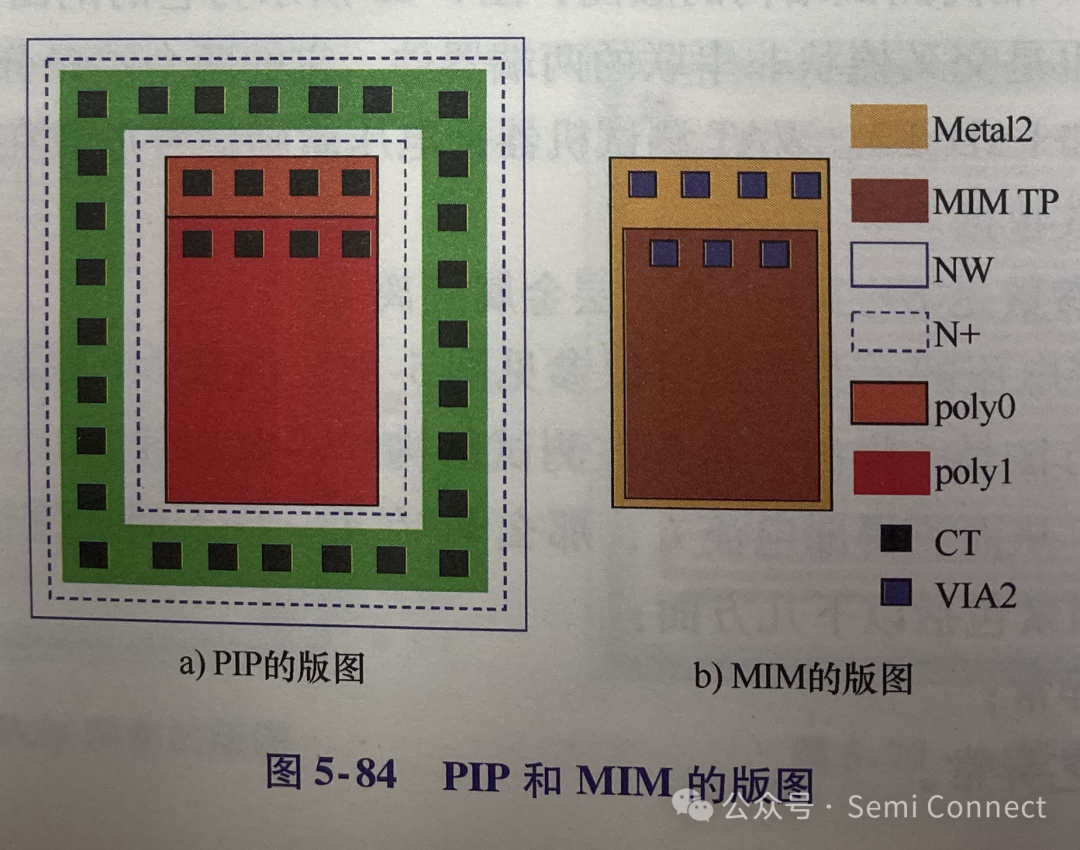

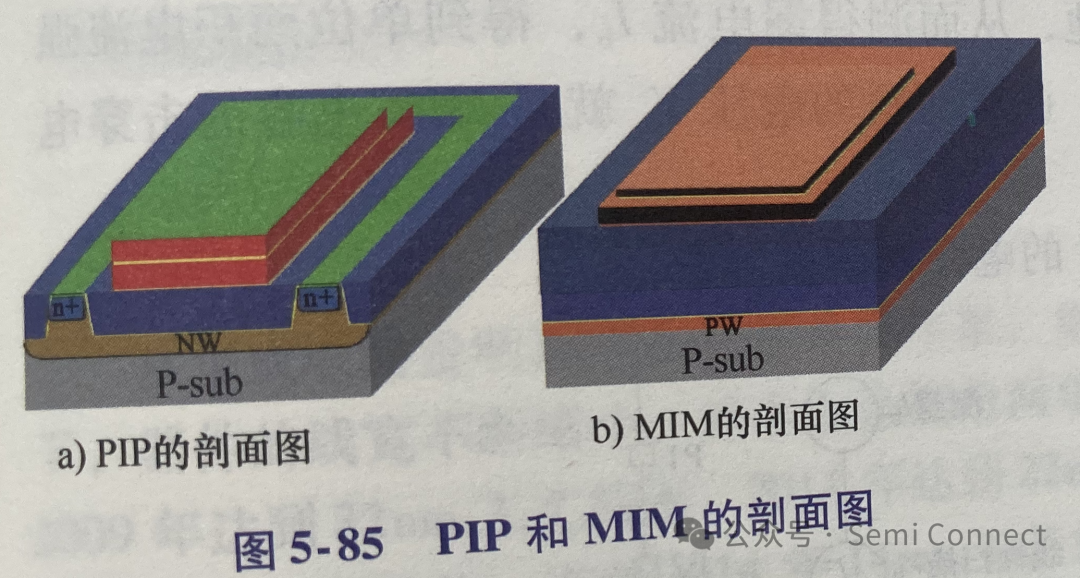

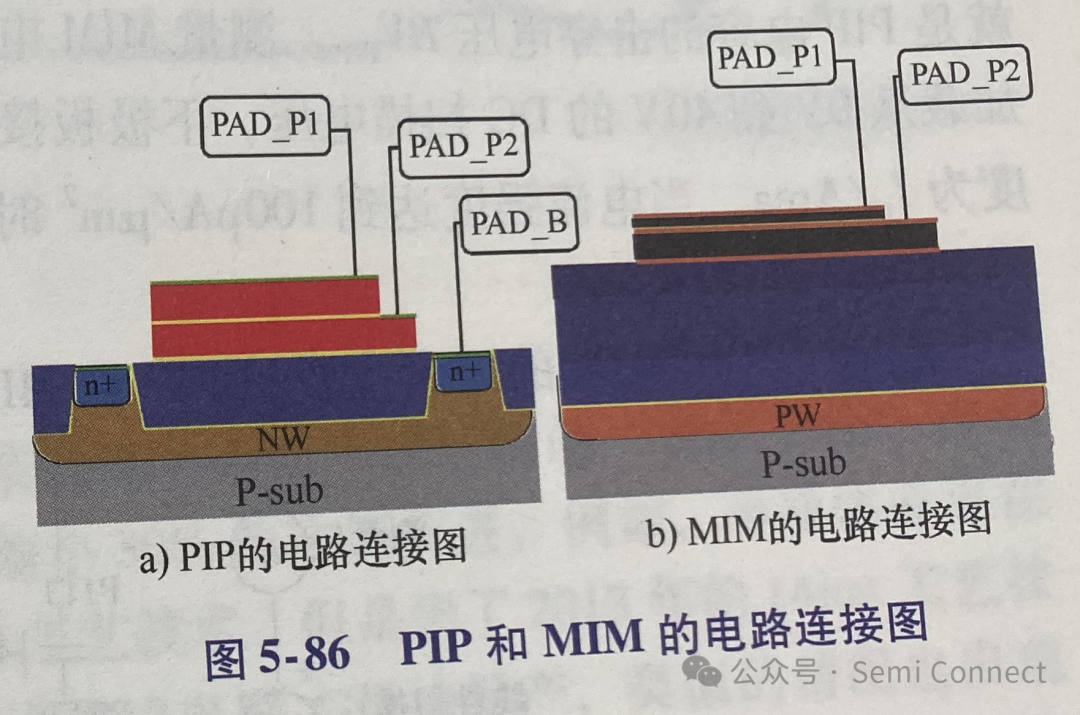

圖5-84所示為 PIP 和 MIM 的版圖,圖5-85所示為它們的剖面圖,圖5-86所示為它們的電路連接圖,它們的兩個端口是上極板(Top)和下極板(Bottom)分別連接到 PAD_P1和PAD_P2。為了更好地與襯底隔離,PIP測試結構是設計在NW里,NW連接到PAD_B,PAD_B接地。襯底對 MIM 的影響非常小,把MIM 測試結構設計在PW里,WAT測試機器通過上極板和下極板這兩個端口把電壓激勵信號加載在 MIM 和 PIP,從而測得所需的電性特性參數數據。

MIM和 PIP電容是設計混合信號電路的重要器件,它們的準確性嚴重影響電路性能,芯片代工廠通過兩個 WAT 參數監測MIM 和PIP,這兩個 WAT 參數分別是電容C和擊穿電壓BV。

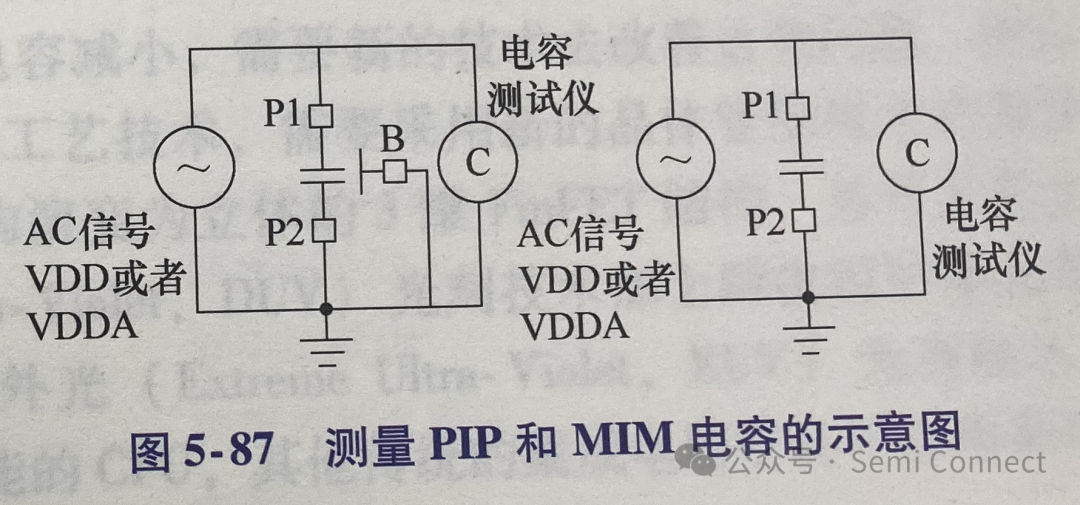

測量 MIM和 PIP 電容的基本原理與測量MOS 晶體管器件柵極氧化層電容類似,它的基本原理是在電容的上極板加載100kHz掃描電壓,下極板接地,從而測得電容C,Cjun=C/Area,Area 是電容的面積。

圖5-87所示測量MIM 和PIP 電容的電路示意圖,左邊是測量PIP 電容的電路示意圖,右邊是測量 MIM 電容的電路示意圖。PIP 電容的測量方法是在電容的上極板加載AC 100kHz(VDD 或者 VDDA)掃描電壓,下極板和襯底接地。MIM 電容的測量方法是在電容的上極板加載 AC 100kHz(VDD或者 VDDA)掃描電壓,下極板接地。分別測得它們的電容C,那么單位面積的電容CPIP或者CMIM= C/Area."

影響MIM 和PIP 的因素包括以下兩方面:

1)PIP 和MIM的刻蝕尺寸異常;

2) PIP 和MIM 的電介質厚度異常。

-

CMOS

+關注

關注

58文章

5718瀏覽量

235494 -

電容

+關注

關注

100文章

6045瀏覽量

150327 -

工藝

+關注

關注

4文章

593瀏覽量

28790 -

晶體管

+關注

關注

77文章

9692瀏覽量

138178

原文標題:電容的測試條件-----《集成電路制造工藝與工程應用》 溫德通 編著

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

詳解電容的測試條件

詳解電容的測試條件

評論