引言

人工智能(AI)和機器學習(ML)技術的需求正以驚人的速度增長,遠超摩爾定律的預測。自2012年以來,AI計算需求以每年4.1倍的速度指數增長,為半導體制程縮放和集成帶來重大挑戰。為應對這些需求,業界采用了基于Chiplet的設計方法,將較大系統分解為更小、更易于管理的組件,這些組件可以分別制造并通過先進封裝技術進行集成[1]。

先進封裝技術

先進封裝技術可以大致分為2D、2.5D和3D方法。2.5D集成技術,包括晶圓級芯片堆疊(CoWoS)和集成扇出型封裝(InFO),在高性能計算應用中獲得了顯著發展。

圖1:臺積電3D Fabric技術組合,展示了包括CoWoS、SoIC和InFO平臺在內的各種封裝選項,滿足不同集成需求。

CoWoS技術提供三種主要變體:

1. CoWoS-S:采用硅中介層實現密集金屬布線

2. CoWoS-R:在有機中介層中使用重布線層

3. CoWoS-L:結合-R和-S兩種方案的優勢

InFO平臺已從移動應用發展到高性能計算,提供多種選項,包括局部硅橋接和嵌入式去耦電容,以實現更好的供電性能。

芯片間互連應用

芯片封裝的演進帶來了各種凸點間距縮放選項,從傳統MCM封裝(110-130μm間距)到先進的2.5D封裝(40μm間距)和3D集成(9μm或更小間距)。

圖2:凸點間距縮放視角,展示了從MCM到先進封裝技術的演進,隨著間距減小帶寬密度不斷提高。

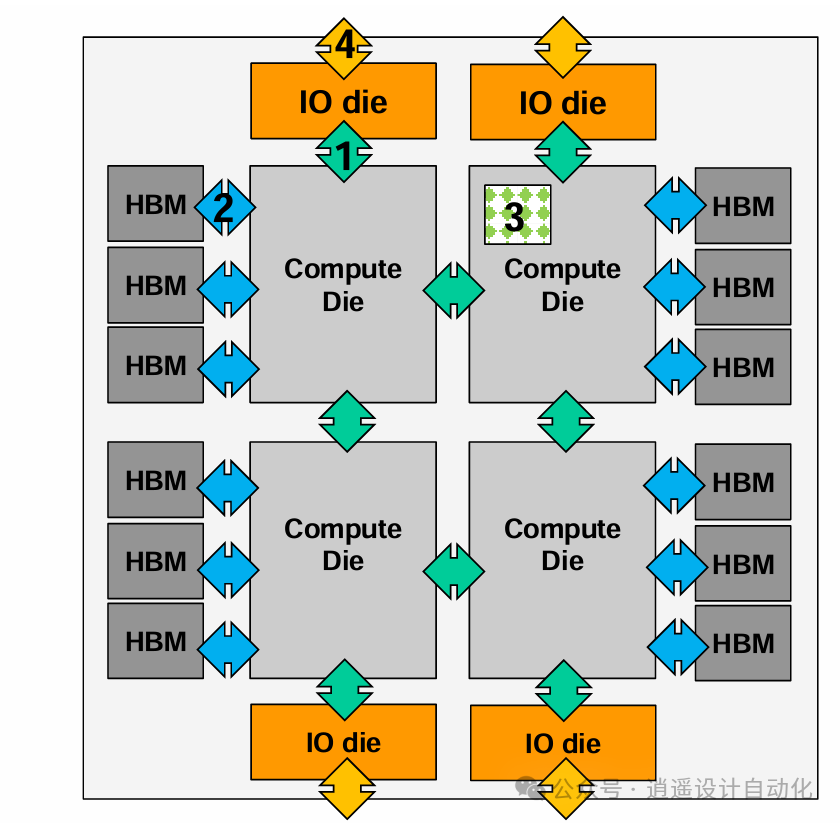

現代Chiplet系統中使用不同的互連技術服務于不同目的:

計算到計算及IO連接使用UCIe PHY

計算到內存連接使用HBM PHY

計算到SRAM連接通過3D堆疊實現

IO chiplet到外部IO使用XSR-SerDes

圖3:芯片間互連應用,展示了計算芯片、內存和IO組件之間的不同類型連接。

設計考慮和挑戰

通道優化在實現最佳信號完整性和可布線性方面發揮關鍵作用。設計人員必須平衡各種因素,包括介電層厚度、金屬間距、層厚度和過孔封裝規則。

圖4:通道可布線性和信號完整性優化,展示了中介層子部分設計和相應的信號完整性測量。

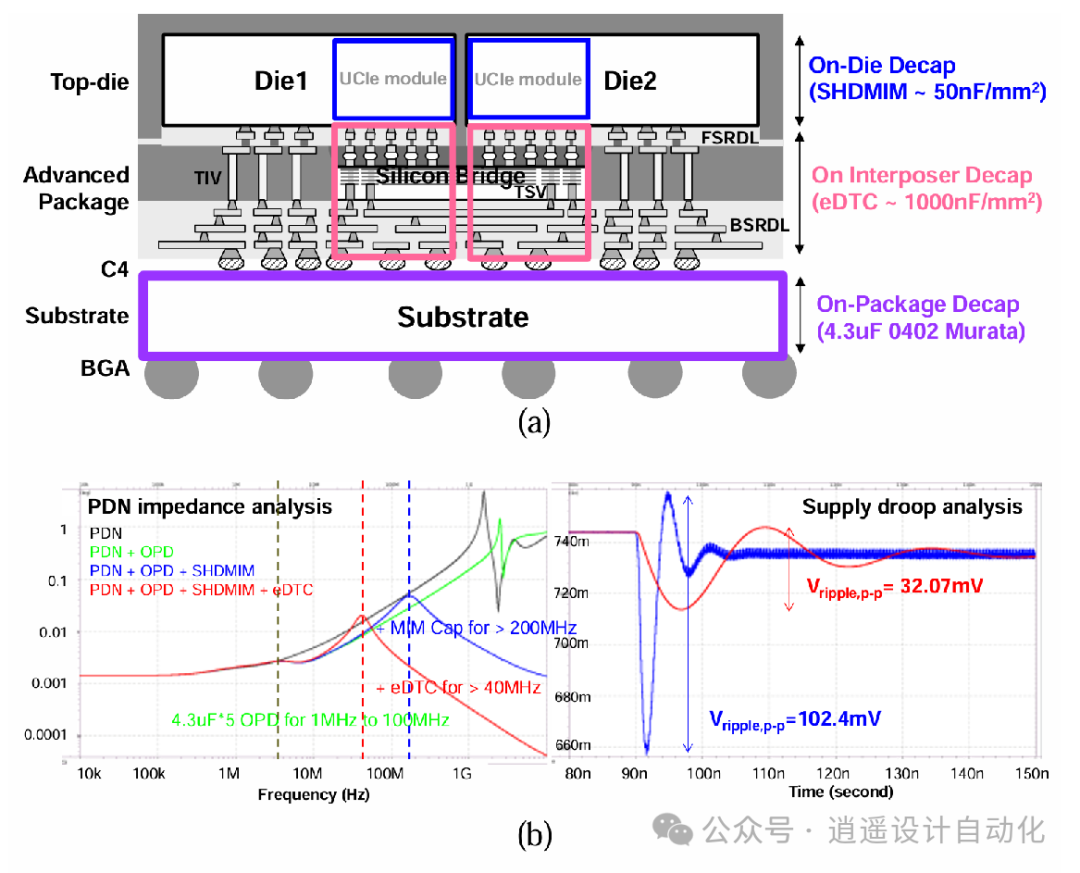

供電代表另一個關鍵挑戰,尤其是在電流密度不斷增加的情況下。現代解決方案包含多級去耦電容:

圖5:供電網絡的去耦電容策略,展示了不同類型電容及其在系統中的布置。

未來趨勢和發展

業界持續追求更高的帶寬密度和能源效率。技術制程縮放在實現這些改進方面發揮核心作用。

圖6:技術和帶寬縮放趨勢,展示了數據速率、凸點間距和制程節點之間的關系。

對于更大規模集成,晶圓級封裝變得越來越重要。這種方法允許超越傳統光罩尺寸限制的集成。

圖7:晶圓級系統擴展示意圖,展示了多個Chiplet和HBM內存在晶圓級系統中的集成。

結論

高帶寬Chiplet互連是下一代計算系統的核心技術。通過仔細考慮封裝技術、互連架構和設計優化,這些系統能夠為要求嚴格的AI和ML應用提供所需的性能。隨著行業不斷發展,供電、散熱和系統集成方面的新挑戰將推動該領域的進一步創新。

參考文獻

[1] S. Li, M. Lin, W. Chen and C. Tsai, "High-bandwidth Chiplet Interconnects for Advanced Packaging Technologies in AI/ML Applications: Challenges and Solutions," IEEE Open Journal of the Solid-State Circuits Society, 2024, doi: 10.1109/OJSSCS.2024.3506694

-

CoWoS

+關注

關注

0文章

154瀏覽量

10716 -

chiplet

+關注

關注

6文章

442瀏覽量

12721 -

先進封裝

+關注

關注

2文章

439瀏覽量

391

原文標題:TSMC | 高帶寬Chiplet互連的技術、挑戰與解決方案

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

晶圓測試的五大挑戰與解決方案

Chiplet技術革命:解鎖半導體行業的未來之門

Chiplet技術有哪些優勢

邊緣計算的技術挑戰與解決方案

UCIe規范引領Chiplet技術革新,新思科技發布40G UCIe IP解決方案

創新型Chiplet異構集成模式,為不同場景提供低成本、高靈活解決方案

西門子EDA創新解決方案確保Chiplet設計的成功應用

雙向4Tbps、兼容PCIe5.0!英特爾光學I/O chiplet再突破

高帶寬電源模塊消除高壓線路紋波抑制的干擾

評論