一、系統總體方案設計

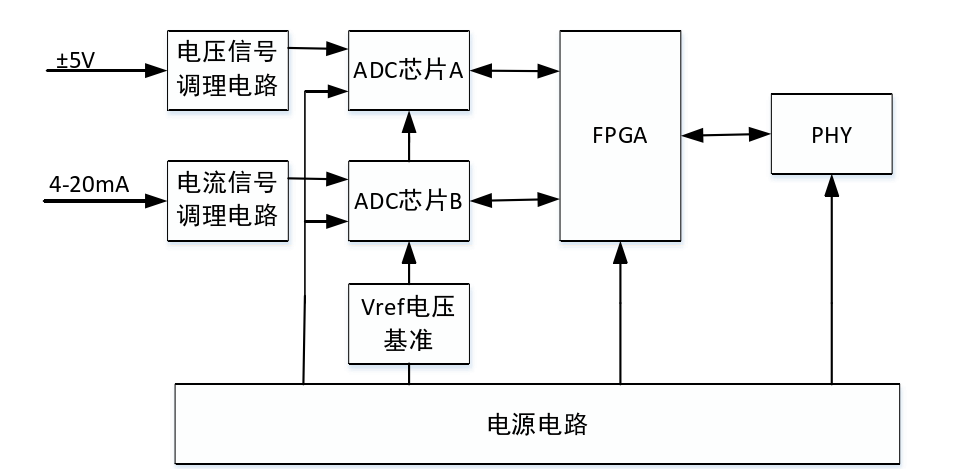

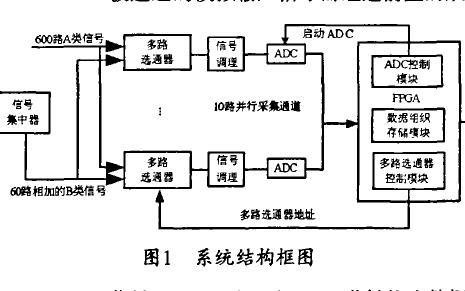

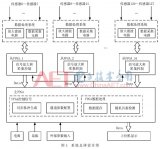

為了滿足油田增壓站對數據采集的需求,我們設計了一套基于FPGA的多通道數據采集與傳輸系統。系統以FPGA作為主控制器,利用外部ADC芯片完成模擬信號的采集,通過以太網實現與上位機的人機交互。

需求分析:油田增壓站的環境復雜,采集信號類型多樣,包括溫度、壓力、流量等模擬信號。系統需要實現對多通道信號的實時采集與傳輸,并具備較高的采集精度和穩定性。

系統架構:系統主要由FPGA、ADC芯片、以太網模塊和上位機軟件組成。FPGA負責系統的核心控制,包括信號采集、數據處理和數據傳輸。外部ADC芯片將模擬信號轉換為數字信號。通過以太網模塊,數據傳輸至上位機進行處理和顯示。

系統的總體設計流程如下:首先,外部傳感器將模擬信號輸入到ADC芯片中,FPGA通過SPI通信協議讀取ADC的數字信號,對數據進行濾波和組幀處理后,通過以太網發送至上位機。上位機軟件將接收到的數據進行解析和可視化顯示。

二、硬件電路設計與FPGA內部邏輯設計

1. 硬件電路設計

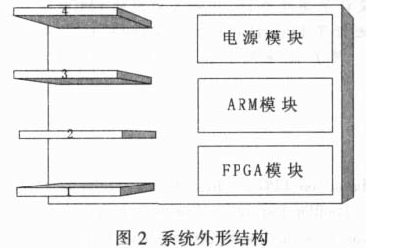

硬件電路設計是實現多通道數據采集傳輸的基礎,包括關鍵芯片的選型、原理圖設計和PCB布板。

關鍵芯片選型:

FPGA:選擇一款具有足夠I/O口、內存和處理能力的FPGA芯片。Altera Cyclone系列或Xilinx Spartan系列是常用的選擇,具有豐富的外圍接口資源和較高的性價比。

ADC芯片:選擇支持多通道輸入和高采樣速率的ADC芯片,如TI公司的ADS1256或Analog Devices的AD7606。這些芯片支持多通道同步采樣,具備較高的分辨率(24位)和采樣精度。

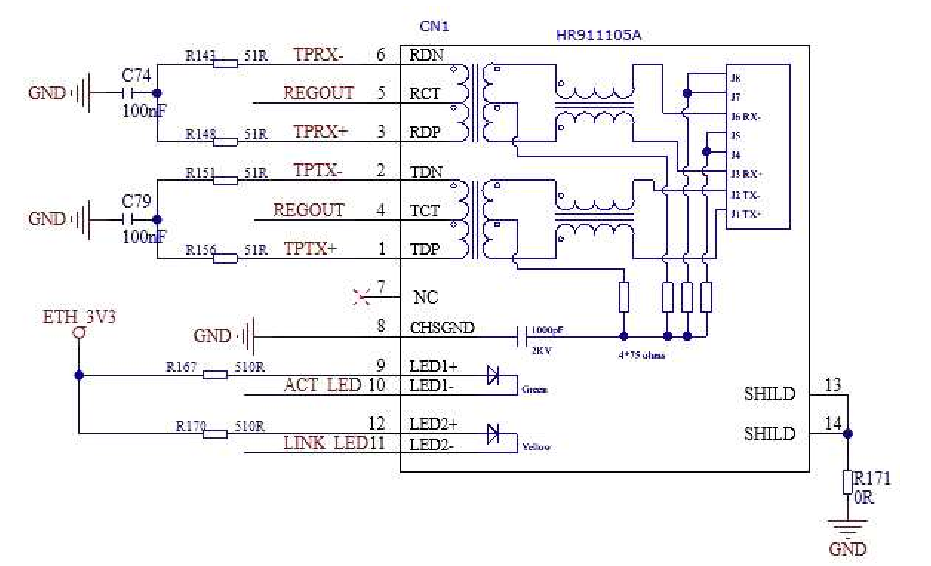

以太網模塊:選用常見的以太網PHY芯片,如Wiznet的W5500或Microchip的ENC28J60,實現以太網通信。

電路設計:

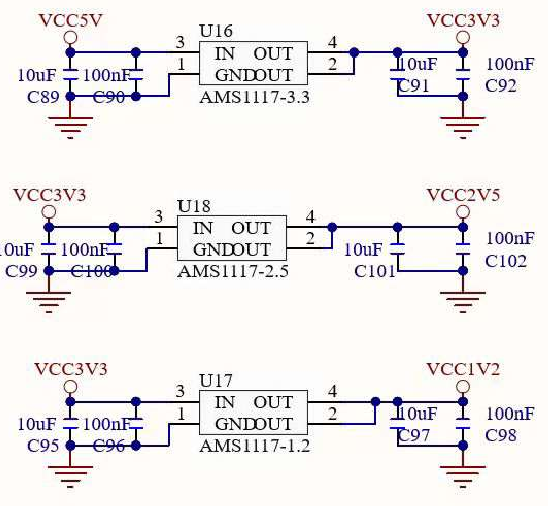

原理圖設計:根據功能需求繪制系統的原理圖,包括FPGA與ADC芯片的SPI接口電路、FPGA與以太網模塊的接口電路,以及電源管理和信號調理電路等。

PCB設計:完成原理圖設計后,進行PCB布局布線,確保高速信號傳輸的完整性和系統的穩定性。注意地線和電源的布置,避免噪聲干擾。

2. FPGA內部邏輯設計

FPGA內部邏輯設計是整個系統的核心,包括SPI通信模塊、數字濾波模塊和數據傳輸模塊。

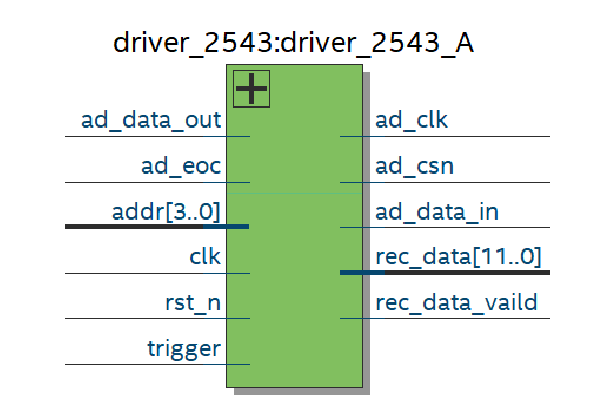

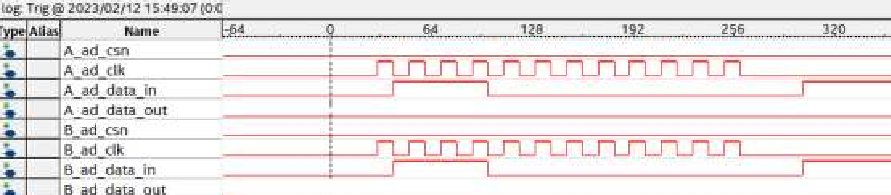

SPI通信模塊:FPGA通過SPI協議與ADC芯片通信,完成多通道數據的采集。設計一個支持SPI主機模式的模塊,用于控制ADC芯片的工作模式和數據讀取。該模塊包括SPI時鐘的生成、數據的發送與接收,以及片選信號的控制。

數字濾波模塊:為了減少現場高頻噪聲對采集數據的影響,在FPGA中實現了一個FIR數字濾波器。該濾波器對從ADC采集到的信號進行濾波處理,消除高頻噪聲,確保數據的準確性。FIR濾波器的設計需要根據系統的采樣率和信號特性選擇合適的濾波器系數,確保在不失真信號的情況下消除噪聲。

數據組幀與傳輸模塊:為了方便上位機識別采樣數據來自具體的設備和通道,對采集到的數據進行自定義組幀處理。每幀數據中包括通道標識、數據值和校驗信息等。組幀完成后,FPGA通過以太網模塊將數據發送至上位機。數據傳輸模塊采用UDP協議實現,確保數據的實時性和可靠性。

三、上位機軟件設計

為了實現數據的實時顯示和控制下位機的采集功能,設計了基于LabVIEW的上位機軟件。其主要功能包括:

數據采集控制:上位機通過以太網發送命令,控制FPGA實現數據采集的啟停。LabVIEW提供了豐富的網絡通信控件,可以方便地實現與下位機的交互。

數據解析與顯示:接收FPGA傳輸的數據,對數據進行解析,包括提取通道標識和采樣值。將解析后的數據轉換為波形曲線,并在上位機界面進行實時顯示。LabVIEW具有強大的圖形化界面設計功能,能夠直觀地呈現采集到的信號。

數據存儲與分析:除了實時顯示外,上位機還可以將采集到的數據存儲在本地文件中,供后續分析和處理。LabVIEW支持多種數據存儲格式,如文本文件、Excel文件等。

四、系統測試與性能驗證

為了驗證數據采集傳輸系統的功能完整性和可靠性,搭建了測試平臺對系統進行了全面測試。測試包括以太網數據傳輸的可靠性、采集數據的精度和系統整體功能。

以太網數據傳輸測試:測試以太網模塊的傳輸性能,驗證數據在傳輸過程中是否存在丟包或延遲等問題。實驗結果表明,系統的數據傳輸穩定,丟包率低于0.1%,傳輸延遲在可接受范圍內。

數據采樣精度測試:對系統的采樣精度進行測試,使用標準信號源向系統輸入已知信號,采集后與原始信號進行對比。實驗結果顯示,系統的采樣誤差在±0.1%以內,達到了設計要求的精度。

系統整體功能測試:包括從信號采集、數據傳輸到上位機顯示的完整流程測試。實驗中,上位機軟件能夠準確控制FPGA的采集啟停,并實時顯示采集到的信號波形。系統整體運行穩定,滿足數據采集、傳輸與顯示的功能需求。

// SPI通信模塊

module spi_master (

input clk,

input rst_n,

input start,

input [7:0] data_in,

output reg miso,

output reg sclk,

output reg cs_n,

output reg [7:0] data_out,

output reg done

);

reg [2:0] bit_cnt;

reg [7:0] shift_reg;

reg state;

// SPI時鐘產生

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

sclk <= 1;

end else begin

sclk <= ~sclk;

end

end

// SPI狀態機

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

cs_n <= 1;

bit_cnt <= 3'b0;

state <= 0;

done <= 0;

end else begin

case (state)

0: begin

if (start) begin

cs_n <= 0;

shift_reg <= data_in;

bit_cnt <= 3'b111;

state <= 1;

end

end

1: begin

if (bit_cnt == 3'b000) begin

state <= 2;

end else begin

sclk <= ~sclk;

if (sclk) begin

miso <= shift_reg[7];

shift_reg <= {shift_reg[6:0], 1'b0};

bit_cnt <= bit_cnt - 1;

end

end

end

2: begin

cs_n <= 1;

data_out <= shift_reg;

done <= 1;

state

-

FPGA

+關注

關注

1629文章

21736瀏覽量

603321 -

數據采集

+關注

關注

39文章

6100瀏覽量

113652 -

傳輸系統

+關注

關注

0文章

152瀏覽量

37187

原文標題:FPGA的多通道數據采集傳輸系統

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

基于FPGA的多通道數據采集系統設計

基于FPGA的多通道數據采集系統設計

如何使用FPGA進行超多通道高速數據采集系統的構成和設計過程資料概述

如何使用FPGA進行多通道同步數據采集系統的設計

FPGA的多通道數據采集傳輸系統

FPGA的多通道數據采集傳輸系統

評論