導讀

在電路設計中,為了降低成本而忽視ESD防護和隔離設計可能導致嚴重后果。本文將探討因不當添加元件而引發的電路問題,并逐一解析這些問題,提供實用的解決方案,以確保電路設計的可靠性和穩定性。

電路設計中,有的為了降低成本,沒有進行任何ESD防護和隔離設計,這是不行的,為了提高可靠性和穩定性,增加保護器件,或者增強驅動能力是常用方法。但稍有不慎,就有可能適得其反,在一些關鍵電路上,增加一些元件后,會帶來很大的負面影響:

- 如果添加的元件對電路時序產生了影響,這樣的器件最好不要加。

- 在總線時鐘信號線上增加了ESD保護器件,但器件選型沒做好容性控制,這樣會引起時鐘信號波形畸變,影響正常通信;

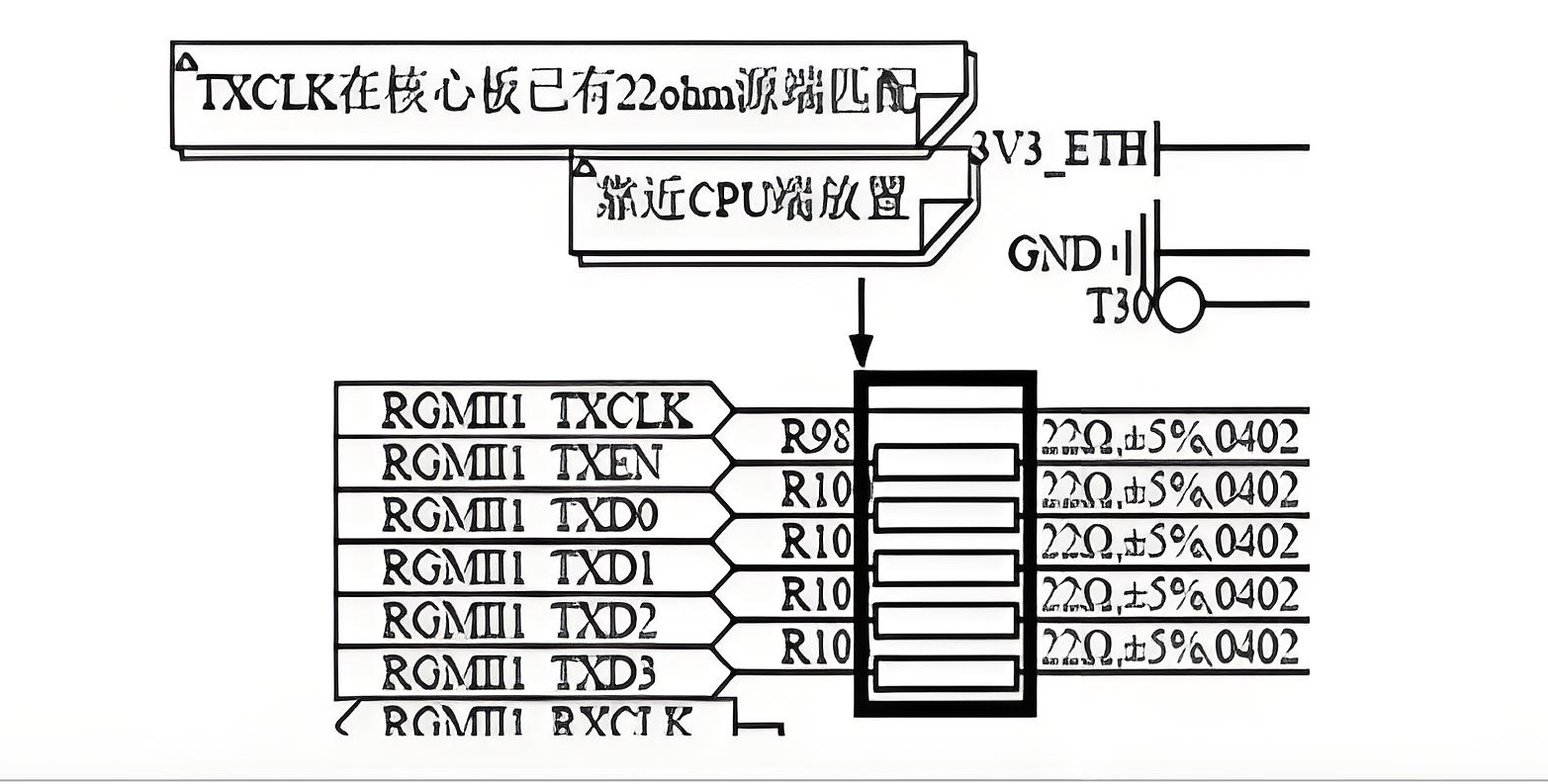

- 在總線源端加22Ω電阻也是常用設計手段,但這一定要考慮總線整體電路。如果核心板上已經放置了22Ω的電阻,則在底板上則不需要再串聯電阻,否則也會引起工作異常。

?開機階段閃屏

?開機階段閃屏

1. 現象描述

儀器設備在上電后在BootLoader和內核兩個階段出現閃屏現象。

先從軟件方面著手,通過延遲打開背光,但并未完全解決,通過示波器觀察,背光控制部分有明顯延遲。

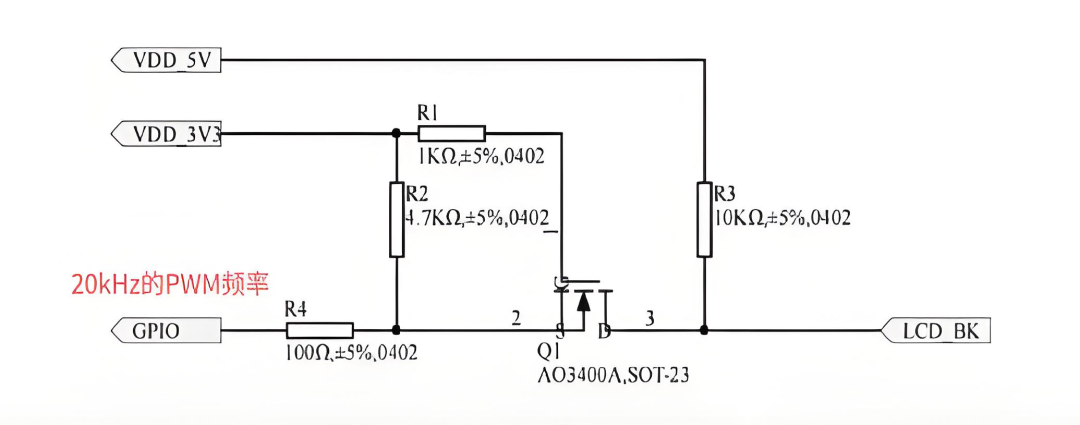

再從硬件著手分析,拿到的設備背光控制電路如圖1所示,通過示波器觀察,在設備上電時LCD_BK引腳會有一個高電平脈沖,之后維持低電平,最后階段為20KHz的PWM波。

圖1 客戶的LCD背光控制電路

2. 分析過程

根據以上現象基本可以判斷為上電時序問題,通過測量也可以發現VDD_5V早于VDD_3V3上電。當VDD_5V上電時,VDD_3V3未上電,系統沒有啟動,GPIO處于高組態,因此Q1的1、2引腳電平相同,Q1處于關斷狀態,LCD_BK信號會被R3拉高,導致背光被點亮,而當系統啟動后,GPIO會輸出低電平,控制背光關閉,由此出現屏閃現象。

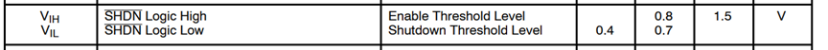

查看背光驅動芯片手冊,使能引腳高電平閾值為1.5V,如圖2所示,無需進行電平轉換,元件Q1是多余的,直接使用3.3V GPIO既可驅動。

圖2 使能引腳高電平閾值

3. 解決措施

去掉R1、R2、R3和Q1,并且把Q1的2、3引腳短接,設備上電啟動時不會再出現閃屏現象。

?TF卡無法識別

?TF卡無法識別

1. 現象描述

這現象比較常見于TF卡所有信號線都加上了ESD保護器件的情形,常見問題為ESD器件選型不正確。

2.分析過程

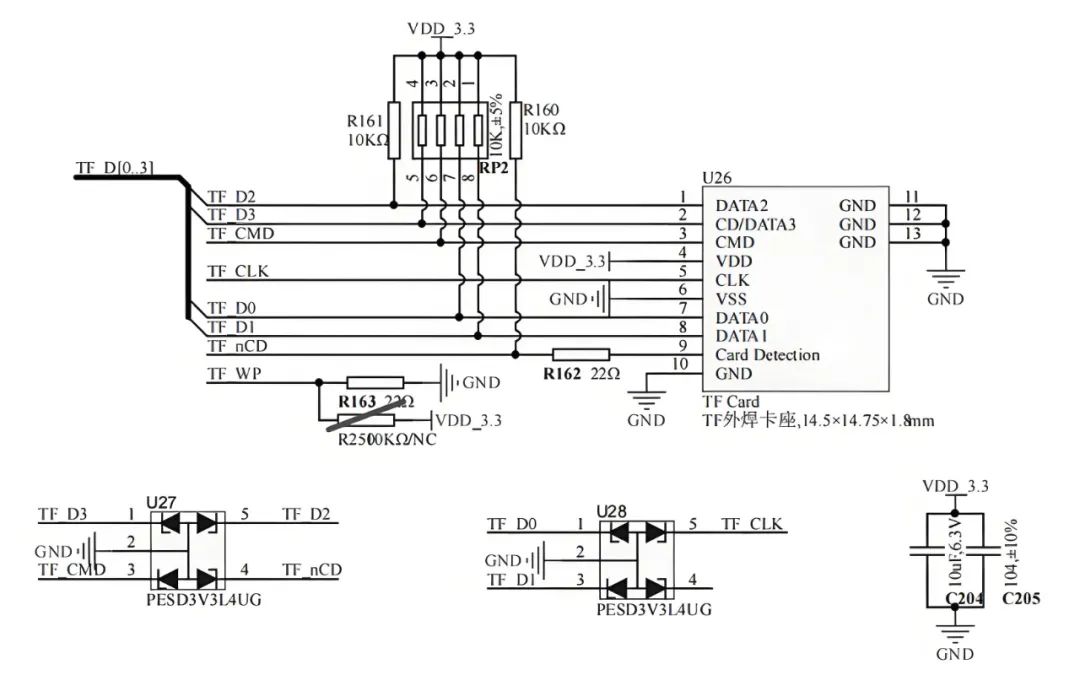

以圖3所示的原理圖為例進行分析。

圖3 TF卡一般電路圖

SD2.0對ESD器件寄生電容的要求為小于9pF,首先查看該ESD器件(PESD3V3L4UG)數據手冊,發現該ESD器件寄生電容最高可到28pF(參見圖 4),超過了SD2.0對寄生電容的要求。

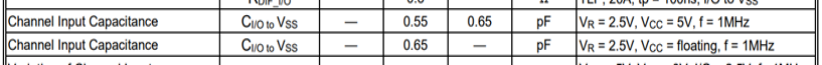

圖4 PESD3V3L4UG的寄生電容3. 解決措施斷開CLK線上的ESD器件,或者換用小寄生電容的DT1446-04S-7,該器件寄生電容僅為0.65pF(參見圖5),替換上去后TF卡正常識別。

圖5 DT1446-04S-7的寄生電容

?以太網匹配電阻

?以太網匹配電阻

1. 現象描述

核心板上以太網TX_CLK信號線已有22Ω的源端電阻,客戶在底板也加了22Ω的匹配電阻,引起以太網通信不穩定。

2. 分析過程

將同一塊核心板插到評估板上,以太網通信正常,基本定位是底板原因。而后檢查底板以太網電路原理圖,發現TX_CLK引腳串接了22Ω匹配電阻。而致遠電子官網給出的以太網參考電路里沒有加匹配電阻,顯然用戶沒有按照參考電路來設計。

圖6 新能源

3. 解決措施

將底板的22Ω電阻換為0Ω,以太網即可正常通信。

4. 總結

以太網PHY和處理器端的數據線和控制信號要注意阻抗匹配,避免信號反射。在設計原理圖時,一般建議源端串聯22~33Ω電阻。但是,部分核心板已經在源端串接匹配電阻,設計底板時就不需要串接匹配電阻。使用核心板開發新產品時,建議參考致遠電子官方硬件設計參考電路。

-

元器件

+關注

關注

112文章

4716瀏覽量

92303 -

嵌入式

+關注

關注

5082文章

19123瀏覽量

305150 -

電路設計

+關注

關注

6673文章

2453瀏覽量

204350 -

儀器設備

+關注

關注

1文章

104瀏覽量

10731

發布評論請先 登錄

相關推薦

求嵌入式linux學習筆記

如何在嵌入式操作系統ARM Linux中實現ZLG7290的驅動?

嵌入式系統筆記

嵌入式Linux驅動筆記--轉自風箏丶

從客戶需求視角去認識ZLG | 為用戶提供工業自動化及嵌入式領域生態產品

為何ZLG致遠電子要推出LGA嵌入式核心板?

ZLG嵌入式筆記(連載08) | 那些不能隨便添加的元器件

ZLG嵌入式筆記(連載08) | 那些不能隨便添加的元器件

評論