導讀

在電路設計中,電平匹配是一個基本要求,但常常被忽視,可能導致設備故障和通信異常。本文我們將揭示如何避免因電平不匹配導致的設備故障,并提供實用的設計建議,確保您的電路設計既高效又穩定。

電平匹配是進行電路設計時的一個基本要求,但有時候卻很容易被忽略,特別是沒有仔細查看外設或者芯片規格書的時候,根據以往經驗來設計,帶來了一些問題。這類問題只要在設計的時候稍加檢查就能被發現,下面的案例1和案例2都是因為沒有仔細看CAN隔離模塊的電氣特性引起的設計錯誤,其中案例2問題比較隱蔽,還涉及到不同溫度下電氣特性的變化:

MR6450外接5V CAN收發器,工作異常;

使用CAN收發器出現偶發性工作異常。

電平匹配在新處理器系統設計時越來越值得注意,現在很多處理器都分多個電平域,有的IO是3.3V,有的是1.8V。電平不匹配會工作不正常,還會帶來損壞IO的危險,例如產生電流倒灌而損傷IO口。

I2C電平匹配也是一個經常遇到的問題,下面我們將給出兩種不同方案供參考。

?TTL和CMOS電平參數定義

?TTL和CMOS電平參數定義

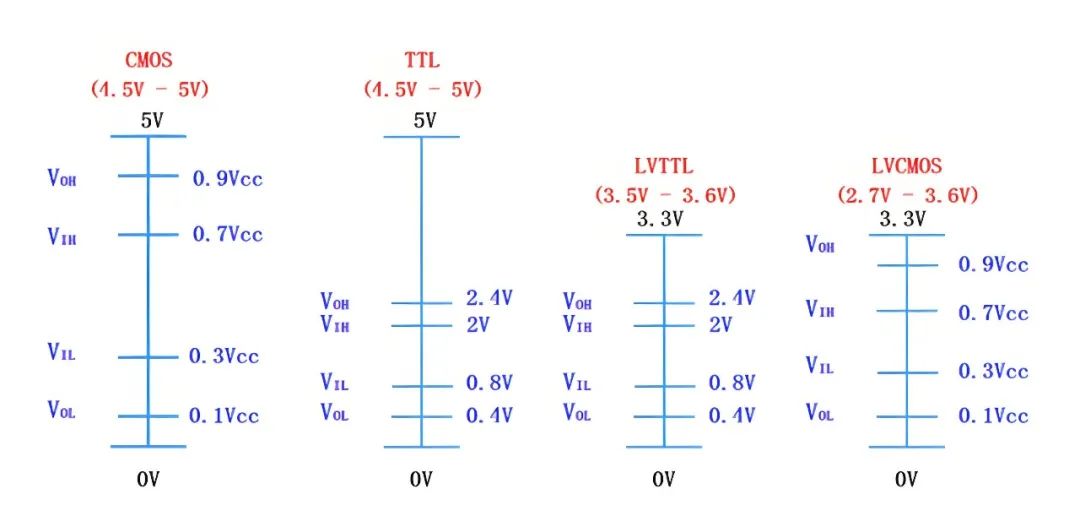

我們先看下TTL、CMOS邏輯電平參數定義,參考圖1。

圖1 TTL和CMOS邏輯電平定義

不同邏輯電平的兩個器件要想實現信號可靠傳輸的前提條件:

驅動器輸出的VOH(MIN)必須大于或等于接收器輸入的VIH(MIN)。

驅動器輸出的VOL(MAX)必須小于或等于接收器輸入的VIL(MAX)。

- 驅動器輸出的電壓不得超過接收器輸入的I/O電壓容差。

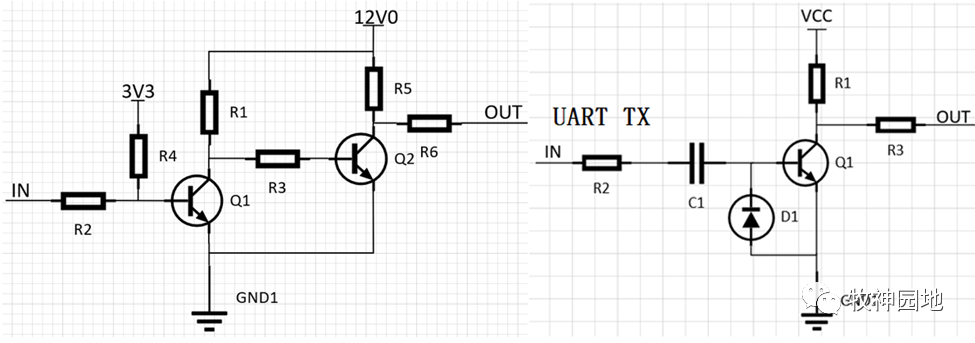

?案例1:MR6450的UART腳接到了5V的收發器

?案例1:MR6450的UART腳接到了5V的收發器

某客戶使用我司MR6450-L核心板通過UART通訊方式外接RS485模塊,無法正常工作,與客戶溝通后了解到客戶使用的RS485模塊邏輯電平為5V。

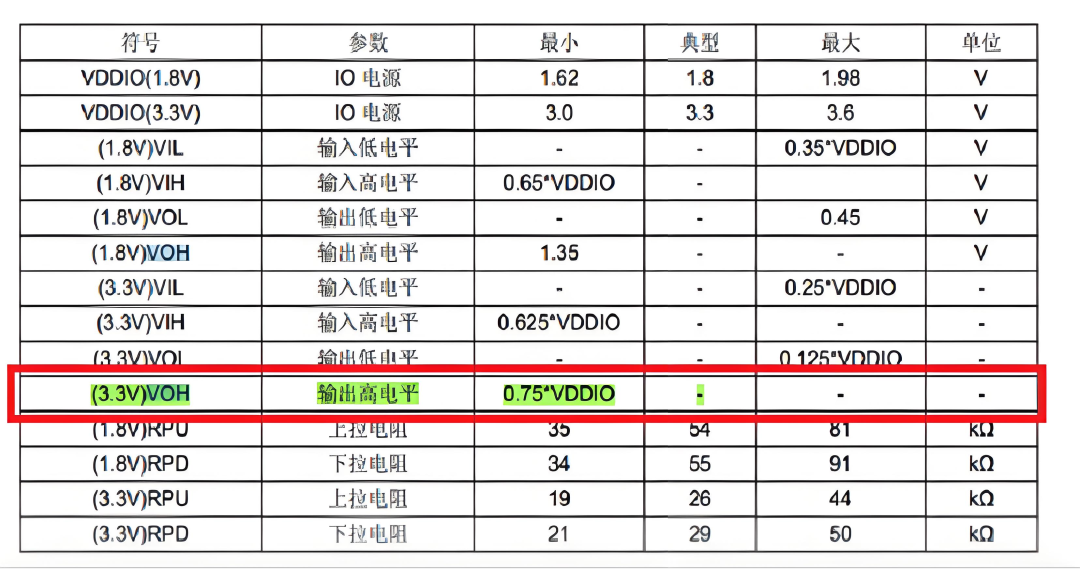

MR6450核心板處理器為先楫HPM6450,其IO 3.3V邏輯電平定義如圖2所示。

圖2 MR6450IO3.3V邏輯電平定義

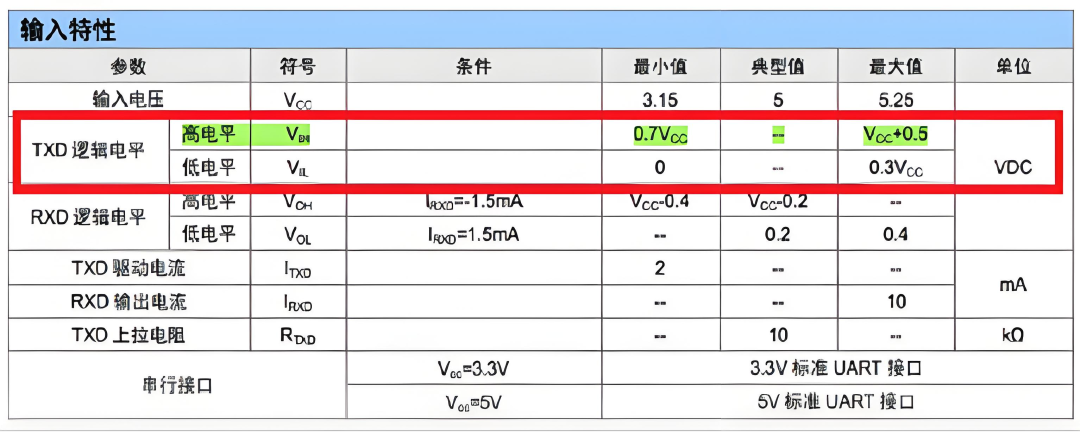

RS485模塊5V邏輯電平定義如圖3所示。

圖3 RS485模塊5V邏輯電平定義

由此可知HPM6450 TX信號輸出的高電平最大值為VCC-0.1V=3.2V , 而5V RS485模塊TXD輸入高電平的最小值為5*0.7=3.5V,很明顯不滿足驅動器輸出的VOH必須大于或等于接收器輸入的VIH(MIN)這一必要條件,IO口邏輯電平不匹配,從而導致兩個模塊間無法通訊。

解決方案:選型3.3V 邏輯電平的RS485模塊,或MCU和模塊間增加電平轉換電路。

?案例2:CAN隔離模塊電平與處理器不匹配,工作時偶爾出現間歇性通訊故障

?案例2:CAN隔離模塊電平與處理器不匹配,工作時偶爾出現間歇性通訊故障

具體表現為客戶使用我司一款隔離CAN收發器模塊,常溫下偶爾出現個別產品間歇性通訊故障,將異常產品置于高溫環境下(65℃)進行重復上電測試,可復現異常現象。

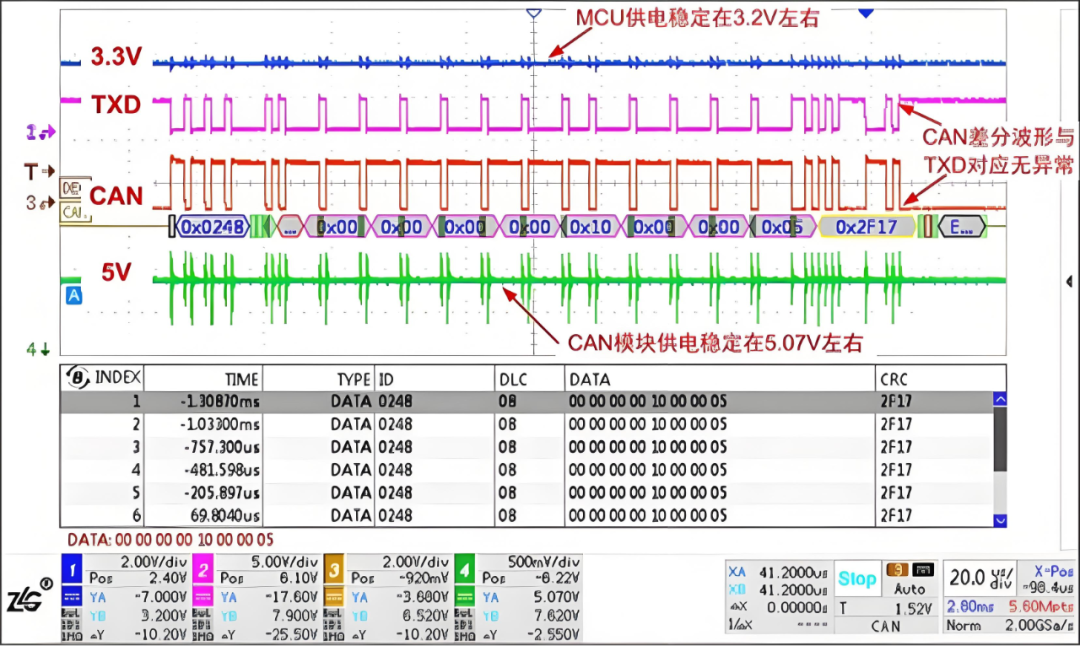

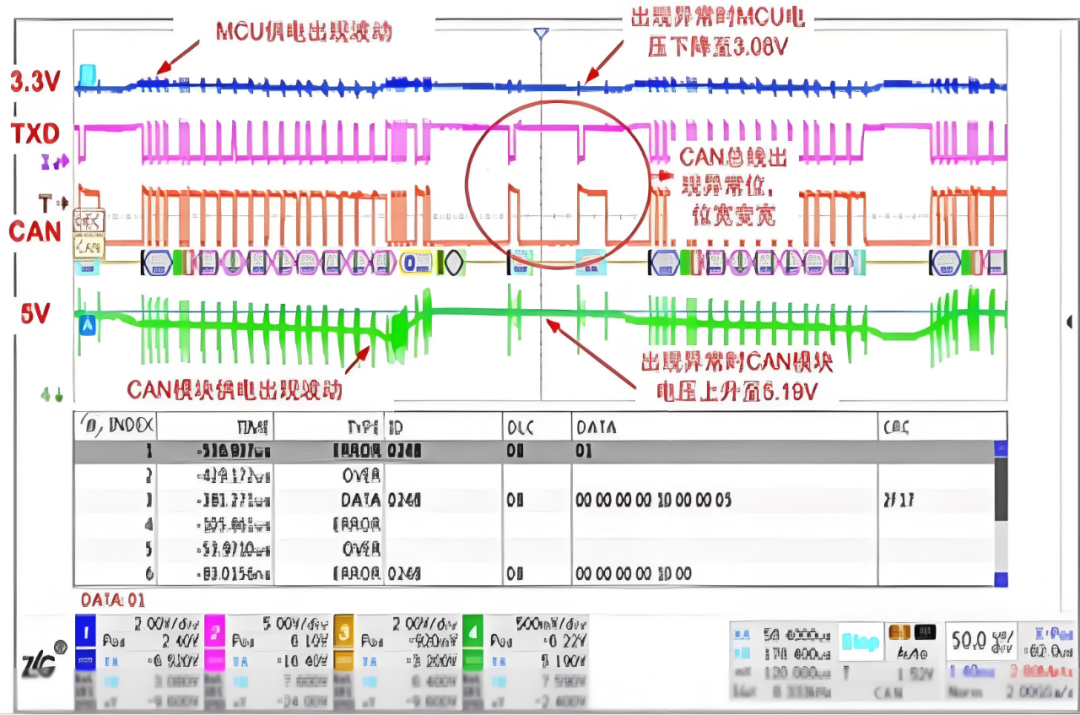

常溫下,測試異常產品的以下信號:MCU供電、TXD、CAN差分、CAN模塊供電,正常時各點波形如圖4所示。

圖4 正常時MCU、CAN差分信號、CAN模塊供電電平波形

進一步進行高溫實驗。將異常產品置于65℃的烤箱中,并進行重復上電,測試以下信號:MCU供電、TXD、CAN差分、CAN模塊供電,異常時各點波形如圖5、圖6所示。

圖5 異常時MCU、CAN差分信號、CAN模塊供電電平波形

圖6 異常時CAN差分信號、CAN模塊供電電平波形

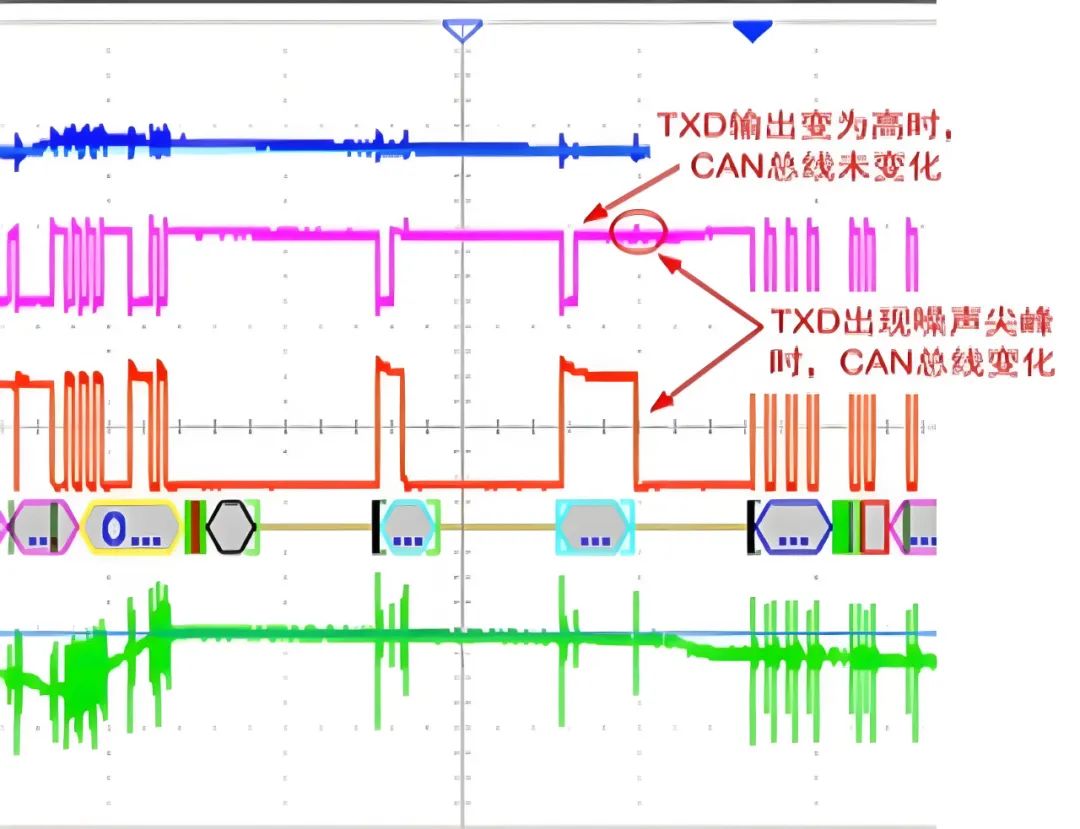

分析CAN總線出現異常位寬時的波形。當TXD信號由低變高時CAN總線電平仍然維持顯性電平,在偶然間疊加線路板上noise后引起TXD電平略微變大。此時CAN總線電平概率性變為隱性電平。

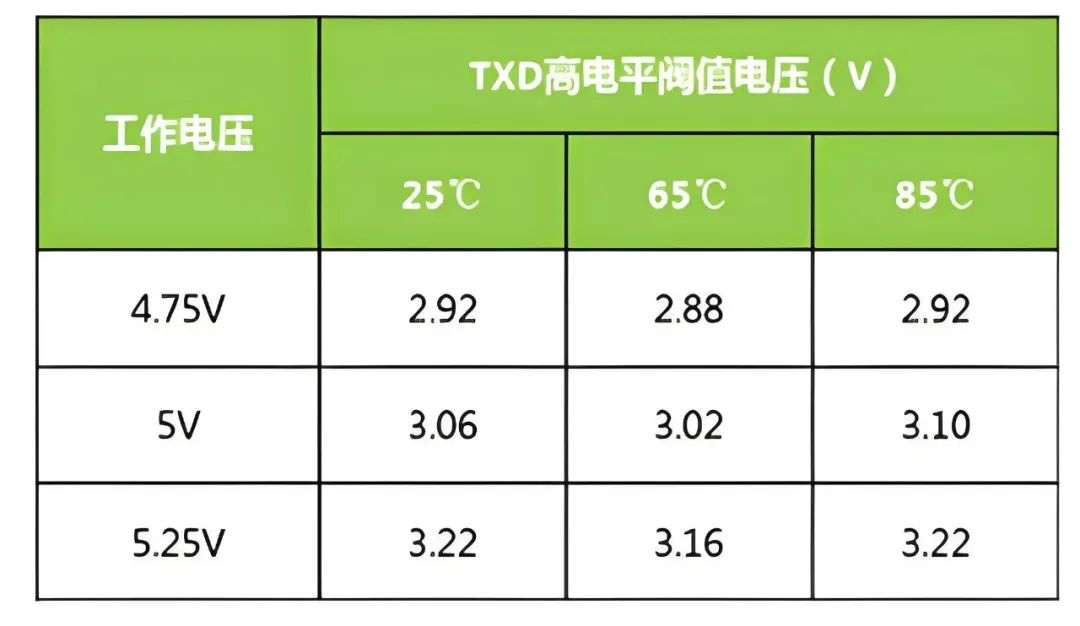

高溫環境下,因半導體材料的特性有可能會導致整個系統的功耗有所增加。此案例呈現的現象為MCU供電電壓下降,CAN模塊供電電壓上升,進一步影響到兩模塊的邏輯電平,從而使異常現象變得更為明顯。實測CAN模塊不同電壓和溫度環境下,TXD高電平閾值的變化如圖7所示。

圖7 CAN模塊不同電壓和溫度環境下,TXD高電平閾值的變化問題根因:高溫65°C環境下,CAN模塊供電5.19V,對應的TXD高電平閾值約為3.17V,MCU供電3.08V,對應的IO輸出電壓最高約為3V,MCU輸出的VOH低于CAN模塊的輸入VIH,兩模塊間邏輯電平不匹配,導致通訊異常,因IO口電平邏輯的容錯余量比較小,常溫下也許能工作,但在高溫環境等比較嚴格的環境下,兩模塊間的邏輯電平很容易出現不匹配問題。解決方案:將5V隔離模塊更換成3.3V隔離模塊。

?如果I2C電平不匹配該怎么處理?

?如果I2C電平不匹配該怎么處理?

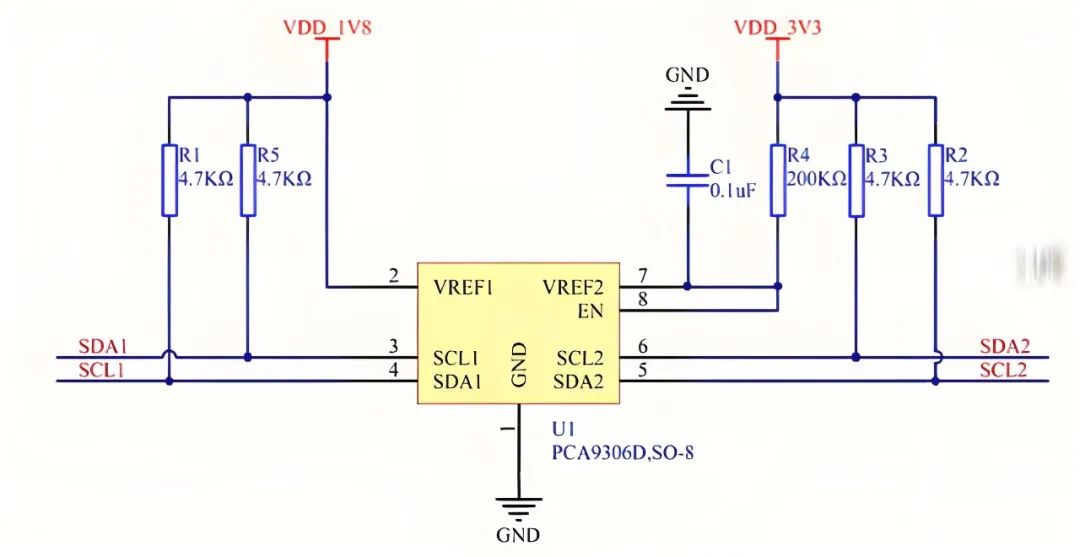

1. 使用專用的I2C總線電平轉換芯片PCA9306

PCA9306是一款支持I2C總線和SMBus的雙向電平轉換器,支持從1.0V~3.6V(Vref(1))到1.8V~5.5V(Vbias(ref)(2))的電平轉換,PCA9306可工作在兩種工作頻率下:400KHz和100KHz。最大頻率取決于RC時間常數,一般支持>2MHz。

PCA9306標準使用電路如圖8所示。

圖8 PCA9306參考電路

設計時注意以下幾點:

兩邊的電壓VREF1和VREF2并不是取任意值且VREF1為低壓位端VREF2為高壓位端;

可以使用EN鍵來控制內部開關的導通和關斷;

EN和VREF2管腳連接在一起;

上拉電阻的取值,取決于SW在導通時產生的壓降,詳見手冊推薦值。

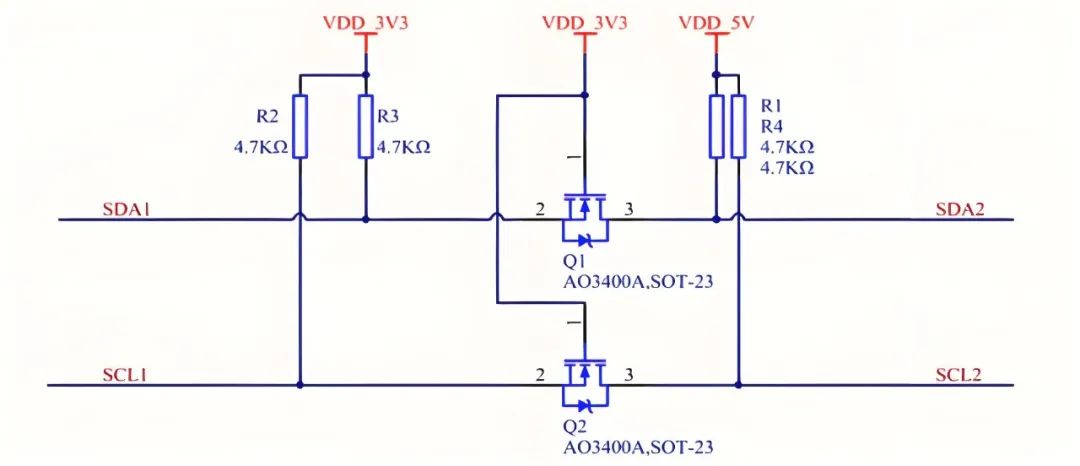

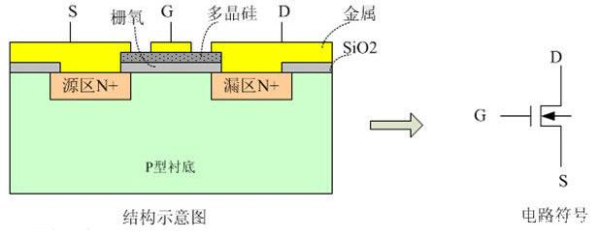

2. 使用MOS管搭建電平轉換電路

圖9所示電路是一個使用MOS管進行電平轉換的示例。

圖9 MOS實現電平轉換

設計時注意以下幾點:

低壓位VDD_3V3連接MOS管源極,高壓位VDD_5V連接MOS管漏極;

如果換用其它電壓閾之間的轉換,如3.3V、2.5V、1.8V等,需要注意MOS管Vgs開啟導通電壓;

-

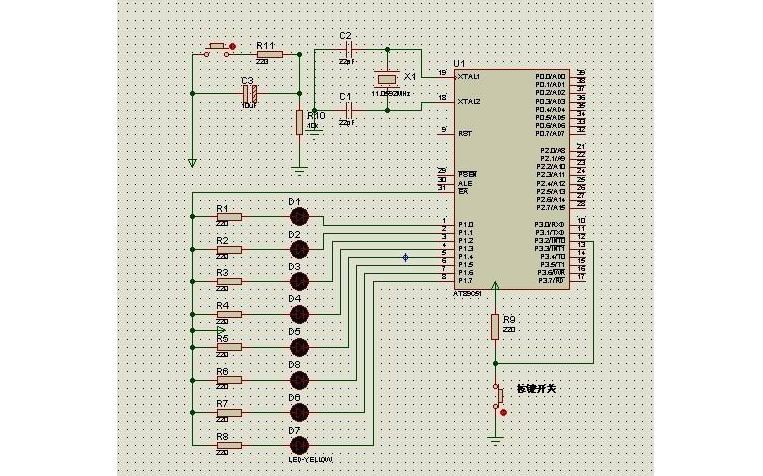

電路設計

+關注

關注

6673文章

2453瀏覽量

204350 -

設備

+關注

關注

2文章

4509瀏覽量

70637 -

電平匹配

+關注

關注

1文章

2瀏覽量

1340

發布評論請先 登錄

相關推薦

選購電視易被忽視的參數

容易被忽視的MLCC選型小技巧

那些經常被忽視的差分放大器阻抗問題

人機交互:一個被忽視的重要領域

被忽視已久的新能源發電殺手

PCB 板 layout 中容易被忽視的 12 個細節資料下載

電平匹配問題,簡單卻容易被忽視

電平匹配問題,簡單卻容易被忽視

評論