最近在看JT大佬出的一本高速PCB設計書籍,看到回流路徑這里,讓我想到最近兩個群里都提到關于這個知識點的問題。書籍很好,但是也會有一些疑問,帶著這些疑問我也查找了相關資料,我想著盡可能的結合書中知識以及自己的理解,把這個問題能給大家講明白,如果有不對的地方,歡迎大家評論區留言。

本文要從以下五個小點進行闡述:

什么是信號的回流路徑?

為什么要研究信號的回流路徑?

高速信號的回流路徑和低速信號的回流路徑有什么不一樣?

高速信號的回流路徑在信號路徑的下方,怎么理解?

了解回流路徑之后,我們在PCB設計時需要注意什么?

問題1、什么是信號的回流路徑?

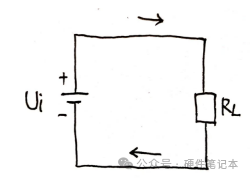

我們先看一張很基礎的圖,電流從電池的正極出發,流向負載RL,再通過負載的另一端返回電池的負極,整個過程形成一個閉環,電流只能在這個環路中流動,這是電源的回流路徑。

信號的回流路徑也差不多,信號從某個芯片的驅動引腳流出,經過傳輸線輸送到終端,被另一芯片或其它電路元件接收。然后在信號驅動電壓的驅使下,電流通過連接收發兩個芯片地引腳的地線,流回驅動電壓源的負極。

簡單說,回流路徑就是電流在源端流出,通過某個回路后,再返回來形成一個閉合回路,這個往返過程電流流過的路徑就是整個信號的回流路徑。

問題2、為什么要研究信號的回流路徑?

為什么要研究信號的回流路徑?換句話說,我們可以不管信號的回流路徑嗎?如果我們不管信號的回流路徑,會造成什么后果?

1、信號完整性問題,信號的回流路徑不連續會導致信號反射、衰減和失真。

2、信號衰減和噪聲干擾,當參考平面出現不連續時,信號的回路電流會受到干擾,從而引發噪聲問題。

3、電磁干擾EMI,不恰當的回流路徑可能導致電磁干擾(EMI),影響系統的穩定運行。

之所以會引起以上問題,是因為影響高速信號的最主要的因素是環路的寄生電感,電感量越大,環路阻抗越高,產生的感應電壓也越高,就會形成強烈的噪聲。這個環路就相當于一個環形線圈,會將干擾信號發射出去,同時也會接收外界的干擾,從而引起EMC問題。

問題3、高頻信號的回流路徑和低頻信號的回流路徑有什么不一樣?

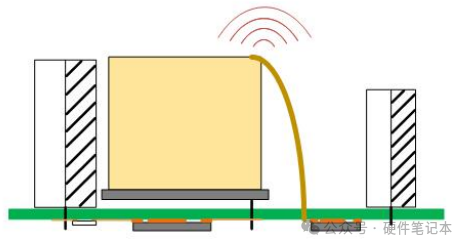

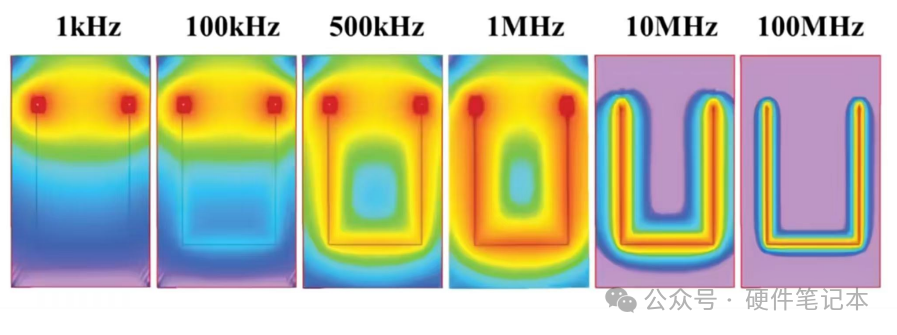

對于低頻信號來說,信號會沿著阻抗最低的路徑返回,這句話毋庸置疑。但是高頻信號這么說就不一定對,隨著信號頻率的提高,導線的感抗逐漸加大,所以返回路徑為感抗最低的回路,且集中在信號走線的下方,沿著PCB走線方向流動,大家可以看看下面這張圖。

這張圖來源群聊,好像是JT大佬視頻來的

講到這里,王工有兩個疑問:

1、寄生電感怎么來的?這不僅是本文重點考慮的因素,其它很多地方也都會聽到寄生電感這個詞,就算工作多年的工程師,你問他為什么,他可能會回答根據以往的經驗得來。

2、為什么高速信號返回路徑在信號走線的下方?

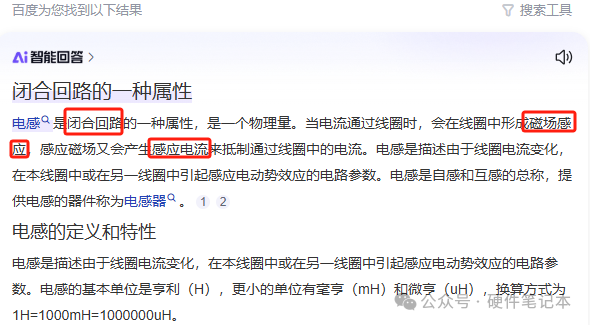

我們先來看第一點,寄生電感怎么來的?先來百度什么是電感,從最基礎的開始抓起

從定義可以總結出兩點:1、閉合回路;2、感應電流。也就是說只要在閉合回路中,導線上的電流發生變化,就會產生變化的磁場,而變化磁場又會產生反向電場來阻止電流變化,這種屬性就是電感,所以我們的電路中都會存在寄生電感。關注公眾號硬件筆記本

而我們的感抗XL=2πfL,可以看出頻率越高,感抗越大,所以高頻信號必須要把寄生電感考慮進去。

為什么高速信號返回路徑在信號走線的下方?請接著往下看

問題4、高速信號的回流路徑在信號路徑的下方,怎么理解?

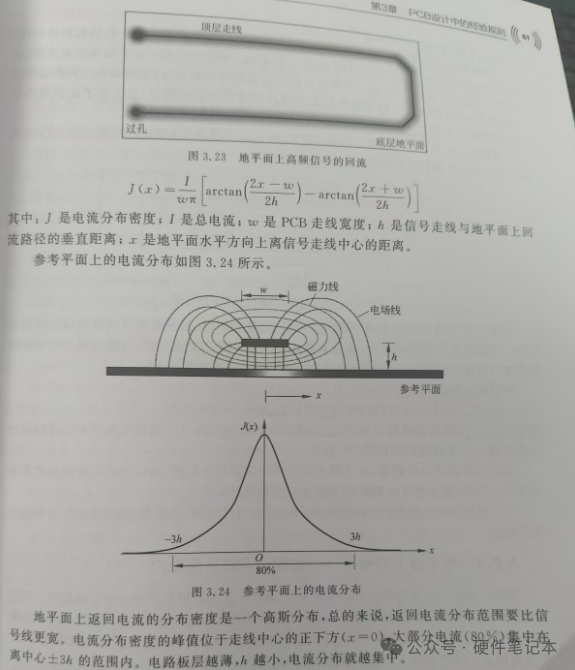

再回到JT大佬的書,最上面是高速信號的一個回流路徑示意圖,信號走頂層,然后通過底層地平面返回。

再通過一個公式和電流分布圖,可得出:返回電流主要分布在走線中心的正下方,而且電流板層越薄,也就是信號跟地平面越靠近,電流分布就越集中。

這個公式看起來有點復雜,不太好理解,大家也不用糾結它怎么來的,記住這個結論就好。

問題5、了解回流路徑之后,我們在PCB設計時需要注意什么?

1、減小信號回流的環路面積。環路面積的大小與線圈輻射和接收電磁波的能力成正比。減小環路面積有利用降低EMC。

2、走線盡可能短,地平面盡可能完整,且讓信號線與回流地平面路徑盡可能地靠近。

3、在芯片的引腳就近放置高頻小電容,為返回電流提供返回通路,否則返回電流將尋找最近的電源平面和地平面的耦合途徑進行回流(使得回流途徑難以預知和控制,從而對其它走線造成串擾)。

本文轉載自硬件筆記本公眾號

-

pcb

+關注

關注

4319文章

23099瀏覽量

397846 -

信號

+關注

關注

11文章

2791瀏覽量

76757 -

PCB設計

+關注

關注

394文章

4688瀏覽量

85619 -

回流路徑

+關注

關注

0文章

13瀏覽量

6745

原文標題:你說得對 !!! 不懂信號的回流路徑,畫不好高速PCB

文章出處:【微信號:FANYPCB,微信公眾號:凡億PCB】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

一文詳解信號的回流路徑

一文詳解信號的回流路徑

評論