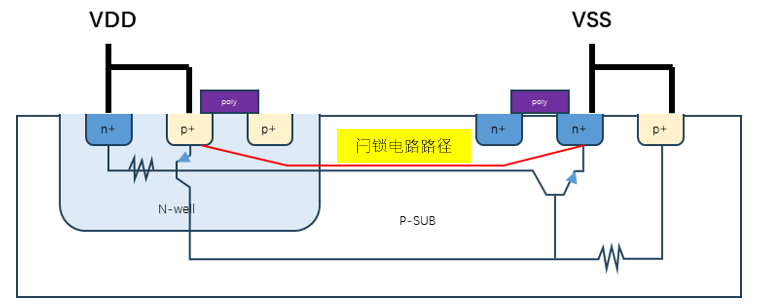

?閂鎖效應(yīng)(Latch-up)是?CMOS工藝中一種寄生效應(yīng),通常發(fā)生在CMOS電路中,當(dāng)輸入電流過大時,內(nèi)部電流急劇增加,可能導(dǎo)致電路失效甚至燒毀芯片,造成芯片不可逆的損傷。

閂鎖效應(yīng)產(chǎn)生的主要原因

■寄生雙極型晶體管的形成?:

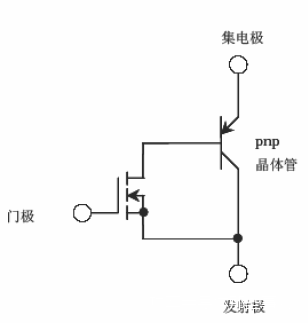

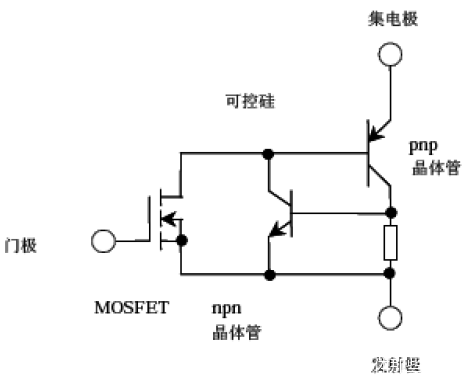

在CMOS工藝中,?NMOS和?PMOS晶體管之間的寄生?PNP和?NPN雙極型晶體管可能被激活,導(dǎo)致?正反饋環(huán)路形成,從而引發(fā)閂鎖效應(yīng)。

■ 外部輸入信號的過壓和過流?:

在芯片的某些工作條件下出現(xiàn)了過壓或過流后激發(fā)了閂鎖,這種閂鎖導(dǎo)致電路中的正反饋環(huán)路,導(dǎo)致過流持續(xù)存在。

■芯片工作的環(huán)境溫度或自身的工作溫度變高?:

芯片在高溫環(huán)境下會出現(xiàn)漏電增大,當(dāng)達到一定條件后就會激發(fā)閂鎖效應(yīng),一起寄生的PNP管的產(chǎn)生。

■ 芯片自身的極限電流和電壓條件下的工作:

芯片在超負(fù)荷的情況下會引起芯片結(jié)溫快速上升,內(nèi)阻下降后引起電流持續(xù)增加,如果內(nèi)部沒有限流抑制電流就會容易產(chǎn)生閂鎖效應(yīng)。

閂鎖效應(yīng)防御措施

■使用?Guard ring?:

在NMOS周圍使用P+ ring環(huán)繞并接地,在PMOS周圍使用N+ ring環(huán)繞并接VDD,以降低電阻值并阻止載流子到達BJT的基極。

?■優(yōu)化電路設(shè)計?:

確保NMOS和PMOS之間保持足夠的距離,以減少觸發(fā)寄生雙極型晶體管的可能性,合理分配電源和地線,降低電源噪聲,減少信號交叉耦合等。

■ 引入保護電路:

在設(shè)計電路的過程中,可以引入一些防護電路來提高電路的可靠性,增加穩(wěn)壓電路,加強電源濾波電路等。

■增加保護二極管:

保護二極管的電路會使得限制輸入和輸出電壓,在電路超電壓的情況下會提高額外的保護機制。

?

閂鎖效應(yīng)的失效分析

失效分析會分為兩種情況:可恢復(fù)的閂鎖失效和不可恢復(fù)的閂鎖失效。

可恢復(fù)的閂鎖失效分析:

在激發(fā)閂鎖的過程中需要保持電源不能斷電的情況下做熱點定位,選用InGaAs的定位工具進行定位,確認(rèn)閂鎖激發(fā)后的位置。

不可恢復(fù)的閂鎖失效分析:

這種情況是直接導(dǎo)致芯片燒毀短路,如果開蓋后表面看不到異常就可以進行熱點定位,逐層去層就能看到閂鎖導(dǎo)致的燒傷位置。

閂鎖失效的特點,會橫跨兩個器件或多個器件的串聯(lián)燒傷,并且這種燒傷的面積和嚴(yán)重程度是非常大的。如下圖,供大家參考。

季豐電子

季豐電子成立于2008年,是一家聚焦半導(dǎo)體領(lǐng)域,深耕集成電路檢測相關(guān)的軟硬件研發(fā)及技術(shù)服務(wù)的賦能型平臺科技公司。公司業(yè)務(wù)分為四大板塊,分別為基礎(chǔ)實驗室、軟硬件開發(fā)、測試封裝和儀器設(shè)備,可為芯片設(shè)計、晶圓制造、封裝測試、材料裝備等半導(dǎo)體產(chǎn)業(yè)鏈和新能源領(lǐng)域公司提供一站式的檢測分析解決方案。

季豐電子通過國家級專精特新“小巨人”、國家高新技術(shù)企業(yè)、上海市“科技小巨人”、上海市企業(yè)技術(shù)中心、研發(fā)機構(gòu)、公共服務(wù)平臺等企業(yè)資質(zhì)認(rèn)定,通過了ISO9001、 ISO/IEC17025、CMA、CNAS、IATF16949、ISO/IEC27001、ISO14001、ANSI/ESD S20.20等認(rèn)證。公司員工近1000人,總部位于上海,在浙江、北京、深圳、成都等地設(shè)有分公司。

-

芯片

+關(guān)注

關(guān)注

455文章

50812瀏覽量

423582 -

CMOS

+關(guān)注

關(guān)注

58文章

5718瀏覽量

235494 -

二極管

+關(guān)注

關(guān)注

147文章

9638瀏覽量

166477 -

閂鎖效應(yīng)

+關(guān)注

關(guān)注

1文章

30瀏覽量

9389

原文標(biāo)題:技術(shù)文章 | 芯片失效機理之閂鎖效應(yīng)

文章出處:【微信號:zzz9970814,微信公眾號:上海季豐電子】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

淺談IGBT的閂鎖效應(yīng)

電容器的常見失效模式和失效機理【上】

什么是閂鎖效應(yīng)?

max232芯片 閂鎖效應(yīng)

對 閂鎖效應(yīng) 的一些理解

元器件失效分析方法

什么是閂鎖效應(yīng)?閂鎖效應(yīng)的觸發(fā)方式有哪幾種?

MOSFET的失效機理 —總結(jié)—

CMOS閂鎖效應(yīng)

IGBT中的閂鎖效應(yīng)到底是什么

芯片失效機理之閂鎖效應(yīng)

芯片失效機理之閂鎖效應(yīng)

評論