找到一篇關(guān)于功率半導(dǎo)體嵌入PCB技術(shù)綜述,而且是22年的,還比較新。文章信息量比較大估計(jì)要一段時(shí)間看完。英文如下。直接翻譯,不畫(huà)蛇添足了。

摘要

與傳統(tǒng)封裝技術(shù)相比,將功率半導(dǎo)體器件嵌入印刷電路板(PCB)提供了幾種好處。

1、可以減少控制器尺寸,縮短電流環(huán)路,降低連接電阻與寄生電感;由于這兩者降低了傳導(dǎo)和開(kāi)關(guān)損耗,都有助于提高系統(tǒng)級(jí)效率。

2、使用厚銅基板可以有效地散熱,降低熱阻。

因此,十多年來(lái),PCB嵌入技術(shù)在電力電子領(lǐng)域受到了廣泛關(guān)注。本文旨在全面回顧關(guān)于這一主題的科學(xué)文獻(xiàn),從基礎(chǔ)的制造技術(shù)、模塊或系統(tǒng)級(jí)的電氣和熱測(cè)試的可靠性研究。性能指標(biāo),如換流回路電感Lσ,芯片面積無(wú)關(guān)的熱阻Rth*Achip,允許與傳統(tǒng)功率模塊進(jìn)行不同方法的比較和基準(zhǔn)測(cè)試。一些出版物報(bào)告了低于1nH的雜散電感和與芯片面積無(wú)關(guān)的熱阻在20~30mm2K/W范圍內(nèi)。

介紹

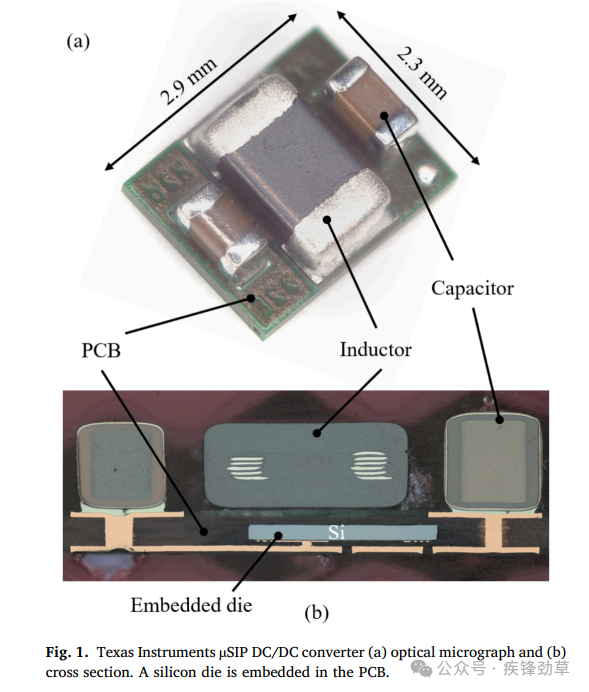

PCB是幾乎所有電子系統(tǒng)的必要組件。PCB提供了有源和無(wú)源器件的連接,這些器件一般通過(guò)焊接,粘接或者壓接技術(shù)連接到PCB。由于對(duì)更緊湊的電子設(shè)備需求,工程師開(kāi)始在電路板的多層結(jié)構(gòu)中構(gòu)建無(wú)源器件。電阻器是通過(guò)在電路板中層壓的電阻層生成的,如(NiP-basedOmegaply )。高介電材料可以制造嵌入電容,磁材料制造集成電感。通過(guò)把SMD元件埋入PCB,通過(guò)內(nèi)層連接,也是一種集成無(wú)源器件的方法。以同樣的方式,無(wú)論SMD封裝還是die都能被嵌入到PCB中。起初,這些技術(shù)首先被開(kāi)發(fā)應(yīng)用于通信領(lǐng)域。為了更進(jìn)一步小型化,F(xiàn)raunhofer IZM開(kāi)發(fā)了PCB嵌入2chip模塊,3D系統(tǒng)級(jí)封裝(SIP)和quad-flat Non-Lead(QFN)封裝。小型化減少了寄生電阻和電感,對(duì)于功率電路帶來(lái)很大好處。不久,使用PCB嵌入技術(shù)的小功率變換器SIP實(shí)現(xiàn)了商業(yè)化。一個(gè)例子是Ti在2010年推出的MicroSIP技術(shù)。這里的一個(gè)小功率DCDC變換器包含了一個(gè)嵌入基板的MOSFET裸Die和表貼式被動(dòng)元器件,見(jiàn)圖1。其他公司類(lèi)似的技術(shù)包括英飛凌的DrBlade,TDK的Semiconductor

Embedded in Substrate (SESUB)。典型的,這些嵌入SIP功率在幾瓦的范圍,電壓小于50V。

最近,研發(fā)人員和工程師已經(jīng)研究了使用PCB嵌入應(yīng)用于大功率應(yīng)用,包括電壓到1200V,功率到100kW。一個(gè)主要的驅(qū)動(dòng)力是乘用車(chē)的電氣化,要求高重量密度、體積密度的低成本轉(zhuǎn)換器。由于能夠最小化封裝的寄生電感,PCB嵌入技術(shù)特別適合于高開(kāi)關(guān)速度的寬帶隙半導(dǎo)體,如碳化硅(SiC) MOSFET,氮化鎵(GaN) HEMT。這些器件要求小的環(huán)路電感,以便干凈有效的開(kāi)關(guān)。

這篇文章論文綜述了PCB嵌入半導(dǎo)體的中功率應(yīng)用(這里定義為1~100kW的功率,最高電壓1200V)的科學(xué)文獻(xiàn)。這里不包含嵌入被動(dòng)元器件、傳感器、熱管理的低功率應(yīng)用。另外一篇報(bào)道包含更廣泛的范圍,包含了這些內(nèi)容。

文章結(jié)構(gòu)如下;首先,簡(jiǎn)單介紹功率半導(dǎo)體嵌入PCB的半導(dǎo)體設(shè)備;接著,介紹主流的工業(yè)過(guò)程制造技術(shù);其次

本文結(jié)構(gòu)如下:第一部分簡(jiǎn)要介紹嵌入電路的功率半導(dǎo)體設(shè)備。接下來(lái),將重點(diǎn)介紹主流工業(yè)過(guò)程的制造技術(shù)。此外,該論文涵蓋了學(xué)術(shù)研究人員經(jīng)常研究的非傳統(tǒng)方法。對(duì)制造中的常見(jiàn)挑戰(zhàn)進(jìn)行了回顧和討論。第3節(jié)給出了選擇嵌入材料的要求,展示了一些精選的示例。第4節(jié)討論了用于熱和電氣性能測(cè)試的方法。基于性能數(shù)據(jù)展示出該技術(shù)的好處。接下來(lái),描述了PCB嵌入技術(shù)的挑戰(zhàn)和局限性。第5節(jié)重點(diǎn)介紹PCB嵌入式功率半導(dǎo)體的可靠性,解決熱機(jī)械問(wèn)題以及電氣隔離問(wèn)題。本文最后對(duì)未來(lái)發(fā)展進(jìn)行了簡(jiǎn)要討論和展望。

2. PCB embedding 技術(shù)

本節(jié)介紹PCB嵌入的基本原理。首先簡(jiǎn)要介紹了嵌入電路板中的有源功率半導(dǎo)體器件。隨后,在介紹不同的PCB嵌入方法之前,簡(jiǎn)要介紹了傳統(tǒng)封裝相關(guān)技術(shù)。有一些共同的挑戰(zhàn),如銅芯片金屬化的必要性、微孔鉆孔和電鍍以及熱機(jī)械應(yīng)力。最后一小節(jié)介紹了更多非傳統(tǒng)的嵌入技術(shù)

2.1 功率半導(dǎo)體和傳統(tǒng)的封裝

電力電子轉(zhuǎn)換器基于開(kāi)關(guān)模式運(yùn)行,因此,需要半導(dǎo)體晶體管作為開(kāi)關(guān)元件。硅金屬氧化物半導(dǎo)體場(chǎng)效應(yīng)晶體管(MOSFET)通常用于不高于600V的低電壓應(yīng)用。對(duì)于更高電壓,絕緣柵雙極晶體管(IGBT)是常用解決方案。然而,在大多數(shù)應(yīng)用中,需要使用獨(dú)立的反并聯(lián)續(xù)流二極管。由于其更高的效率,基于寬帶隙材料的新型半導(dǎo)體器件越來(lái)越受到歡迎,尤其是在快速開(kāi)關(guān)的應(yīng)用中。突出的例子是氮化鎵(GaN)高電子遷移率晶體管(HEMT)和碳化硅(SiC)MOSFET。GaN HEMT適用于電壓低于650 V的應(yīng)用,而SiC MOSFET則適用于更高的電壓。微電子通常將數(shù)百萬(wàn)個(gè)晶體管集成到單個(gè)半導(dǎo)體芯片中,相對(duì)的功率器件每個(gè)芯片只包含一個(gè)晶體管。設(shè)備的電流額定值與其占地面積Achip成比例。對(duì)于MOSFET和IGBT,采用的是垂直結(jié)構(gòu),柵極和源極(如果是IGBT,則為發(fā)射極)位于芯片的頂部,漏極(或集電極)位于芯片的底部。GaN HEMT是水平結(jié)構(gòu)器件,所有功能連接都位于芯片頂面。然而,其基板需要確定的電勢(shì),因此在芯片底部也要包含一個(gè)觸點(diǎn)。因此,任何功率半導(dǎo)體的封裝技術(shù)都需要在半導(dǎo)體芯片的頂部和底部建立電連接。在傳統(tǒng)封裝中,半導(dǎo)體底部附著于導(dǎo)電基板,在分立封裝中是金屬引線(xiàn)框架,在多芯片的功率模塊中是覆銅陶瓷基板。為了實(shí)現(xiàn)焊料與芯片粘接,使用銀對(duì)芯片的底部金屬化。頂部需要鋁基金屬化,觸點(diǎn)由粗鋁鍵合線(xiàn)形成。為了保護(hù)并提供足夠的隔離,這些設(shè)備通過(guò)環(huán)氧樹(shù)脂塑封,或者通過(guò)硅膠灌封。在傳統(tǒng)的功率電路中,封裝好的功率半導(dǎo)體與電路上的其他組件通過(guò)PCB或匯流條(Busbar)連接。PCB嵌入技術(shù)提供了一種另一種方法——將功率半導(dǎo)體芯片嵌入電路板。以下部分介紹這種嵌入式功率電子設(shè)備的制作過(guò)程技術(shù)。

2.2 主流的嵌入過(guò)程

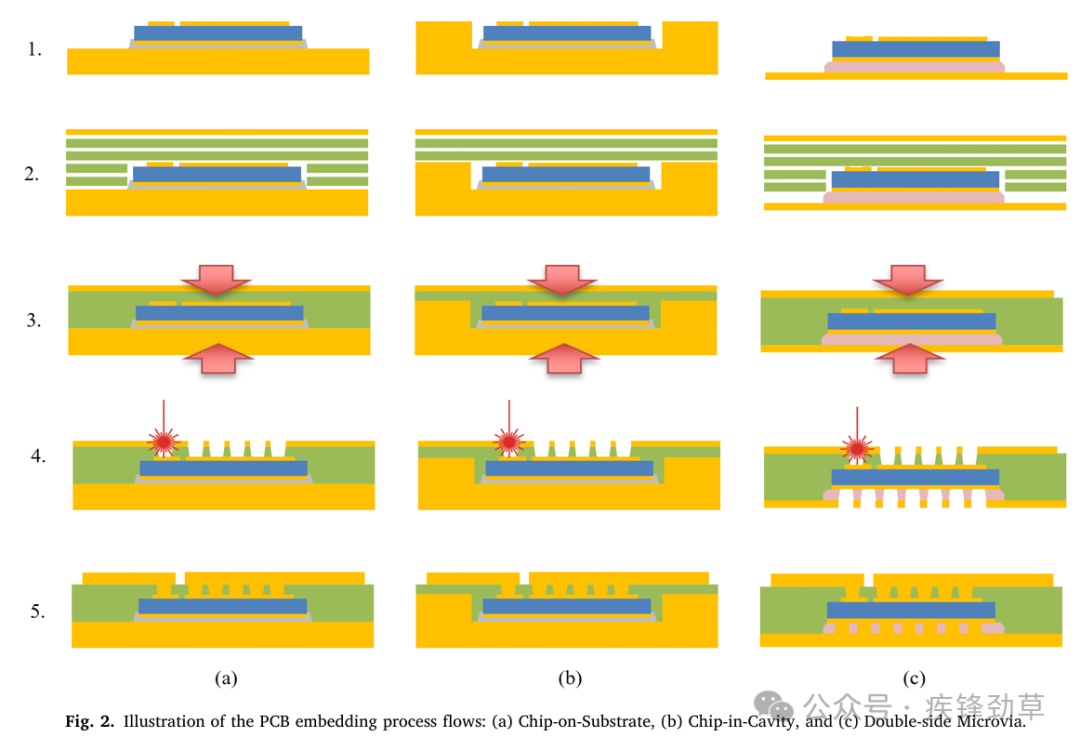

PCB嵌入式功率器件的制造本質(zhì)上意味著在半導(dǎo)體芯片周?chē)鷺?gòu)建電路板。本節(jié)介紹了三種最常見(jiàn)的制造工藝,這些工藝可從各種PCB制造商那里買(mǎi)到。圖2示意性地說(shuō)明了基本工藝步驟,(a)“芯片在基板上(Chip-on- Substrate)”工藝,(b)“芯片在腔體中(Chip-in-Cavity)”工藝和(c)“雙面微過(guò)孔(Double- side Microvia)”工藝。

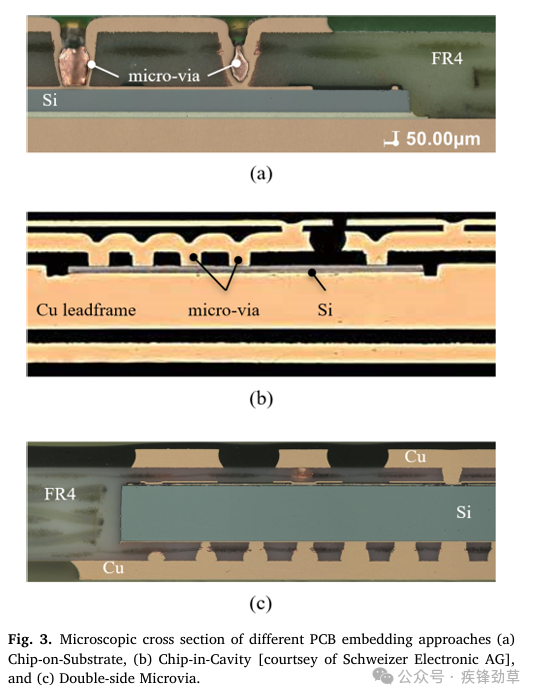

Chip-on- Substrate工藝是由Fraunhofer IZM于1999年發(fā)明的。第一步,將半導(dǎo)體die連接到“PCB底層”。該底層可以是銅基板、絕緣金屬基板(IMS)或覆銅陶瓷基板,如直接銅鍵合(DCB)。幾個(gè)預(yù)浸料(一種玻璃纖維織物,預(yù)先浸漬有部分固化的樹(shù)脂,在PCB行業(yè)中稱(chēng)為FR4堆疊在上面。第一預(yù)浸料層具有切口,以容納半導(dǎo)體芯片,而上層覆蓋整個(gè)區(qū)域。銅箔覆蓋在疊層上。預(yù)浸料的厚度和樹(shù)脂含量需要仔細(xì)考慮,因?yàn)轭A(yù)浸料中的樹(shù)脂流動(dòng)填充幾何體積。該疊層在180~200℃的溫度和1~3 MPa的壓力下在真空壓機(jī)中層壓60~180分鐘。確切的工藝條件取決于樹(shù)脂類(lèi)型和確切的幾何形狀。使用激光工藝鉆出微孔,在芯片頂部金屬化處停止。通過(guò)電鍍銅和隨后對(duì)頂側(cè)軌跡進(jìn)行結(jié)構(gòu)化來(lái)建立頂側(cè)連接。電鍍工藝要求在芯片上進(jìn)行銅金屬化,這在目前并不常見(jiàn),因?yàn)榇蠖鄶?shù)半導(dǎo)體芯片采用為了引線(xiàn)鍵合的鋁基金屬化。第2.3節(jié)將更詳細(xì)地討論這個(gè)問(wèn)題。圖3(a)顯示了通過(guò)芯片在基板上工藝嵌入的硅二極管橫截面的光學(xué)顯微照片。

圖2(b)概述了Chip-in-cavity工藝。基板通常是厚銅板,具有放置半導(dǎo)體芯片的腔體。腔深等于芯片和芯片連接鍵合線(xiàn)厚度(The cavity depth equals the chip and die-attach bond line thickness),因此芯片的頂部金屬化與基板表面齊平。隨后,將非結(jié)構(gòu)化預(yù)浸料和銅箔堆疊在頂部。不需要使用結(jié)構(gòu)化的預(yù)浸料,這有助于層壓板的堆疊。該工藝的后續(xù)步驟與Chip-on-Substrate工藝的步驟相同,需要真空層壓、激光鉆孔、鍍銅和頂部軌跡的結(jié)構(gòu)化。該技術(shù)可從PCB供應(yīng)商處獲得,如德國(guó)Schweizer Electronic AG(稱(chēng)為p2Pack技術(shù))或Advanced Semiconductor Engineering ASE Inc(稱(chēng)為嵌入式有源系統(tǒng)集成eASI(embedded active system integration)。圖3(b)顯示了用p2 Pack技術(shù)制造的嵌入式封裝的橫截面圖。

雙面微孔嵌入如圖2(c)所示。在這里,芯片通過(guò)(非導(dǎo)電)粘合劑附著在薄銅箔上。多層預(yù)浸料,有和沒(méi)有切口,以及最終的銅箔堆疊在頂部。在器件的頂部和底部激光鉆孔之前,對(duì)堆疊層進(jìn)行真空層壓。這樣,所有的電連接都是通過(guò)鍍銅建立的,避免了任何潛在的關(guān)鍵芯片連接層。該工藝來(lái)自?shī)W地利AT&S的嵌入式組件包ECP(Embedded Component Package)或德國(guó)伍爾特電子公司的MICROVIA。圖3(c)展示了通過(guò)ECP技術(shù)制造的GaN Systems GS61008T封裝的橫截面顯微照片。通過(guò)在芯片背面引入全面積鍍層,可以修改基本的雙面微通孔工藝,以改善嵌入式組件的散熱效果。AT&S將這種工藝變體稱(chēng)為PARSEC(PlAnaR Surface Embedded Components))技術(shù)。

上述嵌入技術(shù)可以應(yīng)用于兩種不同的集成概念,如圖4所示。在第一個(gè)概念中,嵌入技術(shù)被用作器件級(jí)PCB功率組件制造。這些組件作為表貼器件(SMD)連接到主電路板上。嵌入技術(shù)為基于傳統(tǒng)引線(xiàn)框架的分立封裝提供了一種替代解決方案。GaN Systems GaN PX封裝是這種PCB電源封裝的一個(gè)很好的例子。它是使用AT&S的ECP技術(shù)制造的。一些出版物使用了“預(yù)封裝prepackage”一詞,這是Fraunhofer IZM的研究人員首次引入的。與PCB功率封裝相比,prepackage確實(shí)包含散熱器,并且沒(méi)有提供足夠的間隙和爬電。需要第二個(gè)組裝步驟,例如通過(guò)PCB嵌入,來(lái)獲得強(qiáng)大的功率模塊。Sharma等人為這種方法提供了一個(gè)很好的例子。

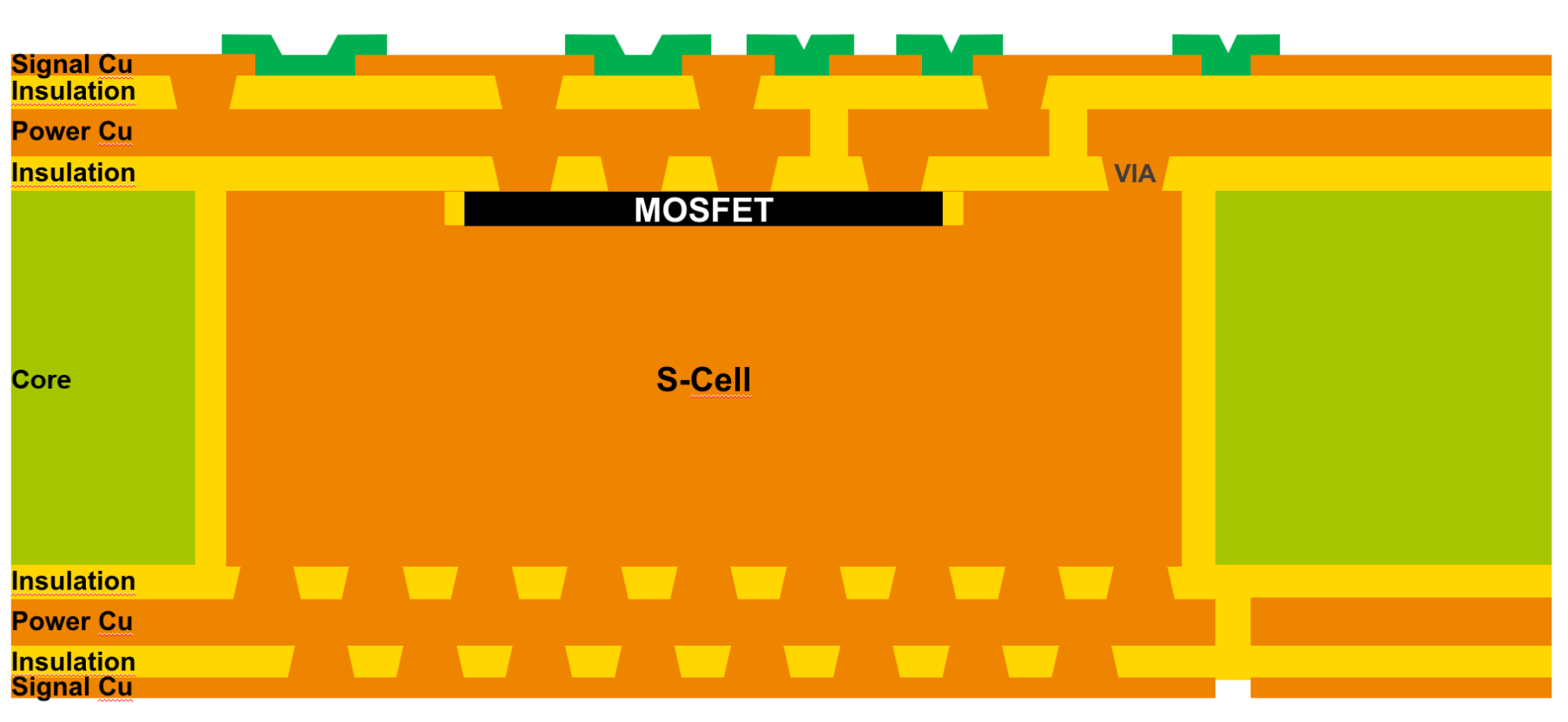

第二個(gè)概念將PCB嵌入用于器件級(jí)封裝和板級(jí)封裝。這需要在芯片嵌入后進(jìn)行額外的層壓步驟,以增加更多的布線(xiàn)層,并在連接散熱器的封裝底部提供電絕緣。為了實(shí)現(xiàn)高效散熱,需要導(dǎo)熱、電絕緣的預(yù)浸料材料。關(guān)于材料的更多詳細(xì)信息,請(qǐng)參閱第3節(jié)。帶有多個(gè)嵌入式功率半導(dǎo)體和內(nèi)部電氣隔離的PCB被為PCB功率模塊。其他組件,如柵極驅(qū)動(dòng)器、去耦電容器和溫度或電流傳感器,通過(guò)SMD連接到PCB功率模塊上,生成嵌入式“智能功率模塊“(IPM)。在極端情況下,整個(gè)電源電路集成在嵌入式PCB上,形成完整的板上系統(tǒng)(System-in- Board SiB)。

2.3. 制造技術(shù)挑戰(zhàn)

本節(jié)詳細(xì)介紹了幾乎任何嵌入工藝中都需要解決的重要挑戰(zhàn)。如前所述,功率半導(dǎo)體通常在背面為Ag,在正面為Al。嵌入技術(shù)需要一個(gè)Cu面,以便后續(xù)的微孔鍍層。第一小節(jié)介紹了在晶片級(jí)(wafer-level)或芯片級(jí)生成銅表面的方法。激光鉆孔是與銅金屬化密切相關(guān)的另一個(gè)關(guān)鍵工藝步驟,將在第二小節(jié)中介紹。最后一小節(jié)涉及熱機(jī)械應(yīng)力,這些應(yīng)力固有地存在于具有不同熱膨脹系數(shù)(coefficient of thermal expansion CTE)的異質(zhì)材料的封裝中。

2.3.1. 鍍銅

如上所述,大多數(shù)嵌入工藝都需要銅金屬化,要么僅在正面(Chip-on-Substrate 、Chip-in- Cavity),要么在芯片的兩面(Double-side-Microvia)。然而,傳統(tǒng)封裝也對(duì)正面感興趣,其中用銅鍵合線(xiàn)代替鋁鍵合線(xiàn)可以顯著改善功率循環(huán)。在公共資助的研究項(xiàng)目ProPower中,對(duì)晶圓級(jí)電鍍進(jìn)行了研究。首先,在原始芯片金屬化層的頂部沉積晶種層,并通過(guò)光刻進(jìn)行結(jié)構(gòu)化。隨后,在光刻膠限定的芯片焊盤(pán)中電鍍銅。隨后剝離光刻膠并蝕刻晶種層。最后,將芯片切塊并從載體上取出。優(yōu)化了電鍍工藝參數(shù),可鍍出高達(dá)50μm厚的銅。然而,在30~50μm的銅厚度范圍內(nèi),觀察到芯片彎曲超過(guò)100μm。通過(guò)雙面鍍銅可以減少die的彎曲。為此,已經(jīng)開(kāi)發(fā)了特殊的工具,可以在薄功率半導(dǎo)體晶片上使用低應(yīng)力銅。 由于這些電鍍工藝尚未廣泛應(yīng)用到商業(yè)產(chǎn)線(xiàn)中,許多用戶(hù)不得不使用標(biāo)準(zhǔn)金屬化。因此,研究人員開(kāi)發(fā)了芯片級(jí)解決方案,用于在鋁金屬化上沉積銅。Randoll等人描述了一種芯片級(jí)電鍍工藝,類(lèi)似于上述晶片級(jí)工藝。另一種選擇是使用物理氣相沉積(PVD)。這里,Cu幾何形狀由shadow mask定義,避免了芯片級(jí)的光刻。Kearney等人使用這種工藝在IGBT和二極管的al金屬化層上濺射Cr/Cu(5 nm/8μm)。Le Lesl′e等人比較了Cu的電子束和熱蒸發(fā)(e-beam and thermal evaporation)方法。事實(shí)證明,這兩種方法都是不切實(shí)際的。熱蒸發(fā)沒(méi)有在原始金屬化層和銅層之間產(chǎn)生良好的粘附性,導(dǎo)致器件運(yùn)行過(guò)程中的損耗顯著增加。由于柵極氧化物中的陷阱電荷,電子束工藝引入了閾值電壓的負(fù)偏移。

2.3.2. 微孔形成

在PCB堆疊層壓后,通過(guò)微過(guò)孔建立電連接。微過(guò)孔通過(guò)紫外(UV)或紅外(IR)激光加工形成的。兩者都可以去除玻璃纖維/樹(shù)脂復(fù)合材料。銅只能通過(guò)紫外激光去除,這帶來(lái)了好處,因?yàn)槲⒖仔枰@穿頂層銅層。當(dāng)使用紅外激光時(shí),需要預(yù)先通過(guò)光刻和蝕刻去除頂層銅層。另一方面,鉆孔過(guò)程需要在芯片金屬化上停止,而不造成任何損壞。在這里,紅外激光更合適,因?yàn)閷?duì)金屬化層輸入較低的能量輸入。Munding等人對(duì)激光工藝進(jìn)行了更深入的研究。在他們的研究中,他們使用了波長(zhǎng)為9.4μm的紅外激光器。使用PVD工藝和隨后的光刻,在芯片本來(lái)的Al金屬化上沉積Cu。對(duì)各種工藝參數(shù)進(jìn)行了研究。在高能量輸入的情況下,在金屬化中觀察到氣泡。氣泡是由Al-Cu界面形成的共晶引起的。這種共晶相的熔點(diǎn)僅為547℃,而純鋁的熔點(diǎn)為660℃。因此,當(dāng)?shù)竭_(dá)激光工藝的熱影響區(qū)時(shí),共晶首先熔化。在最壞的情況下,在這個(gè)位置的整個(gè)金屬化層被去除,甚至可能引發(fā)芯片開(kāi)裂。為了克服這個(gè)問(wèn)題,作者建議鍍上厚度超過(guò)11μm的銅,以使Al-Cu界面遠(yuǎn)離熱影響區(qū)。此外,可以在Al和鍍Cu之間放置擴(kuò)散阻擋層,以避免形成共晶相。

其他研究人員優(yōu)化了通孔結(jié)構(gòu)的幾何形狀,以實(shí)現(xiàn)低接觸電阻和低熱阻。Yu等人研究了通孔尺寸和通孔數(shù)量對(duì)接觸電阻的影響。由于研究了不常見(jiàn)的幾何形狀(1mm2的方形阱穿過(guò)400μm厚的FR4層,鍍銅厚度為7μm),理論上獲得了1.13 m?的不切實(shí)際的高電阻。實(shí)驗(yàn)表明,由于芯片級(jí)PVD鍍覆的厚度小于500nm的銅金屬化層分層,結(jié)果甚至更高。

Reiner等人研究了通孔直徑對(duì)通過(guò)雙面微通孔工藝嵌入的GaN功率IC熱阻的影響。在固定間距下,通孔直徑的增加會(huì)降低熱阻。直徑為50μm的通孔的熱阻為3.7 K/W,當(dāng)通孔直徑為100μm時(shí),熱阻降至1.1 K/W。

Perrin等人提出了微孔密度的進(jìn)一步改進(jìn)。在鉆孔和鍍覆第一組通孔之后,將第二組通孔放置在已經(jīng)建立的通孔之間的未鍍區(qū)域中。與只有一組微孔的傳統(tǒng)結(jié)構(gòu)相比,在四次迭代中產(chǎn)生的連接將封裝的熱阻降低了32%。

2.3.3. 熱機(jī)械應(yīng)力

具有不同CTE的異質(zhì)材料在任何類(lèi)型的封裝中都會(huì)引入熱機(jī)械應(yīng)力。這些應(yīng)力可能會(huì)導(dǎo)致制造中的屈服問(wèn)題,例如由于芯片斷裂或由于疲勞而限制壽命。在傳統(tǒng)封裝中,鍵合線(xiàn)剝離和die-attach分層是由熱機(jī)械應(yīng)力引起的主要失效模式。

PCB嵌入式封裝包含Si或SiC半導(dǎo)體芯片,這些芯片通常附著在Cu層上,并由FR4等電介質(zhì)層壓板封裝。表1列出了相關(guān)材料特性。電路板材料FR4和Cu具有相近匹配的CTE,但是與半導(dǎo)體材料嚴(yán)重不匹配。在高溫下組裝部件時(shí)會(huì)引入機(jī)械應(yīng)力。Die-attach通常通過(guò)粘合劑粘合、焊接、銀燒結(jié)或瞬態(tài)液相粘合進(jìn)行。除了粘合劑粘合是一種低溫工藝外,所有其他Die-attach技術(shù)都需要230°C至260°C的工藝溫度。冷卻到室溫將引入顯著的應(yīng)力。隨后在180°C至200°C下對(duì)電介質(zhì)進(jìn)行層壓,有助于封裝中的整體應(yīng)力分布。這些應(yīng)力會(huì)導(dǎo)致芯片自發(fā)斷裂。幾位作者報(bào)告了芯片附著后或嵌入后的水平裂紋。裂紋形成的原因如下:由于其較低的CTE,半導(dǎo)體芯片會(huì)受到平面內(nèi)壓應(yīng)力。橫向收縮(泊松比)在z方向上引起拉伸應(yīng)力。芯片邊緣的表面缺陷是由切割過(guò)程引起的,會(huì)引發(fā)水平裂紋的形成。(Due to its lower CTE, the semiconductor die experiences in-plane compressive stress. Transverse contraction (Poisson′s ratio) induces tensile stress in the z-direction (Kasem & Feinstein, 1987)。 Surface flaws on the chip edge, which are caused by the dicing process, trigger the formation of horizontal cracks)。斷裂概率的預(yù)測(cè)需要統(tǒng)計(jì)方法。結(jié)果受到芯片幾何形狀、表面質(zhì)量和金屬化結(jié)構(gòu)的強(qiáng)烈影響。

2.4. 非傳統(tǒng)嵌入過(guò)程

除了主流的PCB嵌入工藝外,科學(xué)文獻(xiàn)還討論了不同的替代方法,這些方法通常由學(xué)術(shù)界開(kāi)發(fā)。

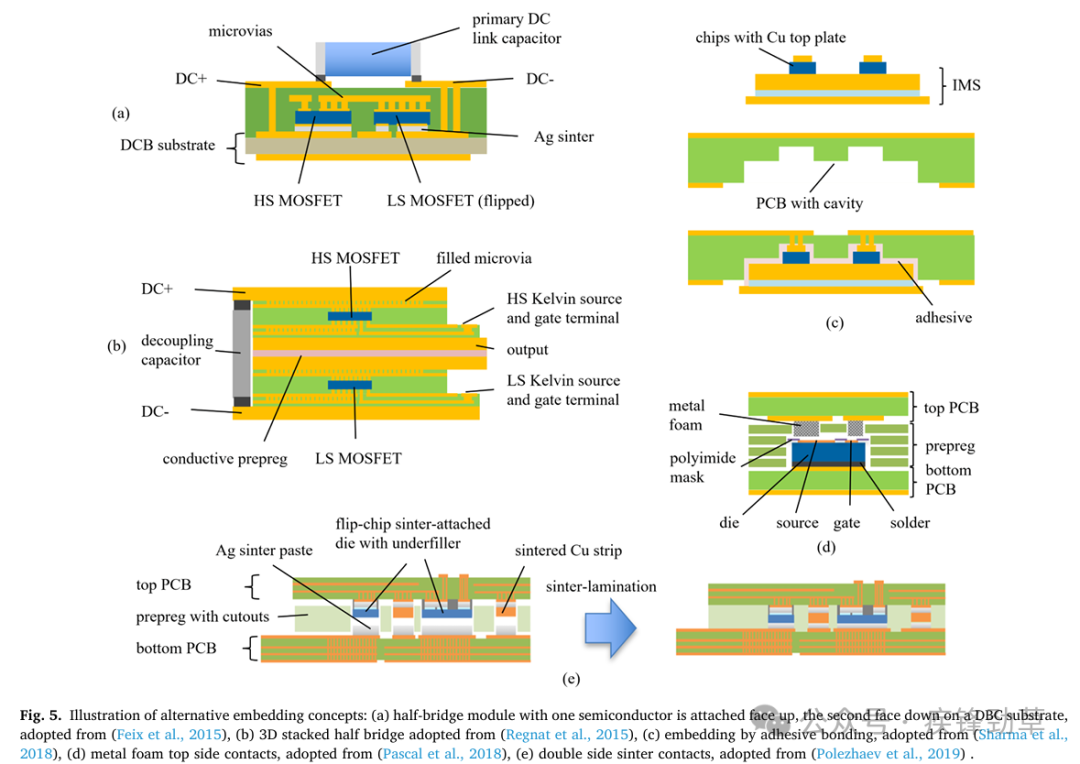

一個(gè)例子是Feix等人開(kāi)發(fā)的SiC半橋功率模塊。工藝技術(shù)基于使用氮化鋁DCB的Chip-on-Substrate工藝。然而,半橋的高邊開(kāi)關(guān)以倒裝芯片(flip-chip)的形式面朝下附著在基板上,而低邊開(kāi)關(guān)則面朝上附著,見(jiàn)圖5(a)。這樣,通過(guò)將DC-link電容器直接放置在頂部,可以最小化換向回路電感。此外,輸出電容顯著降低,因?yàn)檩敵鲭妱?shì)僅位于第一PCB層上,不能形成對(duì)地的寄生電容。

Regnat等人開(kāi)發(fā)了power chip on chip(PCOC)模塊,其中嵌入式高邊和低邊開(kāi)關(guān)堆疊在一起。該概念基于雙面微孔嵌入工藝。通過(guò)順序?qū)訅翰襟E添加用于開(kāi)爾文觸點(diǎn)、柵極和電源觸點(diǎn)布線(xiàn)的附加層。這樣,就生成了兩個(gè)幾乎相同的子模塊。如圖5(b)所示,這兩個(gè)部分都使用導(dǎo)熱和導(dǎo)電預(yù)浸料進(jìn)行層壓,以產(chǎn)生堆疊半橋。由于每個(gè)開(kāi)關(guān)包含4個(gè)并聯(lián)的SiC MOSFET,因此需要特別注意使所有開(kāi)關(guān)的阻抗對(duì)稱(chēng)。因此,SMD去耦電容器附著在模塊DC+和DC-之間的側(cè)壁上。這個(gè)概念的主要優(yōu)點(diǎn)是雜散電感極低。一個(gè)模型已被用于阻抗測(cè)量,其中半導(dǎo)體已被通孔取代以形成短路。基于該測(cè)量,估計(jì)功率回路電感為0.23nH。

為了避免在PCB生產(chǎn)線(xiàn)中處理裸片,Sharma等人開(kāi)發(fā)了一種特殊工藝,通過(guò)粘合劑粘合進(jìn)行嵌入。圖5(c)概述了這一概念。第一步,PCB供應(yīng)商制造一個(gè)帶有機(jī)加工腔的半成品電路板。半導(dǎo)體供應(yīng)商將芯片組裝到IMS基板上。為了嵌入半導(dǎo)體,兩個(gè)部分用硅膠粘合劑粘合在一起。電路板被送回PCB生產(chǎn)線(xiàn),在那里,芯片被鍍Cu的微孔連接,頂部軌跡被結(jié)構(gòu)化。這種方法的另一個(gè)獨(dú)特之處是半導(dǎo)體的頂部接觸。首先,通過(guò)化學(xué)鍍Ni/Au層對(duì)標(biāo)準(zhǔn)Al金屬化進(jìn)行改性。這種表面處理允許在芯片金屬化上焊接或燒結(jié)銅板,類(lèi)似于丹佛斯Bond Buffer或Hereaus Die Top System。由于銅中介層的厚度,采用機(jī)械鉆孔來(lái)制造鍍Cu連接通孔。

如上所述,主流PCB嵌入工藝要求芯片銅金屬化,這非標(biāo)準(zhǔn)的。為了能夠嵌入具有標(biāo)準(zhǔn)鋁金屬化的功率器件,Pascal等人開(kāi)發(fā)了基于壓制金屬泡沫的頂部觸點(diǎn)。圖5(d)顯示了制造過(guò)程:首先,將芯片焊接到PCB基板上。然后,將帶有芯片切口的預(yù)浸料放置在頂部,然后是帶有芯片接觸焊盤(pán)開(kāi)口的聚酰亞胺掩模。帶有切口的額外預(yù)浸料層堆疊在頂部。金屬泡沫墊插入這些切口中。最后,在頂部放置第二塊PCB,并對(duì)整個(gè)堆疊進(jìn)行真空層壓。芯片和頂部PCB之間的電接觸是通過(guò)壓制的鎳泡沫建立的,鎳泡沫由預(yù)浸料中的樹(shù)脂保持在適當(dāng)?shù)奈恢谩Mㄟ^(guò)被動(dòng)熱循環(huán)、電流浪涌和重復(fù)短路測(cè)試了觸點(diǎn)的可靠性。一些樣品的性能與引線(xiàn)鍵合觸點(diǎn)一樣好,表明了該技術(shù)的潛力。

Djuric等人研究了另一種用于頂部和底部互連的新型互連技術(shù)。互連基于在電鍍銅臺(tái)面結(jié)構(gòu)上產(chǎn)生的銅納米線(xiàn)。PCB堆疊中的die組裝是在單個(gè)層壓步驟中進(jìn)行的,其中納米線(xiàn)和芯片金屬化之間的永久接觸是通過(guò)熱壓接合形成的。作者報(bào)告了200μ?至400μ?范圍內(nèi)的電阻,取決于溫度。

Polezhaev等人研究了一種嵌入過(guò)程,其中半導(dǎo)體夾在兩個(gè)PCB之間。如圖5(e)所示,半導(dǎo)體和銅帶通過(guò)銀燒結(jié)倒裝連接到頂部PCB。底部填充物用于芯片的機(jī)械支撐。燒結(jié)漿料被模板印刷(stencil-printed)到底部PCB的芯片焊盤(pán)上。頂部PCB面朝下放置在底部PCB上,中間有預(yù)浸料。通過(guò)芯片觸點(diǎn)的銀燒結(jié)和預(yù)浸料在剩余區(qū)域上的層壓來(lái)一起進(jìn)行粘合。關(guān)鍵的挑戰(zhàn)是找到一個(gè)可接受的層壓和燒結(jié)工藝窗口。需要一種用于無(wú)壓燒結(jié)的銀漿和基于苯并惡嗪樹(shù)脂的特殊預(yù)浸料。作者報(bào)告了在雙脈沖測(cè)試中的成功展示。

Tablati等人(2020)研究了使用IMS代替PCB作為頂部和底部基板的類(lèi)似制造概念。具有1.75 m?導(dǎo)通電阻的MOSFET用于技術(shù)演示。然而,根據(jù)作者的說(shuō)法,組裝后觀察到電阻增加了6.7 m?,這可能表明燒結(jié)接觸不良。

3、材料

介電材料在PCB嵌入中起著至關(guān)重要的作用,有各種形式,如芯(core)、樹(shù)脂涂層銅RCC(resin-coated copper)、片材(sheet material)或預(yù)浸漬玻璃纖維織物(pre-impregnated glass-fiber fabrics)。Core材料是具有完全固化電介質(zhì)的覆銅層壓板,用作大多數(shù)電路板的基礎(chǔ)。多層板是通過(guò)在RCC、片材或預(yù)浸料中添加更多的銅層而制成的,這些材料都含有部分固化的樹(shù)脂,可以起到粘合劑和電介質(zhì)的作用。片材含有樹(shù)脂和填料顆粒,而預(yù)浸料還含有玻璃纖維織物。RCC是應(yīng)用于銅箔的片材。材料供應(yīng)商提供各種各樣的產(chǎn)品,這些產(chǎn)品在樹(shù)脂配方和填料成分上有所不同。要選擇合適的PCB嵌入材料,了解材料特性和要求是必不可少的。接下來(lái)的小節(jié)詳細(xì)介紹了材料要求,并介紹了一些選定的材料。

3.1. 材料要求

在選擇任何嵌入材料時(shí),需要考慮熱、機(jī)械、電氣和制造相關(guān)性能。

在IPC-TM-650中的材料數(shù)據(jù)表規(guī)定了玻璃化轉(zhuǎn)變溫度、分解溫度以及在260°C和288°C下分層的時(shí)間。樹(shù)脂的玻璃化轉(zhuǎn)變溫度通常被認(rèn)為是上限,在設(shè)備運(yùn)行過(guò)程中不應(yīng)超過(guò)。在嵌入式封裝中,材料與半導(dǎo)體芯片直接接觸,在最先進(jìn)的器件中,半導(dǎo)體芯片可以在175℃的結(jié)溫下工作,未來(lái)的SiC器件可能超過(guò)200 ℃。熱損失通過(guò)底部的電絕緣材料傳遞到散熱器,見(jiàn)圖4(b)。這些材料需要提供高導(dǎo)熱性和良好的電絕緣性。通常,針對(duì)不同目的進(jìn)行優(yōu)化材料選擇,如在頂部嵌入,如在底部隔離。

擊穿電壓和介電強(qiáng)度是與絕緣性能相關(guān)的材料特性。典型的有機(jī)隔離器的介電強(qiáng)度在40~50 kV/mm范圍內(nèi)。然而,系統(tǒng)整個(gè)生命周期的長(zhǎng)期穩(wěn)定性值得關(guān)注。導(dǎo)電陽(yáng)極絲(Conductive anodic filament CAF)的生長(zhǎng)是一個(gè)已知的,可能會(huì)導(dǎo)致PCB材料的絕緣失效的問(wèn)題。在溫度、濕度和電壓偏壓下,電化學(xué)反應(yīng)會(huì)沿玻璃纖維產(chǎn)生導(dǎo)電銅路徑,并最終導(dǎo)致短路。CAF取決于許多難以量化的因素。因此,材料供應(yīng)商在通過(guò)IPC-TM 650方法2.6.25的標(biāo)準(zhǔn)化測(cè)試程序后,將材料按“CAF resistant”分級(jí)。

重要的機(jī)械性能是熱膨脹系數(shù)(coefficient of thermal expansion)和楊氏模量(Young′s modulus)。如第2.3.3節(jié)所述,這些部件負(fù)責(zé)封裝中的機(jī)械應(yīng)力。x和y方向CTE(平面內(nèi))在半導(dǎo)體芯片上產(chǎn)生應(yīng)力。z軸CTE(橫截面)應(yīng)與Cu(17.7ppm/K)相匹配,以限制微孔上的軸向應(yīng)力。

與加工相關(guān)的材料性能也值得關(guān)注。樹(shù)脂必須填充到內(nèi)嵌堆疊的空隙中。這要求在層壓過(guò)程中樹(shù)脂良好流動(dòng)性。通常,填料顆粒對(duì)流動(dòng)性有負(fù)面影響,但可以提高導(dǎo)熱性并降低CTE。此外,高填料含量可能對(duì)通過(guò)機(jī)械工具或激光加工通孔產(chǎn)生負(fù)面影響。雖然這些特性對(duì)材料選擇很重要,但數(shù)據(jù)表中沒(méi)有這些特性的量化數(shù)據(jù),因此材料選擇需要一些經(jīng)驗(yàn)。

3.2. 選定的材料

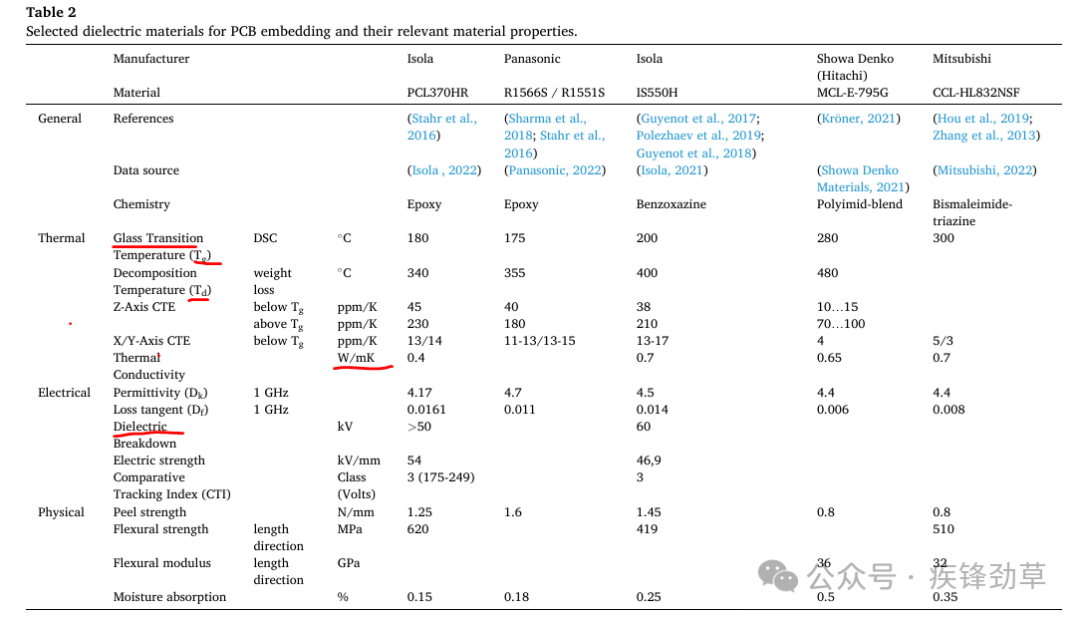

盡管許多科學(xué)出版物都涉及PCB嵌入,但關(guān)于材料選擇的詳細(xì)信息很少。只有少數(shù)出版物明確提到了研究中使用的制造商和材料類(lèi)型。表2列出了出版物中明確命名的材料。表中引用了相應(yīng)的參考文獻(xiàn)以及材料特性的數(shù)據(jù)源。該列表包括玻璃化轉(zhuǎn)變溫度為175℃和180℃的環(huán)氧基材料。這些材料的平面內(nèi)CTE在13~15 ppm/K范圍內(nèi),導(dǎo)熱性低,這表明填料含量低,加工過(guò)程中流動(dòng)性好。與Cu的粘附力大于1N/mm,吸濕率低于0.2%。基于苯并惡嗪(benzoxazine 200℃)、聚酰亞胺共混物(polyimide-blend 280℃)和雙馬來(lái)酰亞胺三嗪(bismaleimide-triazine300℃)的材料具有更高的玻璃化轉(zhuǎn)變溫度。后兩者是微電子封裝中用作基板的材料,因此具有極低的CTE(3~5ppm/K)。與標(biāo)準(zhǔn)環(huán)氧基材料相比,它們顯示出更高的吸濕性和更低的剝離強(qiáng)度(peel strength)。

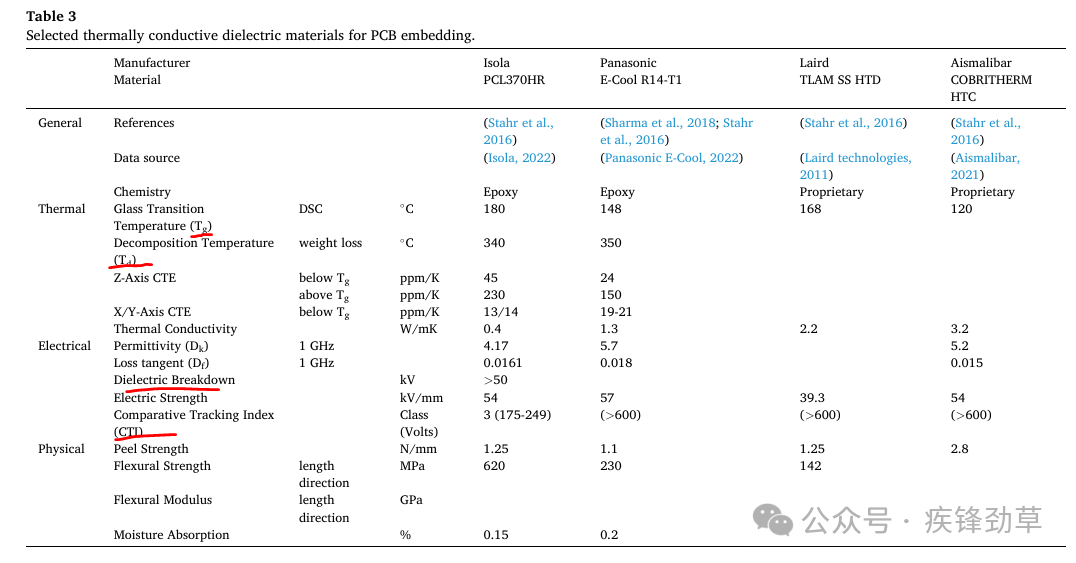

表3列出了用于嵌入式封裝底部導(dǎo)熱隔離的電介質(zhì),如圖4(b)所示。該列表包括導(dǎo)熱系數(shù)為0.4 W/mK的標(biāo)準(zhǔn)環(huán)氧基預(yù)浸料和導(dǎo)熱系數(shù)為1.3 W/mK增強(qiáng)的環(huán)氧基預(yù)浸漬料。為了提高導(dǎo)熱性,在樹(shù)脂中添加了陶瓷填料顆粒。然而,高填料含量對(duì)加工過(guò)程中樹(shù)脂的流動(dòng)性有負(fù)面影響。因此,這些材料的使用僅限于具有低自由體積的幾何形狀。導(dǎo)熱系數(shù)超過(guò)2 W/mK的材料可從隔離金屬基板(IMS)技術(shù)中獲得。這些是不含玻璃纖維織物的高填充樹(shù)脂片材。

4、實(shí)物展示

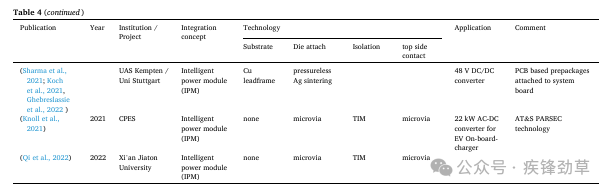

在過(guò)去的十年中,許多科學(xué)論文都描述了PCB嵌入式功率半導(dǎo)體。表4按時(shí)間順序顯示了各種研究示例的簡(jiǎn)要但全面的列表。該列表包括僅用于開(kāi)關(guān)級(jí)測(cè)試的簡(jiǎn)單技術(shù)演示和專(zhuān)用應(yīng)用場(chǎng)景的變換器級(jí)演示。它們涵蓋了所有類(lèi)型的集成概念,如PCB嵌入式功率模塊、智能功率模塊(IPM)和板上系統(tǒng)解決方案。在某些情況下,很難進(jìn)行嚴(yán)格的分類(lèi),因此在整合概念中添加了額外的信息。接下來(lái)的列將詳細(xì)介紹嵌入工藝技術(shù)。基板、底側(cè)芯片連接(die-attach)和頂側(cè)連接以及電氣隔離的信息如表后續(xù)部分所示。最后兩列列出了作者的應(yīng)用案例,以及對(duì)示例產(chǎn)品獨(dú)特功能或進(jìn)一步細(xì)節(jié)的評(píng)論。

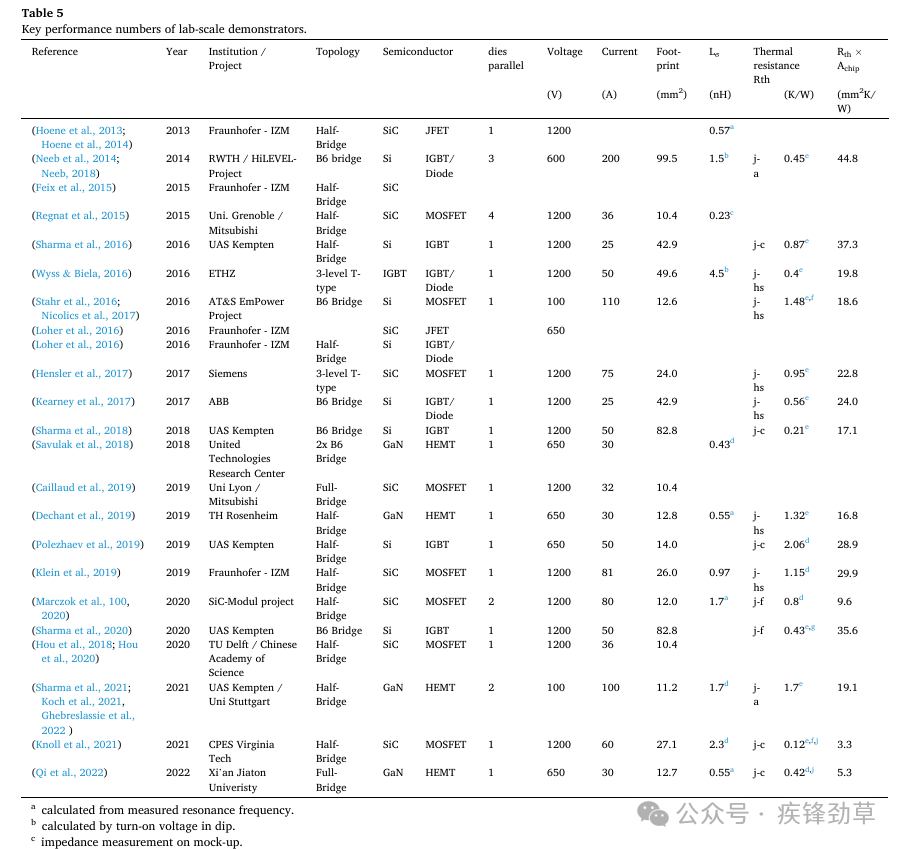

表5列出了相同的實(shí)物示例,并提供了技術(shù)細(xì)節(jié),如拓?fù)浣Y(jié)構(gòu)、芯片類(lèi)型和額定值、并聯(lián)芯片數(shù)量以及關(guān)鍵性能指標(biāo)雜散電感和熱阻。該表包括22個(gè)展示(12×半橋拓?fù)洹?×B6橋、2×全橋、2 x 3電平T型phase legs)。所有常見(jiàn)類(lèi)型的功率半導(dǎo)體,Si IGBT、二極管和MOSFET、SiC MOSFET和GaN HEMT,都已得到應(yīng)用。額定阻斷電壓大多為650 V或1200 V,只有兩個(gè)例外在100 V范圍內(nèi)。換向回路的雜散電感Lσ已在11個(gè)演示中公開(kāi)。如第2.4節(jié)所述三維堆疊PCOC概念報(bào)道了最低電感(0.23 nH)。對(duì)于具有GaN HEMT的半橋,已經(jīng)報(bào)道了0.5nH范圍內(nèi)的雜散電感。為了實(shí)現(xiàn)這些值,必須將DC link電容器直接放置在嵌入式半導(dǎo)體的頂部。GaN器件受益于其橫向結(jié)構(gòu),因?yàn)榇怪彪娏鳝h(huán)可以最小化。垂直器件導(dǎo)致更高的雜散電感值,通常在1nH到2nH的范圍內(nèi)。

在實(shí)際應(yīng)用中,功率半導(dǎo)體的載流能力受到封裝和冷卻系統(tǒng)熱性能的限制。性能指標(biāo)是熱阻,它與芯片結(jié)和封裝外殼之間的溫差(Rth-jc)、散熱器(Rth-jhs)、環(huán)境溫度(Rth-ja)或冷卻液體溫度(Rth-jf)成正比。此外,熱流密度以及芯片占用面積對(duì)熱阻有很強(qiáng)的影響。為了比較不同芯片尺寸封裝技術(shù)的熱性能,面積無(wú)關(guān)熱阻Rth×Achip提供了一種很好的測(cè)量方法。該屬性列于表5的最后一列。面積無(wú)關(guān)結(jié)到散熱器熱阻的典型值在20~30 mm2K/W的范圍內(nèi)。通過(guò)雙面冷卻(18.6 mm2K/W)和直接液體冷卻(9.6 mm2K/W)實(shí)現(xiàn)了較低的值。報(bào)告的最低值(3.3 mm2K/W和5.3 mm2K/W)不包括電絕緣。

5.可靠性

可靠性對(duì)任何電子封裝技術(shù)都是強(qiáng)制性的要求。為了驗(yàn)證可靠性,必須根據(jù)特定應(yīng)用標(biāo)準(zhǔn)進(jìn)行耐久性測(cè)試并通過(guò)。汽車(chē)認(rèn)證指南AQG324,正式名稱(chēng)為L(zhǎng)V324,是此類(lèi)標(biāo)準(zhǔn)的一個(gè)例子,與汽車(chē)傳動(dòng)系統(tǒng)中的功率模塊相關(guān)。該標(biāo)準(zhǔn)描述了功率模塊符合應(yīng)用環(huán)境和壽命的測(cè)試方法。個(gè)別測(cè)試方法旨在觸發(fā)某些眾所周知的故障模式,并要求通過(guò)規(guī)定的最低驗(yàn)收標(biāo)準(zhǔn)。由于電動(dòng)汽車(chē)是PCB嵌入的目標(biāo)應(yīng)用,AQG324為初始可靠性測(cè)試提供了良好的基礎(chǔ)。然而,新的故障模式可能與PCB嵌入式封裝相關(guān),可能需要額外的測(cè)試方法。以下小節(jié)涵蓋了對(duì)熱機(jī)械應(yīng)力引起的故障和絕緣行為的調(diào)查。

5.1. 熱機(jī)械可靠性

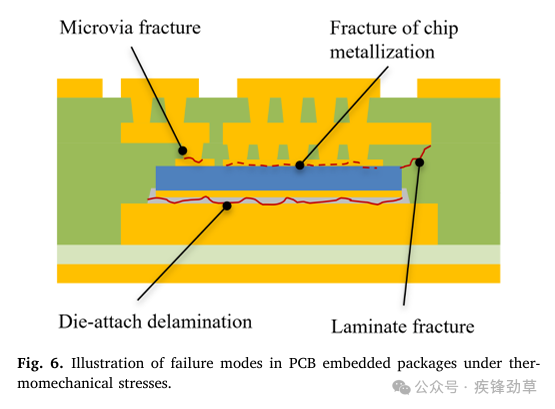

Yang等人對(duì)嵌入式MOSFET封裝的可靠性進(jìn)行了數(shù)值研究。基于有限元法(FEM)仿真,作者確定了嵌入式MOSFET封裝中的臨界熱機(jī)械應(yīng)力。這些應(yīng)力可能引發(fā)以下故障模式:

(1) 制造過(guò)程中的芯片開(kāi)裂,如第2.3.3節(jié)所述。

(2) 銅過(guò)孔開(kāi)裂或分層

(3) 銅芯片金屬化分層

圖6顯示了示意性橫截面中的故障模式。此外,還包括層壓板斷裂和芯片附著分層。

實(shí)驗(yàn)測(cè)試需要使用溫度沖擊室進(jìn)行被動(dòng)溫度循環(huán),或使用電流脈沖定期加熱半導(dǎo)體的主動(dòng)負(fù)載循環(huán)。

Munding等人在被動(dòng)溫度循環(huán)(-55至150℃)后觀察到以RCC作為嵌入材料的樣品出現(xiàn)層壓板開(kāi)裂。然而,當(dāng)使用預(yù)浸料代替時(shí),沒(méi)有出現(xiàn)裂紋。預(yù)浸玻璃纖維提高了介電材料的機(jī)械強(qiáng)度。Pavliˇcek等人觀察到,在500次熱循環(huán)(-50至150?C)后,帶有SiC芯片的PCB-prepackage中的燒結(jié)die-attach分層)。Birkhold等人在-40至200°C下進(jìn)行1000次循環(huán)后也進(jìn)行了類(lèi)似的觀察。在同一項(xiàng)研究中,報(bào)告了通孔分層和金屬化斷裂。通孔分層是由嵌入材料和鍍銅通孔之間的CTE差異引起的軸向應(yīng)力引起的。FR4材料的z軸CTE在40ppm/K的范圍內(nèi),而Cu的CTE為17.7ppm/K,見(jiàn)表1。由于微孔的圓錐形,斷裂發(fā)生在底部,那里的橫截面積最小。芯片金屬化中的裂紋是由金屬和半導(dǎo)體芯片之間的CTE差異引起的。通常,Cu被鍍?cè)贏l金屬化的頂部。鋁的抗拉強(qiáng)度明顯低于銅。因此,裂紋主要出現(xiàn)在鋁層。

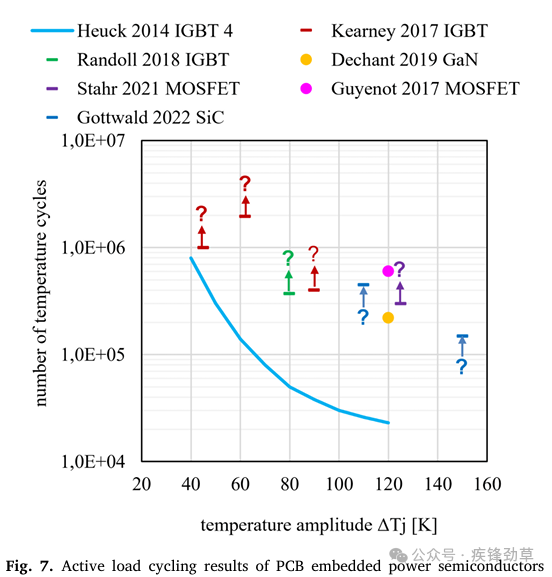

圖7總結(jié)了主動(dòng)負(fù)載循環(huán)試驗(yàn)的結(jié)果。該圖顯示了溫度幅值與失效循環(huán)次數(shù)的關(guān)系。為了基準(zhǔn)測(cè)試,由藍(lán)線(xiàn)表示了傳統(tǒng)基于DBC的引線(xiàn)鍵合功率模塊的結(jié)果。Kearney等人對(duì)一組嵌入式IGBT模塊進(jìn)行了測(cè)試,這些模塊首先在42K的溫差下循環(huán)了100萬(wàn)次。然后,在增加溫差之前,將相同的樣品在62 K下循環(huán)近200萬(wàn)次。在90 K下進(jìn)行40萬(wàn)次循環(huán)后,測(cè)試中止,未出現(xiàn)任何故障。因此,圖中的結(jié)果表示一個(gè)下限,該下限由水平條上方的箭頭和問(wèn)號(hào)表示。Randoll等人對(duì)ΔT=80K的IGBT模塊進(jìn)行了功率循環(huán)測(cè)試,該測(cè)試在370.000次無(wú)故障循環(huán)后中止。Stahr等人在ΔT=125K下,在高達(dá)300.000次循環(huán)中沒(méi)有觀察到MOSFET模塊發(fā)生任何故障。Guyenot在ΔT=120 K下進(jìn)行60萬(wàn)次循環(huán)后,在MOSFET模塊上觀察到熱阻的臨界增加。焊料die-attach分層是故障的根本原因。Dechnat等人通過(guò)在120℃下220.000次循環(huán)后,GaN HEMT的分層。Gottwald等人報(bào)告了一項(xiàng)測(cè)試活動(dòng),其中SiC模塊的樣本數(shù)量更多(未量化)。為了突出該技術(shù)的潛力,他們?cè)诔霭嫖镏姓故玖俗罡叩墓收涎h(huán)次數(shù)。在這種情況下,這些值表示上限。與傳統(tǒng)的引線(xiàn)鍵合功率模塊相比,嵌入式模塊的所有報(bào)告結(jié)果都表明負(fù)載循環(huán)能力明顯提高。

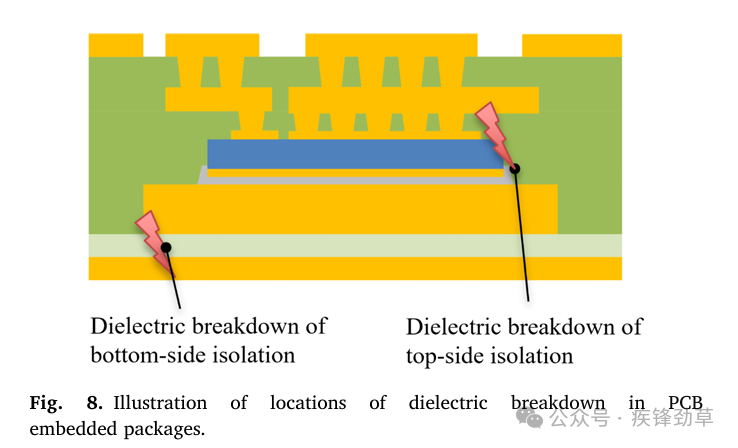

5.2. 絕緣性能

圖8顯示了通用PCB嵌入式功率模塊的橫截面。電介質(zhì)擊穿可能發(fā)生在電場(chǎng)強(qiáng)度高的位置。這些位于芯片頂部,在那里,全工作電壓施加在中心接觸焊盤(pán)和保護(hù)環(huán)之間。第二個(gè)關(guān)鍵位置是底部隔離,因?yàn)闊峤佑|焊盤(pán)通常連接到GND電位。

5.2.1. 底部絕緣

Randoll研究了導(dǎo)熱預(yù)浸料的絕緣性能。使用頂部和底部帶有方形電極的材料樣品進(jìn)行局部放電測(cè)試。本文報(bào)道了在25℃至175℃的溫度范圍內(nèi)的局部放電熄滅電壓(partial discharge extinction voltage PDEV)。在150℃的玻璃化轉(zhuǎn)變溫度下,獲得了4.0至7.0 V的PDEV。在175℃下 PDEV降至1.5 kV。因此,在施加高壓時(shí),嵌入材料在操作過(guò)程中不應(yīng)超過(guò)Tg。

Kearney等人使用了從文獻(xiàn)中獲得的130μm厚的1200 V IGBT模塊。圓形標(biāo)記表示失敗。上方帶有箭頭的水平條表示測(cè)試在故障發(fā)生之前中止,并顯示下限。下面帶有箭頭的水平條表示幾個(gè)樣本失敗,并報(bào)告了最高的循環(huán)次數(shù),這表示上限。藍(lán)線(xiàn)表示傳統(tǒng)引線(xiàn)鍵合功率模塊的功率循環(huán)能力,數(shù)據(jù)來(lái)自(Heuck等人,2014)。

用于評(píng)估底部絕緣的絕緣層。在初始狀態(tài)和老化500次熱循環(huán)(-40℃至150℃)后測(cè)量介電強(qiáng)度和局部放電起始電壓(PDIV)。初始樣品的擊穿電壓在5.3 kV至6.5 kV之間,PDIV在4.7 kV的范圍內(nèi)。老化后,擊穿電壓降至4.2 kV至4.7 kV,PDIV降至3.5V至4.1 kV。在90℃、2.5kV的測(cè)試電壓下進(jìn)行了長(zhǎng)期老化實(shí)驗(yàn)。根據(jù)結(jié)果推斷,使用壽命為15至30年。5.2.2. 頂部絕緣

Dechant等人研究了嵌入式650V GaN HEMT的介電強(qiáng)度。源極和漏極接觸都位于芯片的頂部,并形成叉指(interdigital)結(jié)構(gòu)。第一封裝布線(xiàn)層放置在頂部,由100μm厚的電介質(zhì)隔開(kāi),電介質(zhì)需要承受芯片的全部阻斷電壓。在25?C下測(cè)試時(shí),報(bào)告的特征擊穿電壓為14.7 kV。然而,該值在較高溫度下會(huì)顯著降低。在125℃下測(cè)得降低了77%。與此相反,高溫儲(chǔ)存導(dǎo)致室溫?fù)舸╇妷荷摺_@種效應(yīng)可以用樹(shù)脂中的致密化過(guò)程來(lái)解釋?zhuān)@會(huì)導(dǎo)致初始缺陷的恢復(fù)。致密化過(guò)程在高溫儲(chǔ)存約2000小時(shí)后結(jié)束。由于樹(shù)脂的老化,進(jìn)一步的高溫暴露預(yù)計(jì)會(huì)降低擊穿強(qiáng)度。

Link等人對(duì)嵌入式1200 V二極管進(jìn)行了高濕高溫反向偏壓(H3TRB)測(cè)試。樣品在85℃的溫度、85%的相對(duì)濕度和960V的偏壓下暴露1000小時(shí),偏壓等于標(biāo)稱(chēng)阻斷電壓的80%。該程序是功率模塊的標(biāo)準(zhǔn)測(cè)試,旨在測(cè)試芯片鈍化。測(cè)試條件與根據(jù)IPC-TM-650的CAF測(cè)試相當(dāng),盡管電壓更高。最初的一組樣本未通過(guò)測(cè)試,顯示漏電流增加。芯片聚酰亞胺鈍化層的剝離被確定為根本原因。在第二組改進(jìn)的樣本中,四分之三通過(guò)了測(cè)試。

Frühauf等人將TST和HRTRB測(cè)試相結(jié)合,研究熱機(jī)械損傷和電絕緣損失之間的相互關(guān)系。該測(cè)試是在帶有PCB嵌入式邏輯芯片和功率MOSFET的低壓系統(tǒng)封裝上進(jìn)行的。首先,將樣品暴露于100次熱沖擊循環(huán)中,以觸發(fā)機(jī)械老化。然后,將樣品暴露于H3TRB條件下100小時(shí)。沒(méi)有報(bào)告偏置電壓,但是,SiP的輸入電壓指定為18V,因此可以假設(shè)為低電壓偏置。將該序列重復(fù)五次,在中間測(cè)量中觀察到漏電流的穩(wěn)定增加。然而,即使在測(cè)試結(jié)束后,最大漏電流仍遠(yuǎn)低于設(shè)備的規(guī)格。

6、結(jié)論與展望

本文回顧了將有源功率半導(dǎo)體器件嵌入PCB的科學(xué)文獻(xiàn)。制造技術(shù)可分為三種基本工藝:Chip-on-Substrate、 Chip-in-Cavity和 Double-side Microvia工藝。如今,PCB供應(yīng)商使用這些工藝,有時(shí)會(huì)稍作修改。所有這些都需要具有Cu金屬化的半導(dǎo)體芯片,這仍然是一個(gè)挑戰(zhàn),因?yàn)楣β拾雽?dǎo)體通常在頂部具有Al金屬化,在底側(cè)具有Ag金屬化。文獻(xiàn)中已經(jīng)介紹了在頂部應(yīng)用銅金屬化的幾種方法,并討論了后續(xù)激光鉆孔以形成接觸的要求。學(xué)術(shù)研究提出了一些嵌入式芯片電連接的替代方法,如燒結(jié)銅板(sintered Cu plates)、金屬泡沫觸點(diǎn)(metal-foam contacts)或銅納米線(xiàn)的熱壓接合。所有這些方法都還處于研究階段。

層壓材料的選擇是另一個(gè)重要課題。在大多數(shù)情況下,電路板依賴(lài)于環(huán)氧基層壓板。其他樹(shù)脂材料,如苯并惡嗪、聚酰亞胺共混物或雙馬來(lái)酰亞胺-三嗪,具有更高的玻璃化轉(zhuǎn)變溫度,在運(yùn)行中可能使半導(dǎo)體結(jié)溫高達(dá)200℃。此外,它們提供了較低的CTE值,這降低了異質(zhì)材料堆疊中的固有熱機(jī)械應(yīng)力。

科學(xué)文獻(xiàn)中公開(kāi)了許多PCB嵌入式功率封裝的示例。這些示例包括標(biāo)稱(chēng)阻斷電壓高達(dá)1200 V的所有常見(jiàn)類(lèi)型的功率半導(dǎo)體。PCB嵌入的一個(gè)關(guān)鍵好處是平面結(jié)構(gòu),這使得低雜散電感設(shè)計(jì)成為可能。通過(guò)集成DC link路電容器,開(kāi)關(guān)單元的換相回路電感可以降低到遠(yuǎn)低于1nH,這是寬帶隙半導(dǎo)體快速干凈開(kāi)關(guān)所必需的。該數(shù)字比現(xiàn)有功率模塊的雜散電感低一個(gè)數(shù)量級(jí)以上,例如英飛凌FS50R12W2T7,典型值Lsce=40nH。另一方面,具有大面積軌跡的平面結(jié)構(gòu)會(huì)產(chǎn)生寄生電容。眾所周知,這些寄生電容會(huì)導(dǎo)致接地電流和電磁干擾問(wèn)題。到目前為止,這個(gè)話(huà)題在PCB嵌入文獻(xiàn)中很少受到關(guān)注。

使用厚銅基板可以有效地從半導(dǎo)體中散熱。典型的芯片面積無(wú)關(guān)熱阻在20~40 mm2 K/W的范圍內(nèi)。這個(gè)數(shù)字與Al2O3 DBC基板的傳統(tǒng)功率模塊40mm2 k/w相當(dāng)(英飛凌FS50R12W2T7 Rthjhs=0.955,Achip=41mm)。通過(guò)雙面冷卻或集成液體冷卻實(shí)現(xiàn)了熱阻的進(jìn)一步降低。

在討論P(yáng)CB嵌入時(shí),有機(jī)絕緣材料的使用通常是一個(gè)值得關(guān)注的問(wèn)題。幾項(xiàng)研究報(bào)告稱(chēng),即使對(duì)于薄至100μm的電介質(zhì),擊穿電壓也超過(guò)5.0 kV。然而,介電強(qiáng)度在高溫下和由于溫度循環(huán)而降低。此外,PCB行業(yè)中被稱(chēng)為CAF的銅跡線(xiàn)的增長(zhǎng)仍然令人擔(dān)憂(yōu),需要進(jìn)一步研究。熱機(jī)械應(yīng)力和高溫高濕電壓偏置的結(jié)合可能對(duì)高壓應(yīng)用至關(guān)重要。

據(jù)一些研究人員稱(chēng),在panel級(jí)別制造嵌入式結(jié)構(gòu)可能會(huì)帶來(lái)成本效益。然而,沒(méi)有科學(xué)研究支持這一說(shuō)法。顯然,商業(yè)PCB供應(yīng)商的成本結(jié)構(gòu)是高度機(jī)密的,因此不會(huì)在出版物中討論。然而,在成本敏感的低功耗領(lǐng)域,各種具有嵌入式芯片的SiP證明了該技術(shù)的成功商業(yè)應(yīng)用。對(duì)于更高功率的應(yīng)用,只有少數(shù)商業(yè)產(chǎn)品,如GaN Systems的GaN PX嵌入式封裝。首款應(yīng)用于48V輕度混合動(dòng)力傳動(dòng)系統(tǒng)的System-in-Board轉(zhuǎn)換器已經(jīng)宣布,計(jì)劃于2021年開(kāi)始生產(chǎn)。更高電壓的應(yīng)用,如電動(dòng)汽車(chē)牽引逆變器、車(chē)載充電器和DC/DC轉(zhuǎn)換器,正在主要技術(shù)供應(yīng)商的路線(xiàn)圖上。目前,歐洲和亞洲正在建立專(zhuān)門(mén)的開(kāi)發(fā)和生產(chǎn)能力。經(jīng)過(guò)十多年的研究,這項(xiàng)技術(shù)似乎終于準(zhǔn)備走出實(shí)驗(yàn)室,變成現(xiàn)實(shí)世界的產(chǎn)品。

-

pcb

+關(guān)注

關(guān)注

4323文章

23130瀏覽量

398843 -

功率半導(dǎo)體

+關(guān)注

關(guān)注

22文章

1171瀏覽量

43062

原文標(biāo)題:功率半導(dǎo)體嵌入PCB:綜述(PCB embedded power semi: A technology review )

文章出處:【微信號(hào):深圳市賽姆烯金科技有限公司,微信公眾號(hào):深圳市賽姆烯金科技有限公司】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

功率器件熱設(shè)計(jì)基礎(chǔ)(十二)——功率半導(dǎo)體器件的PCB設(shè)計(jì)

PCB嵌入式功率芯片封裝,從48V到1200V

功率器件熱設(shè)計(jì)基礎(chǔ)(十一)——功率半導(dǎo)體器件的功率端子

功率器件嵌入PCB技術(shù)文章分享

瑞能半導(dǎo)體斬獲亞洲金選獎(jiǎng)功率半導(dǎo)體產(chǎn)品大獎(jiǎng)

功率器件熱設(shè)計(jì)基礎(chǔ)(一)——功率半導(dǎo)體的熱阻

PCB半導(dǎo)體封裝板:半導(dǎo)體產(chǎn)業(yè)的堅(jiān)實(shí)基石

功率半導(dǎo)體和寬禁半導(dǎo)體的區(qū)別

功率半導(dǎo)體的封裝方式有哪些

半導(dǎo)體芯片鍵合裝備綜述

功率半導(dǎo)體技術(shù)如何助力節(jié)碳減排

半導(dǎo)體基礎(chǔ)功率模塊與離散元件的比較

功率半導(dǎo)體漲價(jià)?多家A股功率半導(dǎo)體企業(yè)回應(yīng)來(lái)了

新能源汽車(chē)崛起,功率半導(dǎo)體如何助力綠色出行?

功率半導(dǎo)體嵌入PCB綜述

功率半導(dǎo)體嵌入PCB綜述

評(píng)論