Hello,大家好,今天我們來聊聊,先進封裝中RDL工藝。

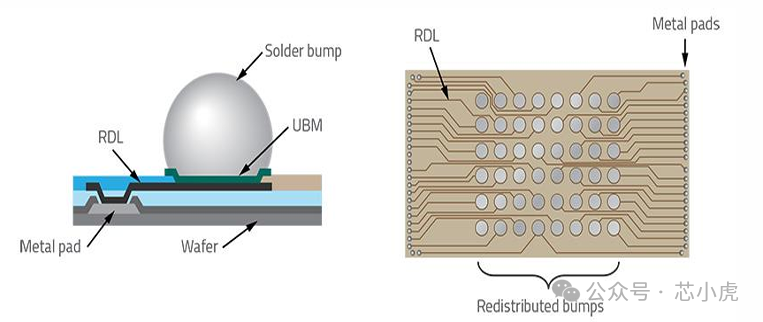

RDL:Re-Distribution Layer,稱之為重布線層。是先進封裝的關鍵互連工藝之一,目的是將多個芯片集成到單個封裝中。先在介電層頂部創(chuàng)建圖案化金屬層,然后將IC的輸入/輸出(I/O)重新分配到新位置。新位置通常位于芯片邊緣,可以使用標準表面貼裝技術(SMT)將 IC連接到印刷電路板(PCB)。 RDL工藝使得設計人員能夠以緊湊且高效的方式放置芯片,從而減少器件的整體占地面積。

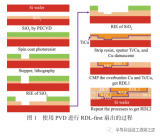

資料來源:Lam Research

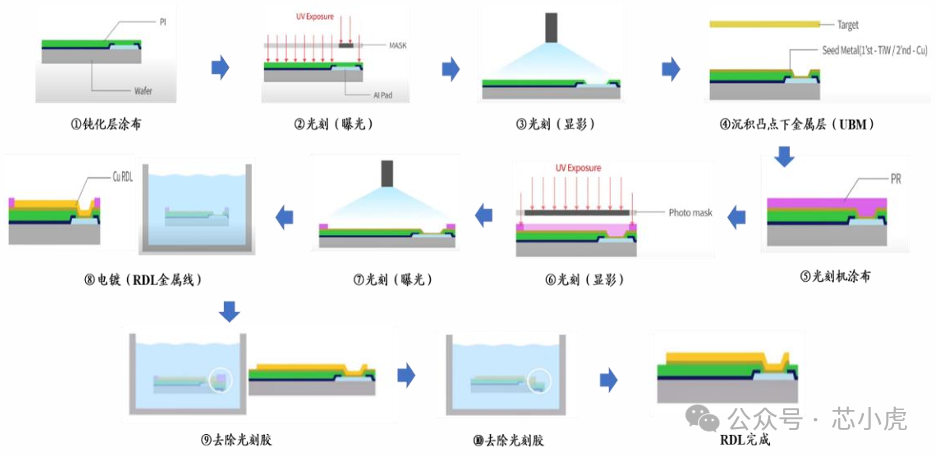

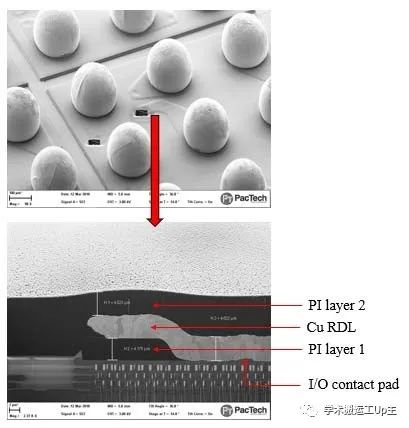

晶圓級金屬重布線制程在IC上涂布一層絕緣保護層,再以曝光顯影的方式定義新的導線圖案,然后利用電鍍技術制作新的金屬線路,以連接原來的芯片引腳和新的凸點,達到芯片引腳重新分布的目的。重布線層的金屬線路以電鍍銅材料為主,根據(jù)需要也可以在銅線路上鍍鎳金或者鎳鈀金材料,相關核心材料包括光刻膠、電鍍液、靶材、刻蝕液等。

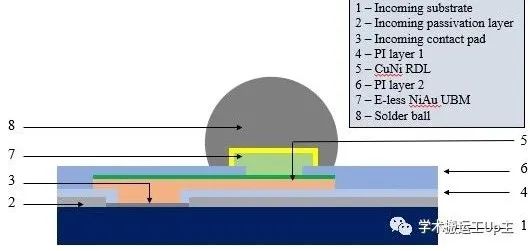

資料來源:SiP與先進封裝技術

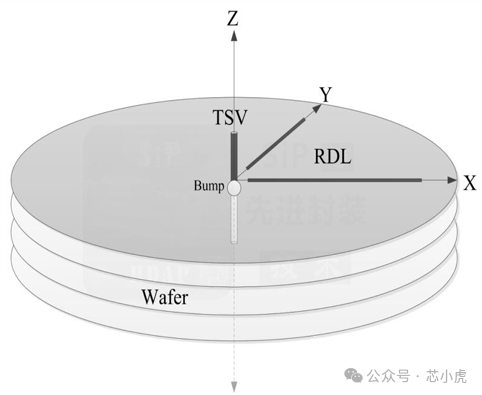

重布線層(RDL)在延伸和互連XY平面方面發(fā)揮關鍵作用。在扇入晶圓級封裝(FIWLP)和扇出晶圓級封裝(FOWLP)等先進封裝中,RDL 為核心關鍵工藝。 使得封裝廠能夠在扇出封裝技術方面與晶圓代工廠展開競爭。通過RDL,IO Pad可以制成FIWLP 或FOWLP 中不同類型的晶圓級封裝。在FIWLP中,凸塊全部生長在芯片上,芯片和焊盤之間的連接主要依靠RDL的金屬線。封裝后,IC的尺寸幾乎與芯片面積相同。在FOWLP中,凸塊可以生長在芯片外,封裝后的IC比芯片面積大(1.2倍)。

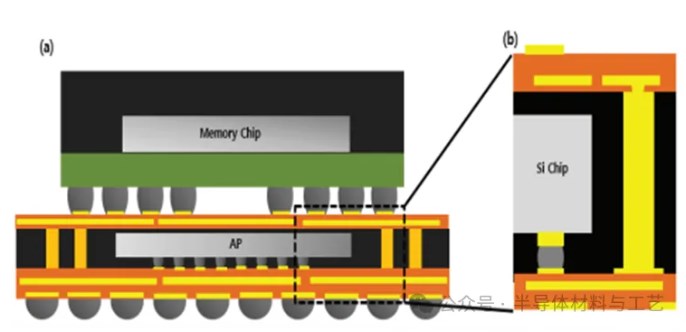

以2.5D先進封裝的代表臺積電的InFO為例,InFO在載體上使用一個或多個裸芯粒,然后將其嵌入到模塑料的重構晶圓中。并在晶圓上制造 RDL 互連和介電層, 這是“芯片優(yōu)先”的工藝流程。單芯片 InFO 提供高凸點數(shù)量,RDL 線從芯片區(qū)域向外延伸,形成“扇出”拓撲。

-

芯片

+關注

關注

456文章

50908瀏覽量

424485 -

工藝

+關注

關注

4文章

595瀏覽量

28828 -

先進封裝

+關注

關注

2文章

413瀏覽量

257

原文標題:什么是先進封裝中的RDL工藝

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

硅通孔封裝工藝流程與技術

先進封裝關鍵技術之TSV框架研究

晶圓級封裝中的窄間距RDL技術

先進封裝RDL-first工藝研究進展

集微連線:板級封裝潛力無窮 RDL工藝勇挑大梁

半導體先進封裝市場簡析(2022)

什么是先進封裝?先進封裝技術包括哪些技術

Manz亞智科技 RDL先進制程加速全球板級封裝部署和生產

芯片先進封裝里的RDL

Manz亞智科技RDL制程打造CoPoS板級封裝路線, 滿足FOPLP/TGV應用于下一代AI需求

Manz亞智科技RDL制程打造CoPoS板級封裝路線,滿足FOPLP/TGV應用于下一代AI需求

先進封裝中RDL工藝介紹

先進封裝中RDL工藝介紹

評論