邊界掃描介紹

邊界掃描(Boundary Scan)測(cè)試發(fā)展于上個(gè)世紀(jì)90年代,隨著大規(guī)模集成電路的出現(xiàn),印制電路板制造工藝向小,微,薄發(fā)展,傳統(tǒng)的ICT 測(cè)試已經(jīng)沒(méi)有辦法滿(mǎn)足這類(lèi)產(chǎn)品的測(cè)試要求。由于芯片的引腳多,元器件體積小,板的密度特別大,根本沒(méi)有辦法進(jìn)行下探針測(cè)試。一種新的測(cè)試技術(shù)產(chǎn)生了,聯(lián)合測(cè)試行為組織(Joint Test Action Group)簡(jiǎn)稱(chēng)JTAG 定義這種新的測(cè)試方法即邊界掃描測(cè)試。

隨著表面貼裝技術(shù)的使用,印制電路板(PCB)的密度越來(lái)越高,已不易采用傳統(tǒng)的針床測(cè)試技術(shù)。而增加電路測(cè)試點(diǎn)、對(duì)復(fù)雜電路增加附加的測(cè)試電路來(lái)進(jìn)行單獨(dú)測(cè)試等方法只是對(duì)傳統(tǒng)方法的改進(jìn),對(duì)提高電路可測(cè)性十分有限且通用性較差。為提高電路和系統(tǒng)的可測(cè)試性,1985年菲利浦電子公司首先倡議并聯(lián)合歐洲、北美和亞洲其他電子設(shè)備制造公司組建了聯(lián)合測(cè)試行動(dòng)組(Jo int TestA ction Group,JTA G)。1990年2月JTA G與TEEE標(biāo)準(zhǔn)化委員會(huì)合作提出了“標(biāo)準(zhǔn)測(cè)試訪(fǎng)問(wèn)通道與邊界掃描結(jié)構(gòu)”的IEEE114911 1990標(biāo)準(zhǔn)。該標(biāo)準(zhǔn)要求在集成電路中加入邊界掃描電路。在板級(jí)測(cè)試時(shí),可以在模式選擇的控制下,構(gòu)成一條就集成電路邊界繞行的移位寄存器鏈,對(duì)板內(nèi)集成電路的所有引腳進(jìn)行掃描,通過(guò)將測(cè)試數(shù)據(jù)串行輸入到該寄存器鏈的方法,檢查發(fā)現(xiàn)印刷電路板上的器件焊接故障和板內(nèi)連接故障,極大地方便了系統(tǒng)電路的調(diào)試。IEEE114911標(biāo)準(zhǔn)的推廣應(yīng)用引起測(cè)試設(shè)備和測(cè)試系統(tǒng)的重大變革,邊界掃描測(cè)試技術(shù)正日益成為超大規(guī)模集成電路的主流測(cè)試技術(shù)。

邊界掃描測(cè)試有2大優(yōu)點(diǎn):一個(gè)是方便芯片的故障定位,迅速準(zhǔn)確地測(cè)試兩個(gè)芯片管腳的連接是否可靠,提高測(cè)試檢驗(yàn)效率;另一個(gè)是,具有JTA G接口的芯片,內(nèi)置一些預(yù)先定義好的功能模式,通過(guò)邊界掃描通道使芯片處于某個(gè)特定的功能模式,以提高系統(tǒng)控制的靈活性和方便系統(tǒng)設(shè)計(jì)。

邊界掃描技術(shù)的含義

邊界掃描技術(shù)是一種應(yīng)用于數(shù)字集成電路器件的測(cè)試性結(jié)構(gòu)設(shè)計(jì)方法。所謂“邊界”是指測(cè)試電路被設(shè)置在集成電路器件功能邏輯電路的四周,位于靠近器件輸入、輸出引腳的邊界處。所謂“掃描”是指連接器件各輸入、輸出引腳的測(cè)試電路實(shí)際上是一個(gè)串行移位寄存器,這種串行移位寄存器被叫做“掃描路徑”,沿著這條路徑可輸入由“1”和“0”組成的各種編碼,對(duì)電路進(jìn)行“掃描”式檢測(cè),從輸出結(jié)果判斷其是否正確。

邊界掃描的硬件結(jié)構(gòu)

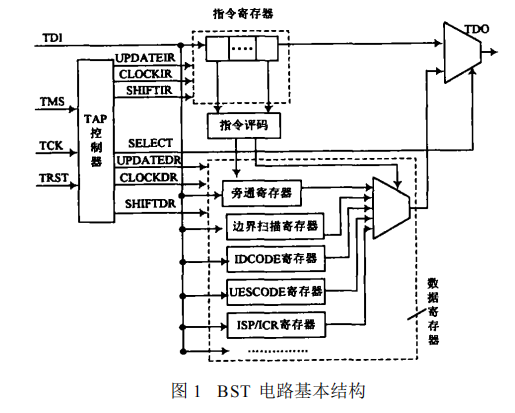

BST的核心思想是在芯片管腳和芯片內(nèi)部邏輯之間,即緊挨元件的每個(gè)輸入、輸出引腳處增加移位寄存器組,在PCB的測(cè)試模式下,寄存器單元在相應(yīng)的指令作用下,控制輸出引腳的狀態(tài),讀入輸入引腳的狀態(tài),從而允許用戶(hù)對(duì)PCB上的互連進(jìn)行測(cè)試。BST電路主要包括指令寄存器(IR)、旁路寄存器(BR)、邊界掃描寄存器(BSR)和測(cè)試訪(fǎng)問(wèn)端口(TA P)控制器。BST電路一般采用4線(xiàn)測(cè)試總線(xiàn)接口,如圖1所示,如果測(cè)試信號(hào)中有復(fù)位信號(hào)(nTRST),則采用5線(xiàn)測(cè)試總線(xiàn)接口。5個(gè)信號(hào)分別為:測(cè)試數(shù)據(jù)輸入總線(xiàn)(TD I),測(cè)試數(shù)據(jù)輸入至移位寄存器(SR);測(cè)試數(shù)據(jù)輸出總線(xiàn)(TDO),測(cè)試數(shù)據(jù)從SR移出;測(cè)試時(shí)鐘總線(xiàn)(TCK);測(cè)試模式選擇總線(xiàn)(TM S),控制各個(gè)測(cè)試過(guò)程,如選擇寄存器、加載數(shù)據(jù)、形成測(cè)試、移出結(jié)果等;復(fù)位信號(hào)總線(xiàn)(TRST),低電平有效。IEEEStd114911測(cè)試總線(xiàn)使用TCK的2個(gè)時(shí)鐘沿,TM S和TD I在TCK的上升沿被采樣,TDO在TCK的下降沿變化。

TA P 控制器

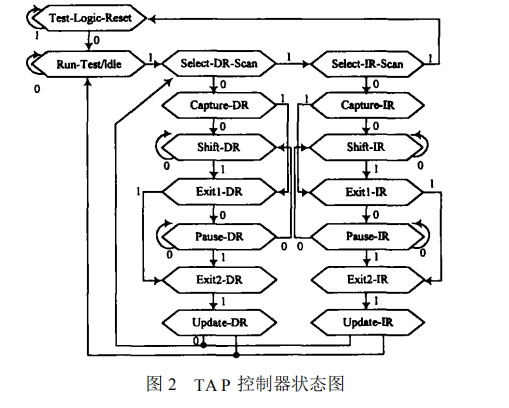

TA P控制器是邊界掃描測(cè)試的核心控制器。在TCK和TM S的控制下,可以選擇使用指令寄存器掃描或數(shù)據(jù)寄存器掃描,以及控制邊界掃描測(cè)試的各個(gè)狀態(tài)。TM S和TD I是在TCK的上升沿被采樣,TDO是在TCK的下降沿變化。TA P控制器的狀態(tài)機(jī)如圖2所示。右邊是指令寄存器分支,左邊是數(shù)據(jù)寄存器分支。

其中,TA P控制器的狀態(tài)機(jī)只有6個(gè)穩(wěn)定狀態(tài):測(cè)試邏輯復(fù)位(Test Logical Reset)、測(cè)試運(yùn)行?等待(RunTest?Idle)、數(shù)據(jù)寄存器移位(Shift DR)、數(shù)據(jù)寄存器移位暫停(Pause DR)、指令寄存器移位(Shift IR)、指令寄存器暫停(Pause IR):其他狀態(tài)都不是穩(wěn)態(tài),而只是暫態(tài)。

在上電或IC正常運(yùn)行時(shí),必須使TM S最少持續(xù)5個(gè)TCK保持為高電平,則TA P進(jìn)入測(cè)試邏輯復(fù)位態(tài)。這時(shí),TA P發(fā)出復(fù)位信號(hào)使所有的測(cè)試邏輯不影響元件的正常運(yùn)行。若需要進(jìn)行邊界掃描測(cè)試。可以在TM S與TCK的配合控制下,退出復(fù)位,進(jìn)入邊界掃描測(cè)試需要的各個(gè)狀態(tài)。需要測(cè)試時(shí),在TM S和TCK的控制下,TA P控制器跳出TLR狀態(tài),從選擇數(shù)據(jù)寄存器掃描(Shift DRScan)或選擇指令寄存器掃描(Shift IR Scan)進(jìn)入圖2所示的各個(gè)狀態(tài)。Shift DR Scan和Shift IR Scan兩個(gè)模塊的功能類(lèi)似。

進(jìn)入每個(gè)模塊的第一步是捕捉數(shù)據(jù)(Cap ture),對(duì)于數(shù)據(jù)寄存器,在Cap ture DR狀態(tài)把數(shù)據(jù)并行加載到相應(yīng)的串行數(shù)據(jù)通道中,對(duì)于指令寄存器,則是在Cap ture IR狀態(tài)把指令信息捕捉到指令寄存器中。TA P控制器從捕捉狀態(tài)進(jìn)入移位(Shift)或跳出1(Exit1)狀態(tài)。通常,Shift狀態(tài)緊跟Cap ture狀態(tài),數(shù)據(jù)在寄存器中移位。在Shift狀態(tài)之后,TA P控制器通過(guò)Exit1狀態(tài)進(jìn)入更新(U pdate)狀態(tài)或者暫停(Pause)狀態(tài)。在Pause狀態(tài),數(shù)據(jù)移位暫時(shí)終止,可以對(duì)數(shù)據(jù)寄存器或指令寄存器重新加載測(cè)試向量。從Pause狀態(tài)出來(lái)通過(guò)跳出2(Exit2)狀態(tài)可以再次進(jìn)入Shift狀態(tài)或者經(jīng)過(guò)U pdate狀態(tài)回到Run Test?Idle狀態(tài)。在U pdate狀態(tài),移入掃描通道的數(shù)據(jù)被輸出。

BST寄存器單元

測(cè)試數(shù)據(jù)寄存器

邊界掃描數(shù)據(jù)寄存器至少應(yīng)該包括3種:邊界掃描寄存器、器件標(biāo)識(shí)寄存器和旁路寄存器。

(1) 邊界掃描寄存器構(gòu)成邊界掃描路徑,他的每一個(gè)單元由存儲(chǔ)器、發(fā)送?接收器和緩沖器組成。邊界掃描單元置于集成電路的輸入?輸出端附近,并首尾相連構(gòu)成一個(gè)移位寄存器鏈,首端接TD I,末端接TDO。在測(cè)試時(shí)鐘TCK的作用下,從TD I加入的數(shù)據(jù)可以在移位寄存器鏈中移動(dòng)進(jìn)行掃描。

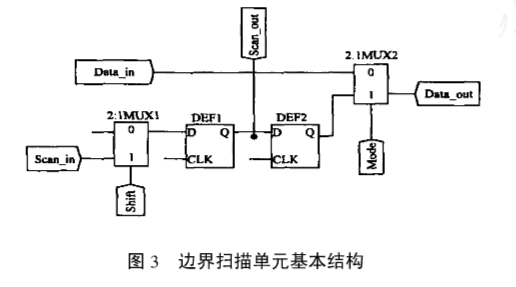

邊界掃描單元(BSC)基本結(jié)構(gòu)如圖3所示。其主要作用是加載測(cè)試向量和捕捉測(cè)試響應(yīng)。MU X2由M ode信號(hào)控制,M ode信號(hào)為0時(shí),可以使單元的數(shù)據(jù)輸出與數(shù)據(jù)輸入相連;為1時(shí),數(shù)據(jù)輸出端的數(shù)據(jù)是DFF2的輸出信號(hào),與數(shù)據(jù)輸入端的信號(hào)無(wú)關(guān)。Shift信號(hào)控制MU X1,為0時(shí),DFF1采樣數(shù)據(jù)輸入端的信號(hào);為1時(shí),進(jìn)行移位。BSC的工作按照以下4個(gè)步驟進(jìn)行:MU X1在Shift DR模式,移入新的測(cè)試向量;MU X2在U pdate DR模式,加載測(cè)試向量到單元的數(shù)據(jù)輸出端;MU X1在Cap ture DR模式,捕捉單元并行輸入端的響應(yīng);MU X1在Shift DR模式,移出響應(yīng)。

(2) 器件識(shí)別寄存器(ID)有32位,其中31~28位是版本號(hào),27~12位是器件序列號(hào),11~1位是廠(chǎng)家標(biāo)識(shí),第0位為1。借助他可以辨別板上元器件的生產(chǎn)商,還可以通過(guò)他來(lái)測(cè)試是否將正確的器件安裝在PCB板的正確位置。器件標(biāo)識(shí)寄存器和邊界掃描寄存器可以使用相同的邊界掃描單元。

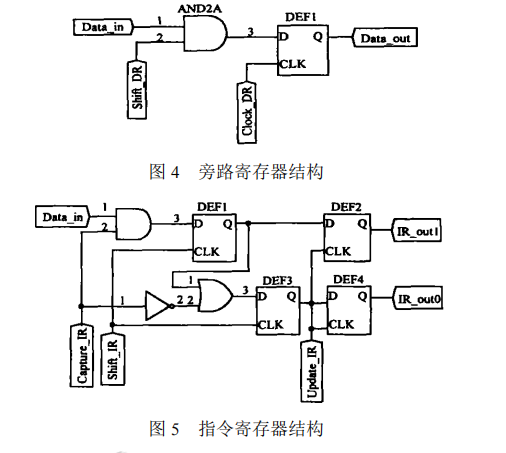

(3) 旁路寄存器(BR)只有1位,他提供了一條從TD I到TDO之間的最短通道,用來(lái)將不參加串行掃描的數(shù)據(jù)寄存器的數(shù)據(jù)旁路掉,以減少不必要的掃描時(shí)間。旁路寄存器的結(jié)構(gòu)如圖4所示。在Shift DR模式下,數(shù)據(jù)直接從Data in到Data out,而不經(jīng)過(guò)任何邊界掃描寄存器。

指令寄存器

指令寄存器由串移位級(jí)和并行鎖存級(jí)組成,進(jìn)行指令的譯碼,兩位指令的指令寄存器的結(jié)構(gòu)如圖5所示。其位數(shù)由所選指令數(shù)決定,常用指令很多。DFF1和DFF2在Cap ture IR和Shift IR的控制下,進(jìn)行兩位指令譯碼,在U pdate IR模式下指令數(shù)據(jù)加載到指令輸出端,高位在IR out1,低位在IR out2。IEEE114911標(biāo)準(zhǔn)中定義了大量指令,有必須的,有可選的,而且也允許定義更多特定設(shè)計(jì)的指令來(lái)擴(kuò)展測(cè)試邏輯的功能。

此外,除了上述數(shù)據(jù)寄存器以外,還可以包括用戶(hù)定義的數(shù)據(jù)寄存器。

邊界掃描測(cè)試方式

利用邊界掃描技術(shù),可以對(duì)集成電路芯片的內(nèi)部故障、電路板的互連以及相互間影響有比較全面的了解,并通過(guò)加載相應(yīng)指令到指令寄存器來(lái)選擇工作方式。不同的測(cè)試在不同的工作方式下進(jìn)行。

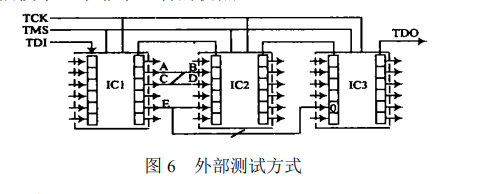

外測(cè)試(EXTEST)

外測(cè)試測(cè)試IC與電路板上其他器件的連接關(guān)系。此時(shí)邊界掃描寄存器把IC的內(nèi)部邏輯與被測(cè)板上其他元件隔離開(kāi)來(lái)。在EXTEST指令下,給每個(gè)I?O端賦一個(gè)已知的值用于測(cè)試電路板上各集成電路芯片間連線(xiàn)以及板級(jí)互連的故障,包括斷路故障和短路故障。圖6中的3塊芯片受相同的TCK和TM S總線(xiàn)控制,各芯片TDO的輸出端連接到下一器件TD I的輸入端,構(gòu)成了一條移位寄存器鏈。測(cè)試向量從IC1的TD I輸入,通過(guò)邊界掃描路徑加到每個(gè)芯片的輸出引腳寄存器,而輸入引腳寄存器則接收響應(yīng)向量。圖中IC2的B腳接收IC1的A腳寄存器的信號(hào),正常情況下,B腳的值應(yīng)該為1。但如果AB和CD線(xiàn)間出現(xiàn)了短路,則B腳寄存器接收到的值變成了0。IC3的F引腳寄存器接收IC1的E腳寄存器信號(hào),正常情況下,F(xiàn)腳的值應(yīng)該為1,但如果引線(xiàn)EF間出現(xiàn)了斷路,則從F腳得到的值不是1,而是0。

在電路板的測(cè)試中出現(xiàn)最頻繁的是斷路和短路故障,傳統(tǒng)的逐點(diǎn)檢查的方法既麻煩又費(fèi)時(shí),而通過(guò)邊界掃描技術(shù)的外部測(cè)試方式,把從TDO端輸出的邊界掃描寄存器的串行信號(hào)與正確的信號(hào)相比較,就可以方便有效地診斷出電路板引線(xiàn)及芯片引腳間的斷路和短路故障。這是邊界掃描技術(shù)一個(gè)非常顯著的優(yōu)點(diǎn)。

內(nèi)測(cè)試 ( IN TEST )

內(nèi)測(cè)試測(cè)試IC本身的邏輯功能,即測(cè)試電路板上集成電路芯片的內(nèi)部故障。測(cè)試向量通過(guò)TD I輸入,并通過(guò)邊界掃描通道將測(cè)試向量加到每個(gè)芯片的輸入引腳寄存器中,從輸出端TDO可以串行讀出存于輸出引腳寄存器中各芯片的響應(yīng)結(jié)果。根據(jù)輸入向量和輸出響應(yīng),就可以對(duì)電路板上各芯片的內(nèi)部工作狀態(tài)做出測(cè)試分析。

采樣測(cè)試方式 (SAM PL E?PRELOAD )

采樣測(cè)試方式常用于對(duì)一個(gè)正在運(yùn)行的系統(tǒng)進(jìn)行實(shí)時(shí)監(jiān)控。取樣?預(yù)置(SAM PL E?PRELOAD),在捕捉階段從輸入端取樣,在更新階段預(yù)置BSC,為外測(cè)試做準(zhǔn)備;移出器件標(biāo)識(shí)(ID Code):選擇旁路寄存器,使數(shù)據(jù)在A SIC間快速移位。此外還有多種測(cè)試指令,他們的存在和不斷擴(kuò)充,使邊界掃描技術(shù)的應(yīng)用得以拓展和延伸,進(jìn)行更有效的集成電路測(cè)試。

邊界掃描技術(shù)是一種新的測(cè)試技術(shù),雖然他能夠測(cè)試集成電路芯片的輸入?輸出管腳的狀態(tài),也能測(cè)試芯片內(nèi)部工作情況以及引線(xiàn)級(jí)的斷路和短路故障,但是邊界掃描技術(shù)還處于不斷發(fā)展之中。他的應(yīng)用是建立在具有邊界掃描電路設(shè)計(jì)的集成電路芯片基礎(chǔ)上的。對(duì)于電路板上安裝的不帶邊界掃描電路的器件的測(cè)試,邊界掃描是無(wú)能為力的。今后也不可能將所有的數(shù)字集成電路芯片設(shè)計(jì)上邊界掃描電路,因此他也不可能完全代替其他的測(cè)試方法。這種方法的突出優(yōu)點(diǎn)是具有測(cè)試性,可以只通過(guò)運(yùn)行計(jì)算機(jī)程序就能檢查出電路或連線(xiàn)的故障,這在可靠性要求高、排除故障要求時(shí)間短的場(chǎng)合非常適用。特別是在武器裝備的系統(tǒng)內(nèi)置測(cè)試和維護(hù)測(cè)試中具有很好的應(yīng)用前景。

-

測(cè)試技術(shù)

+關(guān)注

關(guān)注

0文章

114瀏覽量

21052 -

邊界掃描

+關(guān)注

關(guān)注

1文章

32瀏覽量

15022

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

miniled 技術(shù)原理解析 miniled與 OLED 比較

場(chǎng)發(fā)射掃描電鏡(FESEM)與常規(guī)掃描電鏡(SEM):技術(shù)對(duì)比及優(yōu)勢(shì)分析

蔡司掃描儀GOM精準(zhǔn)與高效的掃描技術(shù)

LMX2572EVM在測(cè)試評(píng)估版時(shí),不同頻率下整數(shù)邊界雜散差別很大是為什么?

第五代CAPSENSE? MSC使用多頻掃描應(yīng)對(duì)CS測(cè)試

掃描速率和濃度對(duì)循環(huán)伏安圖有什么影響

漏洞掃描一般采用的技術(shù)是什么

【9月3日|線(xiàn)上講堂】從衛(wèi)星通信技術(shù)到測(cè)試方案全景解析

在Traveo T2G CYT2B73BADQ0AZSGS上運(yùn)行JTAG邊界掃描,為什么無(wú)法從設(shè)備的JTAG端口獲得任何響應(yīng)?

深入解析與無(wú)線(xiàn)通信RFIC設(shè)計(jì)與測(cè)試實(shí)用指南

HDJB-1200六相微機(jī)繼電保護(hù)測(cè)試儀阻抗特性試驗(yàn)方法

邊界掃描測(cè)試技術(shù)的原理解析

邊界掃描測(cè)試技術(shù)的原理解析

評(píng)論