大俠好,歡迎來到FPGA技術江湖,江湖偌大,相見即是緣分。大俠可以關注FPGA技術江湖,在“闖蕩江湖”、"行俠仗義"欄里獲取其他感興趣的資源,或者一起煮酒言歡。

今天給大俠帶來基于FPGA實時時鐘的設計,附源碼,獲取源碼,請在“FPGA技術江湖”公眾號內回復“基于FPGA實時時鐘的設計源碼”,可獲取源碼文件。話不多說,上貨。

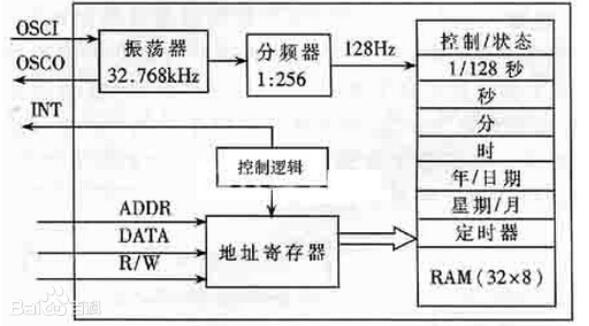

本次設計采用了美國DALLAS公司推出的一種高性能、低功耗、帶RAM的實時時鐘電路 DS1302,它可以對年、月、日、周、時、分、秒進行計時,具有閏年補償功能,工作電壓為2.5V~5.5V。采用三線接口與CPU進行同步通信,并可采用突發方式一次傳送多個字節的時鐘信號或RAM數據。DS1302內部有一個31×8的用于臨時性存放數據的RAM寄存器。

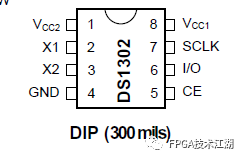

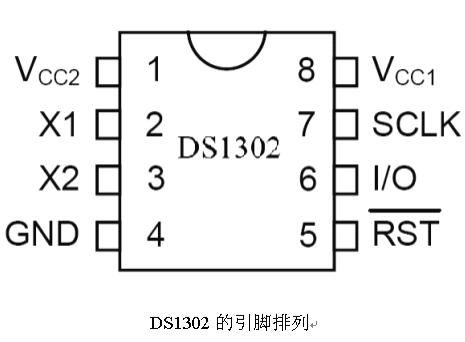

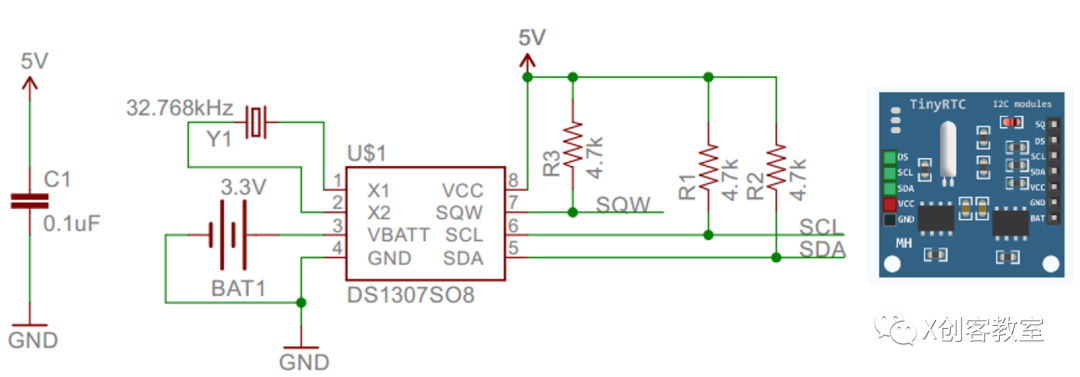

DS1302芯片的封裝如下:

DS1302芯片有8個引腳,在本次的設計中只要驅動3個引腳就可以了,其他的引腳都是和硬件相連接的,和FPGA連接的有時鐘sclk,串行數據數據接口IO,以及CE。

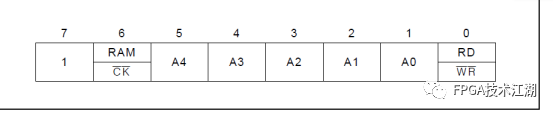

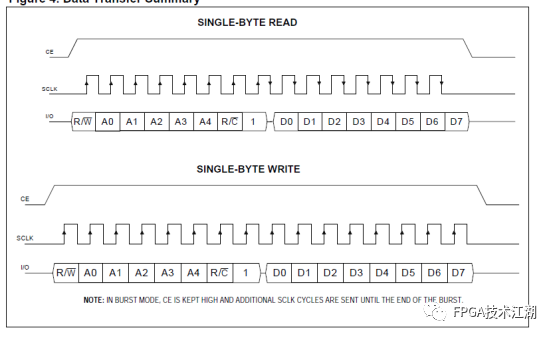

其工作原理就是在數據的傳送過程中先把CE拉高,在每個數據的上升沿寫入數據,在下降沿輸入數據,一次只能讀寫一位數據。最初我們通過一個8位的控制指令來選擇讀寫,如果控制指令是單字節模式,連續的8個脈沖上升沿寫入,下降沿讀出數據,一次只能讀取一個字節,如果是突發模式通過連續的脈沖一次性的寫完7個字節的時間寄存器也可以一次性的讀完8--328位的ram數據

控制指令有8位,第七位必須為高,如果是0寫入被禁止,第六位0是對時鐘寄存器的讀寫操作,為1對是控制對RAM區的讀寫操作。

bit1 -- 5 是對相關寄存器的操作,bit0是讀寫操作。

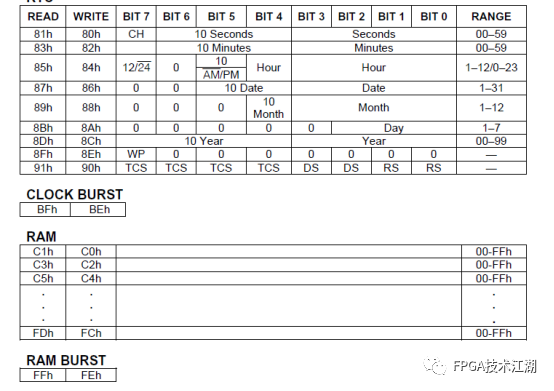

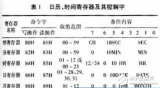

各個寄存器的的設置,和每位的表示如下圖,從圖中我們了解到讀寫時控制字是多少以及寫入寄存器的地址,和寫入的8位的時間表示。我們可以通過下表來設置一個初始的時間。

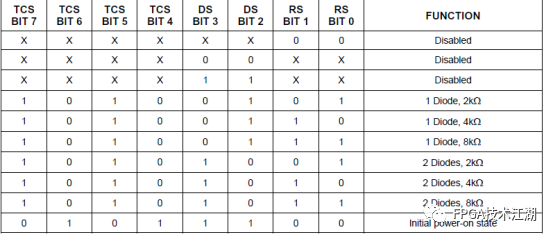

涓流寄存器主要決定了DS1302的充電特性,涓流充電選擇位4--7位,1010涓流充電其他禁止充電,二級管選擇位3--2位,電阻選擇1--0位具體的選擇如下表。

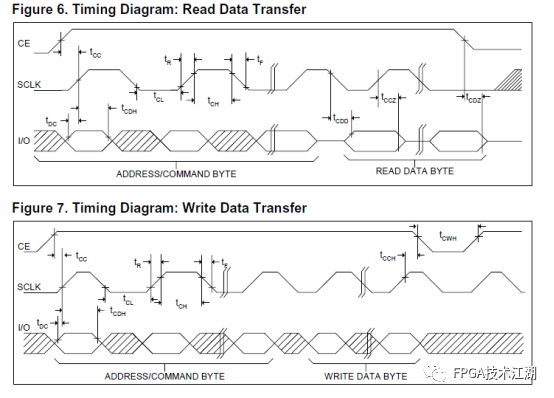

突發模式下,表示我們可以連續寫,連讀,連續寫時必須寫滿7個時鐘寄存器。時序圖如下,SPI通信。

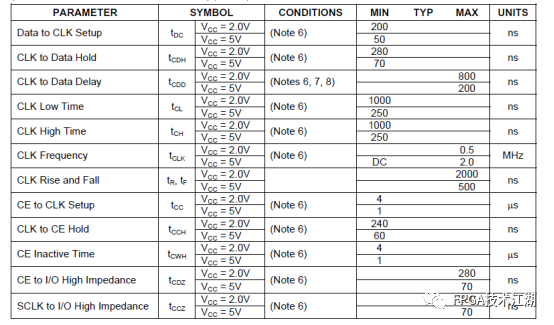

下表表示數據傳送過程中數據的延遲,時鐘的周期等時間。

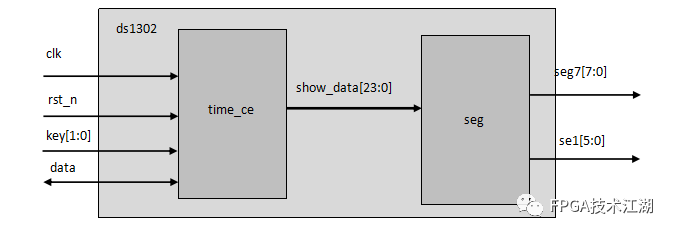

本次設計是通過配置DS1302芯片來實現實時時鐘的監測,通過控制2個按鍵來選擇我們要在數碼管上顯示的時間,按下按鍵1來顯示周幾,按下按鍵2來顯示年月日,不按顯示時分秒,這樣顯示符合實時鐘的顯示。思路是先打開寫保護,一個一個寄存器的寫進去,然后關閉寫保護,然后再讀出數據。 設計架構圖:

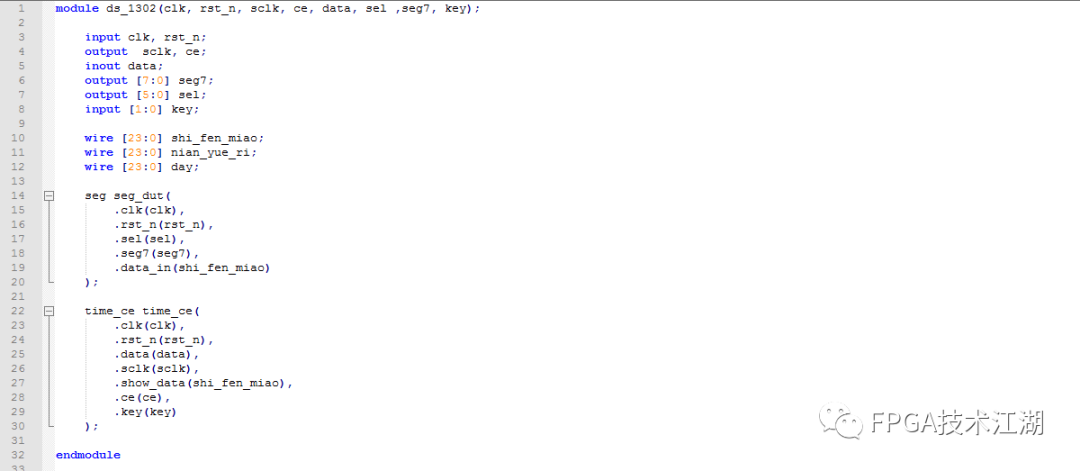

設計代碼:(源碼文件可從公眾號內部獲取) 總模塊:

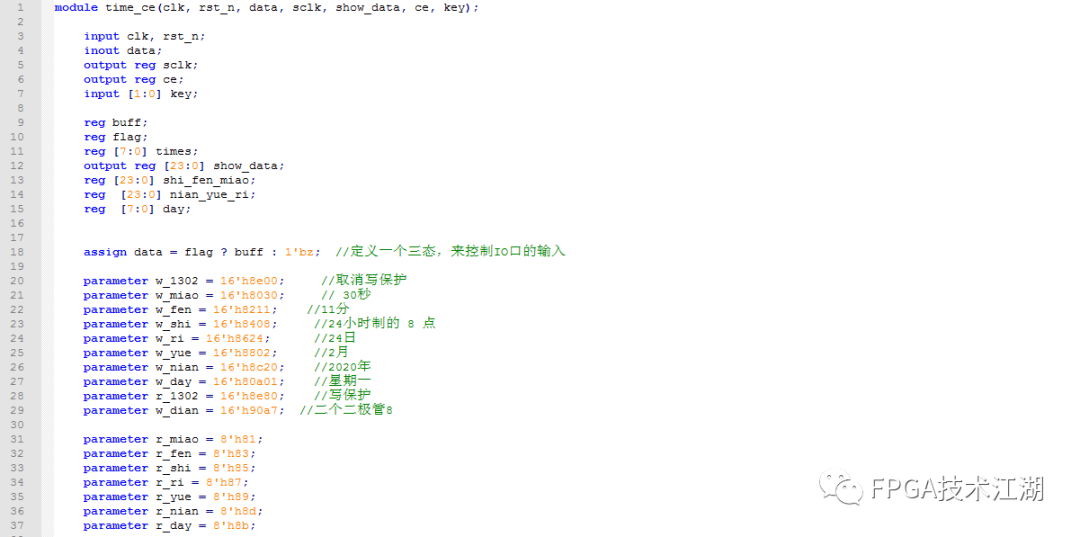

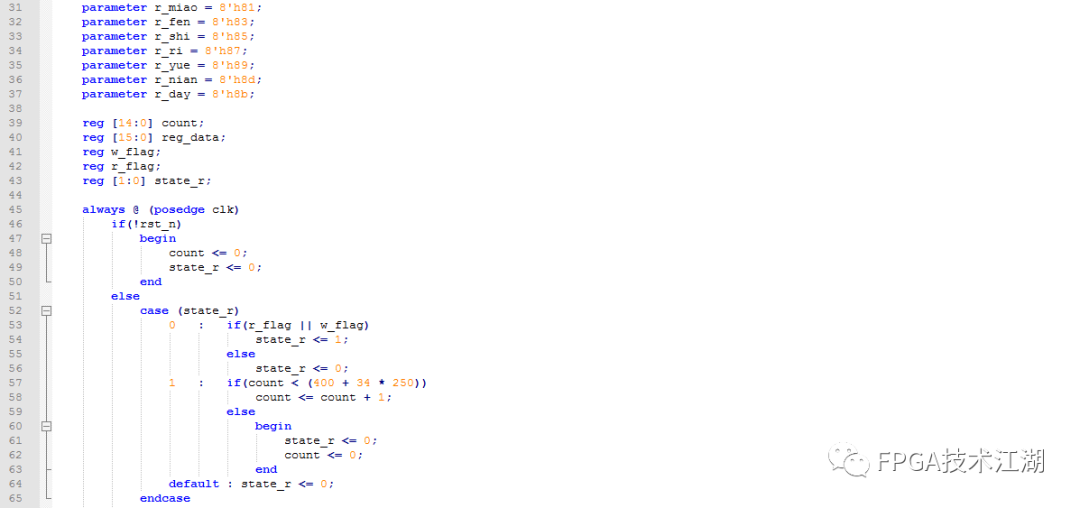

控制模塊:(由于控制模塊代碼較多,只展示部分關鍵信號,具體代碼如有需要,請公眾號內自行獲取)

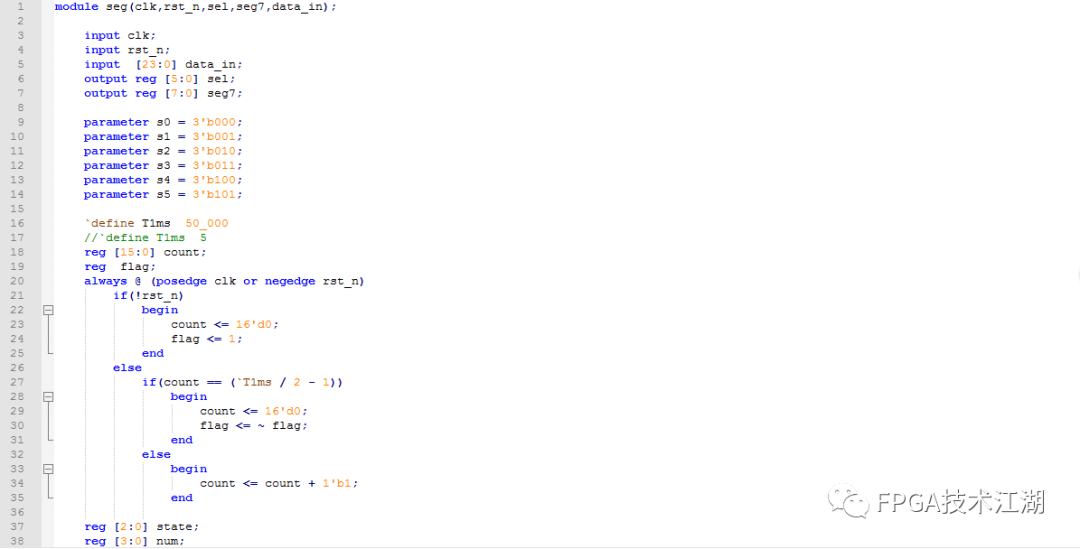

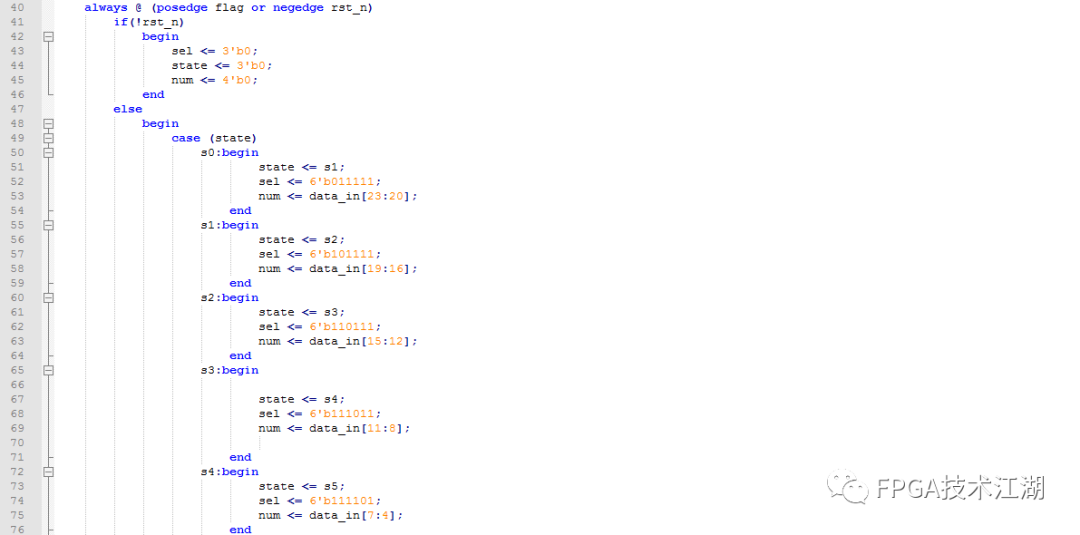

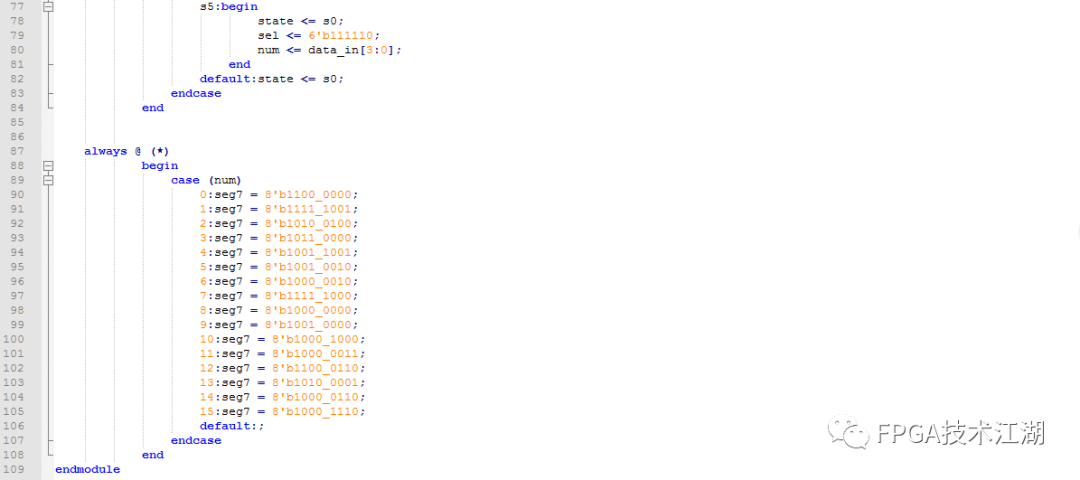

數碼管模塊:

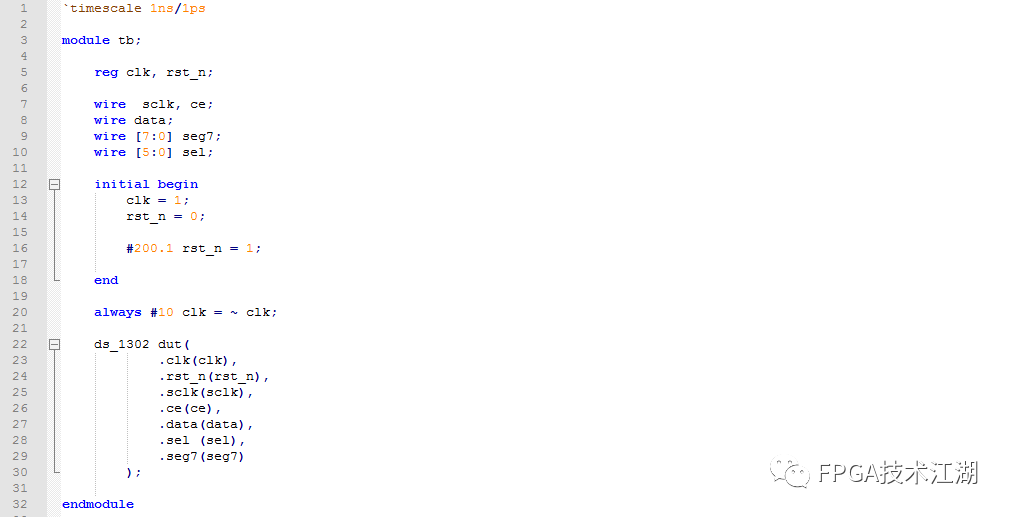

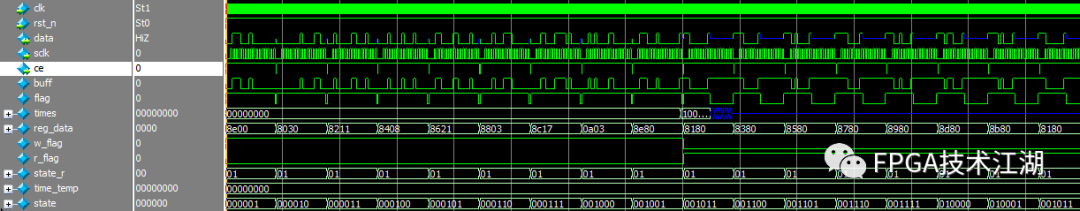

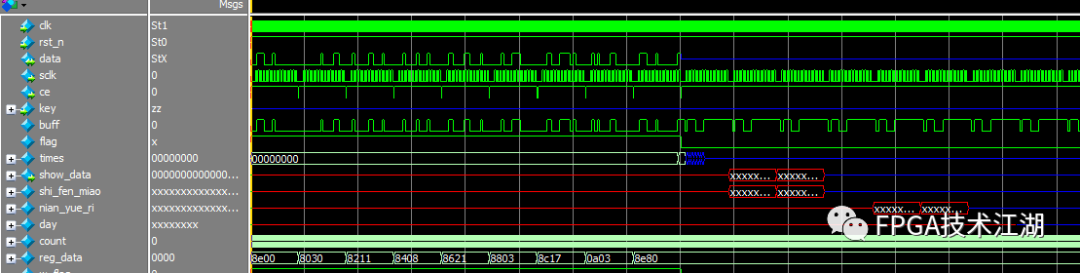

仿真圖:

從仿真測試圖中,可以清楚的看到在發送的寄存器命令時,收回總線控制權,讀數據時,釋放了總線控制權。 下圖是突發讀的時序圖,此次設計是一個一個的寫寄存器,必須寫滿7個時鐘寄存器,然后突發的讀,突發讀的時候拉高CE,然后不停的讀接收數據。拓展也可以做突發讀寫,原理一樣,感興趣的可以試一試。

-

FPGA

+關注

關注

1629文章

21753瀏覽量

604183 -

寄存器

+關注

關注

31文章

5357瀏覽量

120615 -

實時時鐘

+關注

關注

4文章

246瀏覽量

65828 -

時鐘電路

+關注

關注

10文章

237瀏覽量

50753

原文標題:源碼系列:基于FPGA實時時鐘的設計(附源工程)

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

實時時鐘是什么

實時時鐘模DS1302程序列子

實時時鐘芯片有哪些_實時時鐘芯片選型介紹

實時時鐘芯片應用

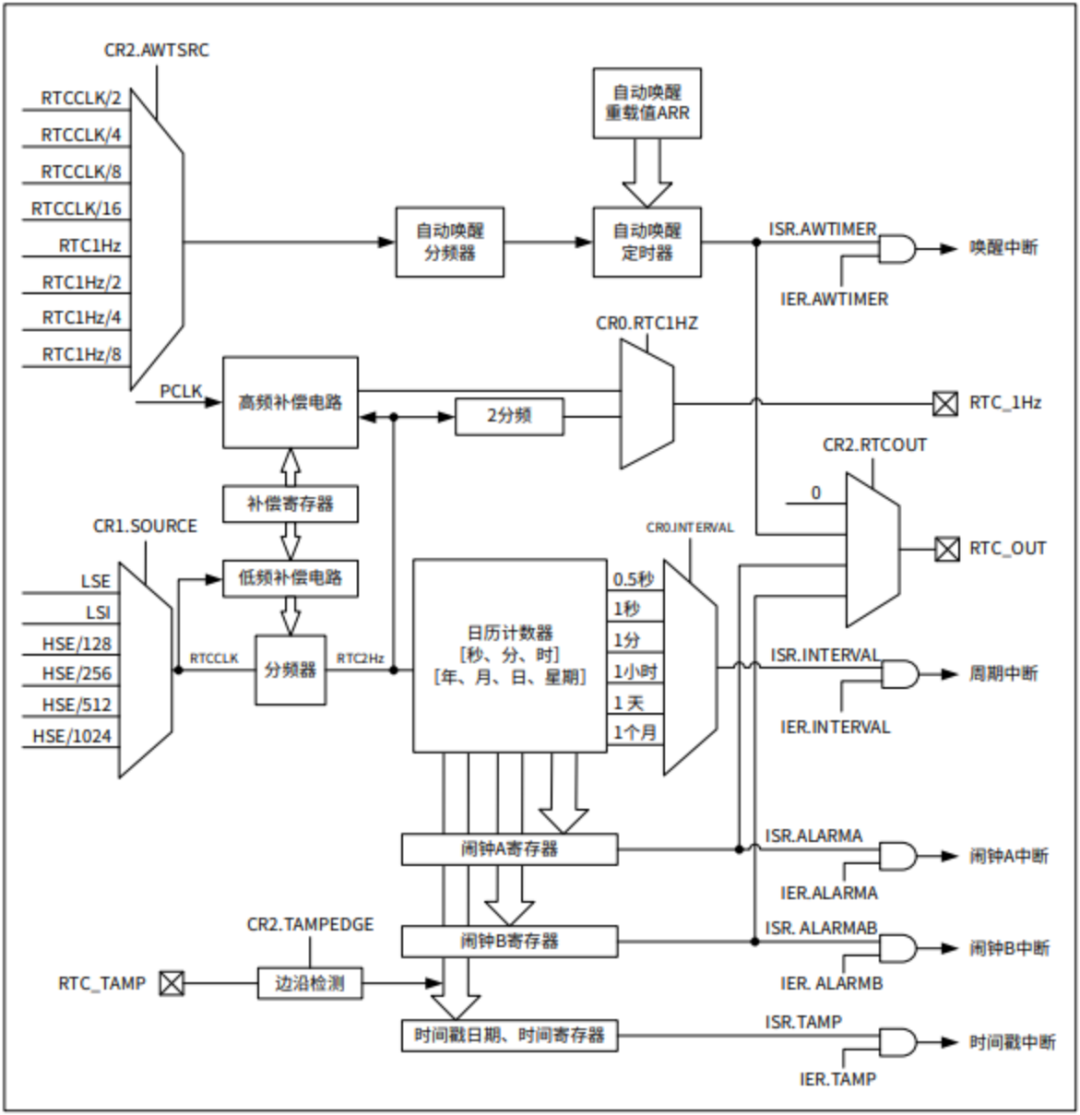

淺談RTC實時時鐘特征與原理

【實時時鐘RTC】MSP430系統實時時鐘RTC學習日志(完善中)

基于FPGA的實時時鐘設計

基于FPGA的實時時鐘設計

評論