STMicroelectronics成像部門負責向消費者、工業、安全和汽車市場提供創新的成像技術和產品。該團隊精心制定了一套通過模板實現的High-Level Synthesis(HLS)高層次綜合流程,使得上述產品能夠迅速上市。對于汽車市場,該流程符合ISO 26262標準,因此能確保可靠性。

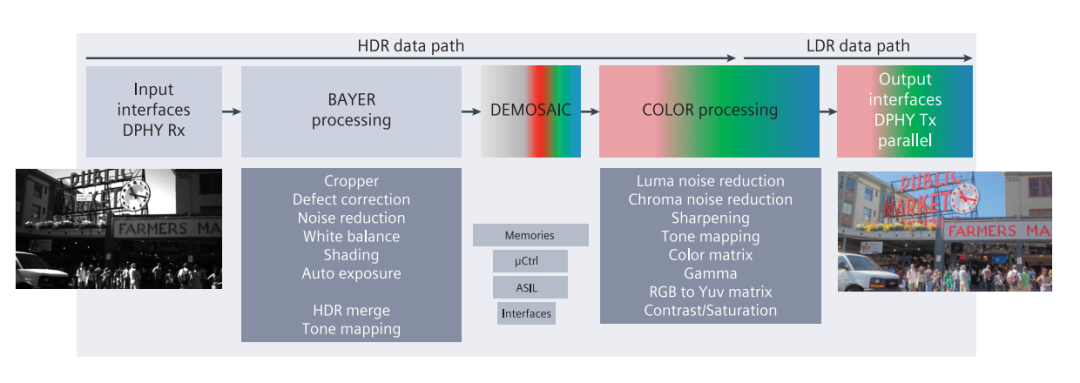

ISP是處理圖像傳感器數據的硬件和軟件組合。ISP可能非常復雜,因此該團隊使用了可復用的IP模塊來組裝設計。圖1顯示了一個示例ISP方框圖。

圖1中的ISP顯示了主要ISP功能,并沿著數據通路說明了各自所需的諸多處理算法。

圖1.用于汽車應用的復雜高質量ISP

了解HLS工具歷史

成像部門于2007年開始對多媒體IP(編碼器、解碼器、顯示器和ISP功能)運用HLS設計流程,最初使用的是西門子數字化工業軟件競爭對手提供的工具。當該工具在2015年停止服務后,該團隊對不同供應商提供的各種HLS工具進行了評估。他們將若干ISP設計用作測試案例,然后監測其所生成的RTL的面積和功耗結果。在此評估基礎上,Catapult High-Level Synthesis平臺因為表現優異而被該團隊選中。

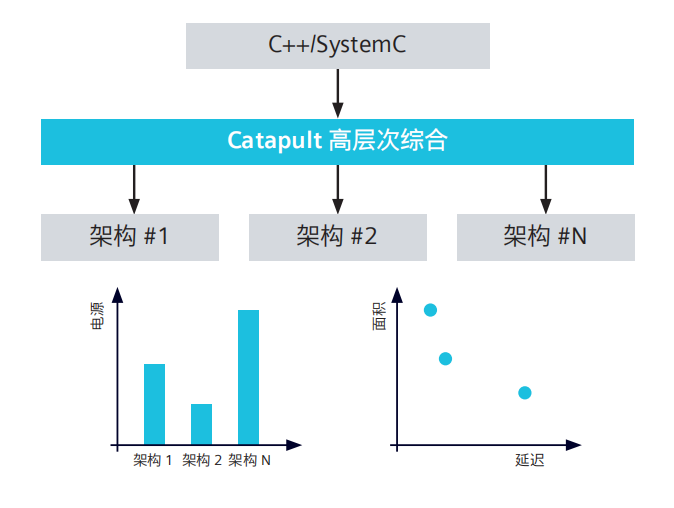

借助Catapult HLS平臺,設計人員便能利用行業標準ANSI C++和SystemC來描述功能意圖,并將其提高到生產率更高的抽象層次。根據這些高層次的描述,Catapult即可生成產品級的RTL。通過加快RTL生成時間以及自動生成無錯誤的RTL,Catapult可顯著縮短RTL驗證所需的時間。Catapult的功耗優化功能可自動大幅降低動態功耗。高度交互的工作流程可提供對綜合過程的完全可見性和控制,使設計人員能夠在功耗、性能和面積等方面迅速收斂到理想實現方案(圖2)。

圖2.快速探索架構以求得理想功耗和面積

創建成像IP模板

該團隊意識到,ISP是一系列的級聯濾波器,這些濾波器具有相似的結構和接口。他們的想法是利用C++模板開發一個參數化濾波器庫,然后將其復用于每個ISP設計中。這種方法具有如下優勢:

◎ 設計效率:復用經過驗證的模板可以更快地構建ISP

◎ 更新:能夠輕松將更新應用到每個IP模塊,而且可以在一天內將算法更改整合完畢

◎ 集中精力:設計人員可以將時間花在增量算法開發上,而不必在通用結構上耗費心力

◎ 資源:團隊可以為項目開發更多的IP模塊,且無需增加額外的員工

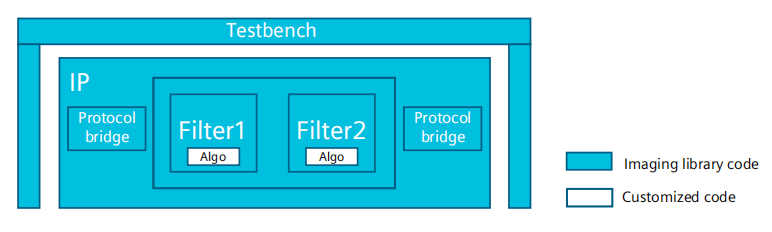

每個參數化模板都是一個C++類(圖3),其可實現如下方面功能:

◎ 內存管理

◎ 協議橋

◎ 像素管理內核

◎ 連接到驗證平臺

圖3.設計人員可專注于算法,而不是基礎架構

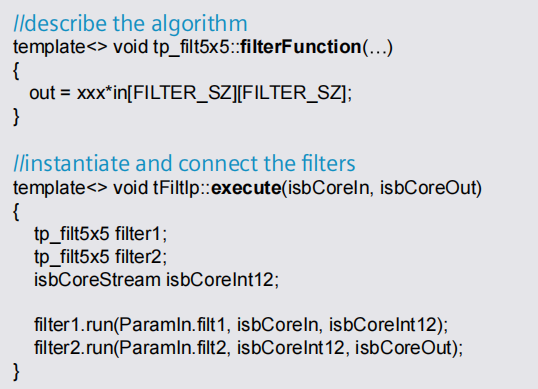

設計人員可覆寫filterFunction以提供算法代碼,然后再通過覆寫execute函數將其連接到濾波器。

利用這一模板流程,該團隊在過去兩年間創建了50多個設計,規模從1萬個邏輯門到200萬個邏輯門不等。

驗 證 設 計

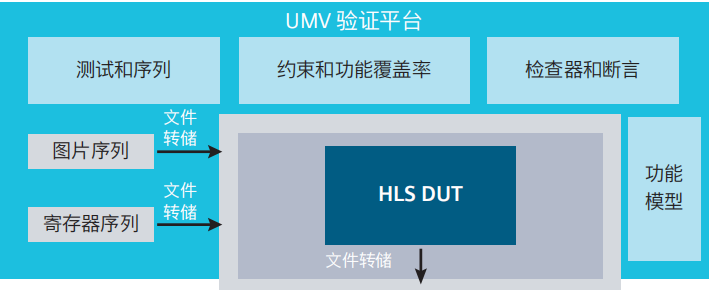

該團隊使用UVM驗證平臺來指定提供偽隨機驗證及收集代碼和功能覆蓋率指標的序列。該團隊使用了相同的驗證平臺(無需任何修改)來驗證C++和生成的RTL設計。每個驗證平臺(圖4)會為每個項目建立相同的標準集,這樣一來,便可通過自動設置驗證環境來縮短開發時間。此標準集包括:

◎ 標準化數據的輸入和輸出接口

◎ 標準化寄存器配置接口

◎ 標準化高層次控制(啟用和重置設計)

◎ 標準化輸入和輸出數據格式

圖4.常見UVM驗證平臺仿真C++(圖中所示)

或RTL被測設計

UVM驗證平臺的常見元素包括操作被測設計(DUT)的測試和序列、約束和功能覆蓋率語句,以及多種檢查器和斷言。圖片和寄存器序列可操作DUT輸入。該團隊使用功能模型對DUT進行按位比較。

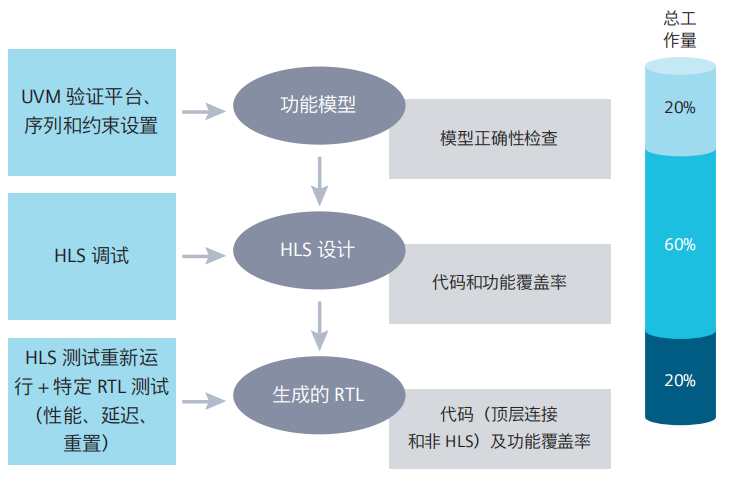

該團隊對每個項目使用了相同的驗證方法,因此可以確保獲得尚佳質量的設計(圖5)。

圖5.驗證流程

HLS驗證流程的高層次步驟包括:

◎ 設計人員創建一個功能模型,驗證人員利用必要 的序列和約束建立UVM驗證平臺。此階段的仿真能夠提供對整體環境的“正確性”檢查,因此可能會發現問題。

◎ 在一個項目中,HLS調試步驟消耗的時間最多。此時,需要運行相關序列來調試問題以及收集代碼和功能覆蓋率指標。

◎ 藉由使用相同的UVM驗證平臺,團隊可以對 Catapult HLS生成的RTL進行仿真。此時,團隊 會針對C++設計中未建模的功能,例如輸入和輸出之間的延遲以及重置行為,添加一些特定RTL測試。在此步驟中,團隊還會仿真HLS流程中未生成的任何RTL(如有)。此時,團隊會從設計的頂層收集代碼和功能覆蓋率指標。

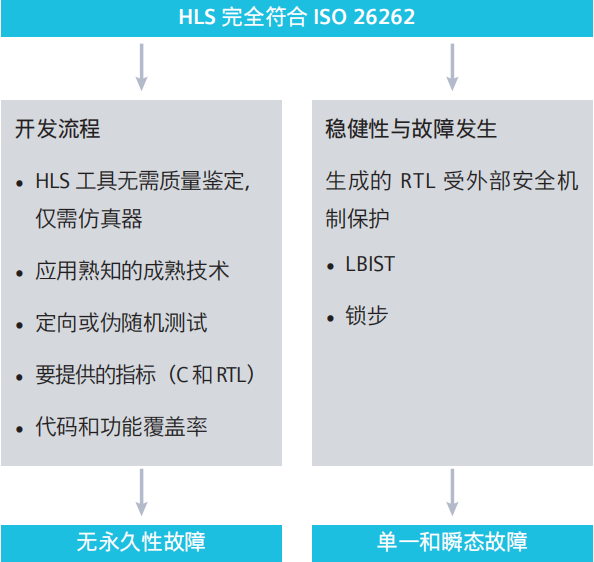

符合ISO 26262標準

許多ISP產品的目標市場均為汽車市場,這意味著團隊必須遵循ISO 26262標準。ISO 26262是一項針對重量在3500公斤及以下的公路車輛中的電氣和電子元器件功能安全的標準。團隊需要確保HLS流程和設計穩健性符合標準(圖6)。

圖6.HLS流程符合ISO 26262

該標準的其中一個關鍵要求是要確保器件沒有永久性故障(設計錯誤)。也就是說,團隊必須確保開發流程是“安全的”。要滿足這一標準,則必須應用成熟的技術,執行一系列測試,并收集衡量指標報告。團隊沒有對Catapult HLS平臺進行 ISO 26262質量鑒定。相反,他們對運行測試的仿真器進行了鑒定。雖然團隊不要求在其流程中對Catapult HLS平臺進行質量鑒定,但實際上Siemens Safe計劃會提供該工具的ISO 26262質量鑒定和相關文檔。

另一個主要要求是要確保設計能夠處理單個或瞬態故障,并能從中予以恢復。團隊在ISP外圍使用邏輯BIST和Lockstep(鎖步)等外部安全機制來確保其穩健性。

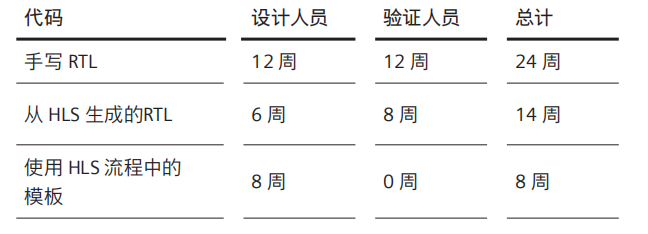

從HLS流程獲益

采用基于模板的HLS流程的主要優勢在于,其可大幅減少開發時間和成本,而又不會影響結果和設計質量(表1)。使用該流程,團隊創建設計的速度比手工編碼快了3倍左右,單個設計人員便可執行驗證,通常不需要單獨的驗證人員資源。

表1. 一名設計人員和一名驗證人員

花在ISP設計項目上的平均時間

開發成本也將進一步降低,原因如下:

◎ 使用C++進行驗證,以收集關鍵覆蓋率指標,這意味著團隊可以在幾分鐘內運行數以千計的測試,而不像RTL那樣需要幾個小時

◎ 與RTL相比,C++代碼的行數顯著減少,這意味著維護成本將會大幅降低

◎ 可以輕松適應設計流程后期的規范變化,而不會影響設計進度

◎ 短短幾天時間便可完成對10名設計人員的HLS流程培訓,這意味著團隊可以快速提高生產率

此外,Catapult HLS平臺具有自動化設計實現的功能,因此可以進一步降低HLS流程的開發時間和成本:

◎ 自動流水線:通過指令的簡單改變提高流水線級 數,而C++代碼將保持不變。如果是手動流水線,則需要大量的重新編碼和調試工作

◎ 自動硬件共享:例如,要在一個流水線的不同狀態下重復使用一個乘法器來處理同一迭代的幾個操作,若通過手動實現將非常困難

◎ 自動功能時鐘門控:相比手動編碼可節省大量時間,并能自動降低功耗10%

◎ 該團隊發現,使用該工具生成的RTL結果的質量非常出色,尤其是針對復雜設計時。

如需了解有關Catapult HLS解決方案的更多信息,請點擊此處。

-

傳感器

+關注

關注

2552文章

51227瀏覽量

754648 -

西門子

+關注

關注

94文章

3051瀏覽量

116053 -

圖像信號

+關注

關注

0文章

26瀏覽量

14157 -

HLS

+關注

關注

1文章

130瀏覽量

24144

原文標題:客戶故事|使用HLS流程設計和驗證圖像信號處理設備,加快產品上市

文章出處:【微信號:Mentor明導,微信公眾號:西門子EDA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

基于FPGA的混合信號驗證流程

新手求助,HLS實現opencv算法加速的IP在vivado的使用

【正點原子FPGA連載】第一章HLS簡介-領航者ZYNQ之HLS 開發指南

【正點原子FPGA連載】第六章OV5640攝像頭灰度顯示實驗-領航者ZYNQ之HLS 開發指南

【正點原子FPGA連載】第十三章基于xfOpenCV的中值濾波實驗-領航者ZYNQ之HLS 開發指南

Vivado HLS實現OpenCV圖像處理的設計流程與分析

嵌入式硬件開發學習教程——Xilinx Vivado HLS案例 (流程說明)

關于ZYNQ HLS圖像處理加速總結的分享

HLS/HLV 流程說明及優勢

基于Vitis HLS的加速圖像處理

使用HLS流程設計和驗證圖像信號處理設備

使用HLS流程設計和驗證圖像信號處理設備

評論