來源:John Boyd IEEE電氣電子工程師學會

9月,佳能交付了一種技術的首個商業版本,該技術有朝一日可能顛覆最先進硅芯片的制造方式。這種技術被稱為納米壓印光刻技術(NIL,nanoimprint lithography),它能夠繪制出小至14納米的電路特征——使邏輯芯片達到與英特爾、超微半導體(AMD)和英偉達現正大量生產的處理器相當的水平。

納米壓印光刻系統具有的優勢可能對當今主導先進芯片制造、價值1.5億美元的極紫外(EUV,https://spectrum.ieee.org/tag/euv)光刻掃描儀構成挑戰。如果佳能的說法正確,其設備最終將以極低的成本生產出具有EUV品質的芯片。

該公司的方法與極紫外光刻系統完全不同,極紫外光刻系統由總部位于荷蘭的阿斯麥(ASML)獨家生產。這家荷蘭公司采用一種復雜的工藝:首先用千瓦級的激光將熔化的錫滴擊打成等離子體,等離子體會發出13.5納米波長的光(https://spectrum.ieee.org/high-na-euv)。然后,通過特殊的光學器件將這種光導入真空室,并從有圖案的掩模反射到硅片上,從而將圖案固定到硅片上。

相比之下,佳能交付給美國國防部支持的研發聯盟——Texas Institute for Electronics的系統看起來簡單得近乎滑稽。簡而言之,它是將電路圖案壓印到硅片上。

納米壓印光刻技術:更小、更廉價

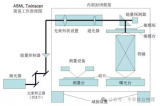

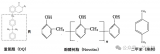

納米壓印光刻(NIL)起始于一個類似光刻的工藝。它使用聚焦電子束在一個“掩模”上繪制圖案。在極紫外光刻(EUV)中,這個圖案被捕捉在一個反射鏡上,然后被反射到硅片上。但在納米壓印光刻技術中,會使用一個由石英制成的所謂母版掩模(或模具)來制造多個同樣由石英制成的復制掩模。

然后,將復制掩模直接按壓到已涂覆一種被稱為光刻膠的液態樹脂的晶圓表面,就像蓋章一樣。接著,使用汞燈(20世紀70年代芯片制造中使用的那種)發出的紫外線來固化樹脂,以便將掩模從晶圓上移除。這樣,母版掩模上的相同圖案就被壓印到硅片上的光刻膠上了。就像基于光刻技術的芯片制造一樣,該圖案引導著制造晶體管和互連線所需的一系列蝕刻、沉積和其他工藝。

“這似乎是一種推進無光源納米光刻技術的簡單而巧妙的方法,能夠實現高精度的圖案化,”印第安納州普渡大學極端環境材料中心主任、極紫外(EUV)光源專家Ahmed Hassanein說道,“該系統還具有功耗更低的優勢,與EUV系統相比,其購買和運行成本應該更低。”

佳能聲稱,與極紫外光刻(EUV)相比,這種直接接觸的方法需要的步驟和工具更少,從而使得操作流程更簡單、成本更低。例如,與采用250瓦光源的極紫外光刻系統相比,佳能估計納米壓印光刻(NIL)僅消耗十分之一的能量。

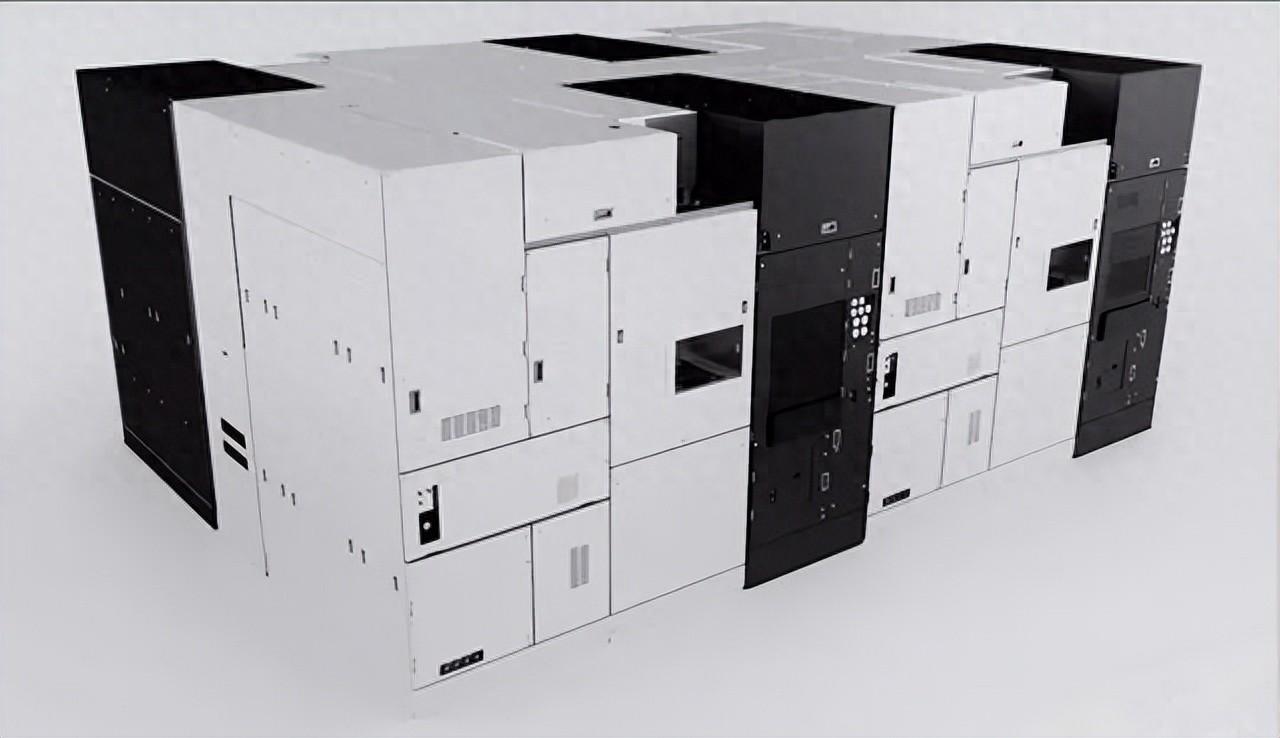

此外,納米壓印光刻技術在晶圓廠潔凈室占地面積更小,而潔凈室的空間極其寶貴。如今的極紫外光刻系統和雙層巴士一樣大——約200立方米。但是一組四個納米壓印光刻系統所占空間還不到其一半(長6.6米、寬4.6米、高2.8米)——不過還需要一個占地50立方米的掩模復制工具。

納米壓印光刻(NIL)走向商業化耗時20年

但這種簡單性是經過漫長、耗資巨大的研發過程才實現的。二十多年前,當佳能于2004年開始研發納米壓印光刻技術時,已有幾家研究實驗室在進行相關技術的研發了(https://spectrum.ieee.org/nanotransistors-stamped-out)。2014年,為了加快研發進程,佳能收購了位于得克薩斯州奧斯汀的分子壓印公司(MII),這是該技術早期的領先企業。這家子公司更名為佳能納米技術公司,現在是佳能在美國的納米壓印光刻技術研發中心。

然而,即便將分子壓印公司納入佳能的研發資源庫,將這項技術推向市場仍然花了20年時間。在此期間,佳能必須跨越幾個重大的工程難題,佳能光學產品業務副首席執行官Kazunori Iwamoto在位于東京以北100公里的宇都宮的納米壓印光刻生產基地如此告訴了IEEE Spectrum雜志。

在大多數芯片制造過程中,光刻膠(一種承載電路圖案的聚合物樹脂)均勻地涂覆在晶圓表面。但這對納米壓印光刻(NIL)來說是行不通的,因為在壓印過程中,多余的光刻膠可能會從掩模下方滲出,并干擾下一次壓印操作,從而導致缺陷。因此,佳能利用其噴墨打印技術,以最佳用量涂覆光刻膠以匹配電路圖案。此外,光刻膠的毛細作用力經過優化,使其在接觸時能將材料吸入掩模蝕刻出的圖案中。

佳能還必須防止在壓印過程中晶圓和掩模之間產生氣泡,氣泡會干擾該工具將掩模與晶圓上已有的任何電路特征對齊的能力。解決辦法是設計一種中間更薄的可彎曲掩模。在壓印時,首先對掩模中間施加壓力,這會將掩模中心向外推,使其首先與光刻膠接觸。然后兩個表面之間的接觸繼續沿徑向向外擴展,將空氣驅趕到邊緣并排出。這和你在給智能手機貼屏幕保護膜時避免產生氣泡的做法沒什么不同。

除了通過開發環境控制技術來處理微粒污染問題之外,對準(對齊)問題可能是最棘手的問題。

當多層電路圖案相互疊加壓印時,精確的套刻(疊層)控制對于確保過孔(層間傳輸信號和電力的垂直連接)正確對準至關重要。納米壓印光刻(NIL)工藝允許有一定的調整余地,但在納米級別的操作意味著很容易出現對準誤差。例如,這些誤差可能源于晶圓平整度和表面特征的差異、晶圓和掩模放置的不精確以及壓印過程中掩模形狀的變形。為了將這種扭曲(變形)降到最低,佳能采用了一系列以自動化為主的技術。這些技術包括嚴格控制操作溫度、施加壓電作用力來校正掩模形狀的變形,以及利用激光加熱來使晶圓膨脹或收縮,從而使其與掩模更精準地對準。

“我們將這種專有技術稱為高階失真校正,”Iwamoto說,“通過應用該技術,我們現在能夠以大約1納米的精度套刻(疊層)電路圖案。”

納米壓印光刻(NIL)的分步壓印流程

解決了所有這些問題之后,佳能的工程師們開發出了一種相對簡單直接的光刻工藝。首先要制作一個母版掩模。與其他光刻掩模一樣,它是通過電子束光刻技術蝕刻圖案制成的。母版掩模包含要印刷的電路設計的凸起圖案,其尺寸為152.4毫米×152.4毫米,大約是光刻技術所能生產的最大芯片面積的25倍。

利用這個母版掩模,可以制作多個帶有凹陷圖案的復制掩模。然后,每個復制掩模最多可生產80批產品,每批包含25個晶圓。所以,一個復制掩模可為2000個晶圓制作一層電路。

為了說明納米壓印光刻(NIL)較低的擁有成本,巖本將其與一種先進的氟化氬浸沒式光刻系統(極紫外光刻(EUV)光刻技術的前身,目前仍被廣泛使用)進行了比較,該系統用于制造密集排列的20納米寬的接觸孔。Iwamoto表示,對于相同的產量,每小時加工80個晶圓(wph)的納米壓印光刻系統能夠將擁有成本降低43%。佳能的目標是采用每小時加工100個晶圓的方案,通過進一步減少微粒污染、提高光刻膠質量以及改進和優化納米壓印光刻工作流程,使每個復制掩模能夠生產340批產品。巖本估計,實現這一目標后,與浸沒式光刻相比,擁有成本將降至59%。

早期采用方案?

盡管有潛在優勢,但要吸引那些已經在主流極紫外光刻(EUV)技術上投入大量資金的器件制造商在其生產運營中增加一種不同類型的光刻系統絕非易事。

“極紫外光刻(EUV)技術在過去十年間已經確立了自己的主流技術地位,”Hassanein說,“它克服了許多挑戰,具備高生產率,并且有制造更小圖案的發展路徑。如果納米壓印光刻(NIL)要參與競爭,就需要加快生產能力、延長模具壽命、改善微粒和碎屑管理并提高產量。”

但首先,這項技術得進入工廠才行。Iwamoto表示,在收到來自日本國內外潛在客戶的一些詢問之后,他們正在進行洽談并提供納米壓印光刻(NIL)的演示。佳能稱,除了向Texas Institute for Electronics交付首套商用系統之外,Kioxia(以前名為Toshiba Memory)已經對納米壓印光刻系統進行了數年測試,現在正在評估利用該工藝生產原型存儲芯片。

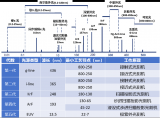

Iwamoto還指出,佳能正在積極推進納米壓印光刻應用路線圖。從2028年開始,其目標是生產能夠制造出線寬為20納米、套刻精度為5納米的三維NAND閃存的高分辨率掩模(https://spectrum.ieee.org/flash-memory)。對于動態隨機存取存儲器(DRAM),目標是達到線寬10納米、套刻精度2納米,而邏輯器件計劃達到線寬8納米、套刻精度1.6納米。如果這些目標能在那個時間框架內實現,同時還能提高晶圓產量,那么納米壓印光刻(NIL)可能會成為極紫外光刻(EUV)的一個有吸引力的替代方案,特別是對于精度和成本效益至關重要的應用而言。

審核編輯 黃宇

-

光刻機

+關注

關注

31文章

1153瀏覽量

47454 -

納米壓印

+關注

關注

0文章

10瀏覽量

6507

發布評論請先 登錄

相關推薦

美投資8.25億美元建設NSTC關鍵設施,重點發展EUV光刻技術

日本與英特爾合建半導體研發中心,將配備EUV光刻機

日本大學研發出新極紫外(EUV)光刻技術

替代EUV光刻,新方案公布!

買臺積電都嫌貴的光刻機,大力推玻璃基板,英特爾代工的野心和危機

光刻機的基本原理和核心技術

光刻機的發展歷程及工藝流程

佳能預計到2024年出貨納米壓印光刻機

納米壓印光刻技術旨在與極紫外光刻(EUV)競爭

納米壓印光刻技術旨在與極紫外光刻(EUV)競爭

評論