一年一度的ISSCC(International Solid State Circuits Conference的簡稱,中文名固態電路年會)正式拉開帷幕,在這個被稱為“集成電路奧利匹克”的會議上,來自全球各地的專家齊聚一堂,探討集成電路的未來。計算機體系專家David Paterson也在會議上發表了題為《50 Years of Computer Architecture:from Mainframe CPUs to DNN TPUs and Open RISC-V》的演講,讓我們看一下體系結構專家眼里的處理器未來。

對過去處理器發展的回顧

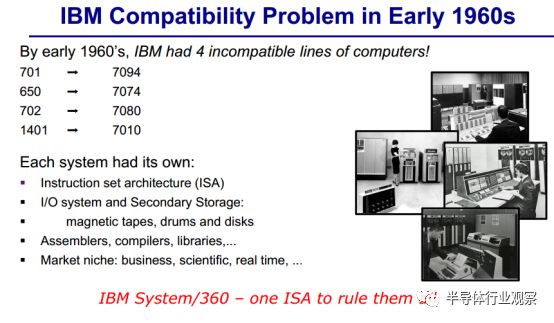

他表示,在20世紀60年代初,當時IBM同時擁有4條完全不兼容的產品線(701 ? 7094、650 ? 7074、702 ? 7080和1401 ? 7010),IBM面臨著非常嚴重的兼容性問題。其中每一條產品線都擁有各自完全獨立的指令集體系結構(ISA),I/O系統和二次存儲,磁盤存儲系統,匯編程序,編譯器,庫以及市場利基。

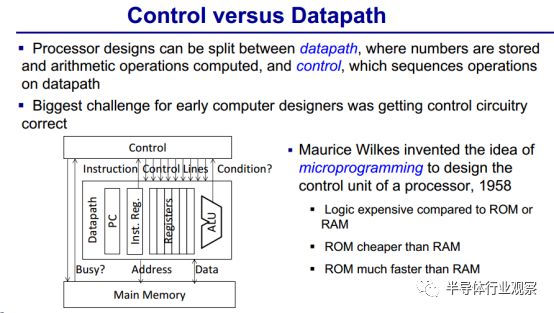

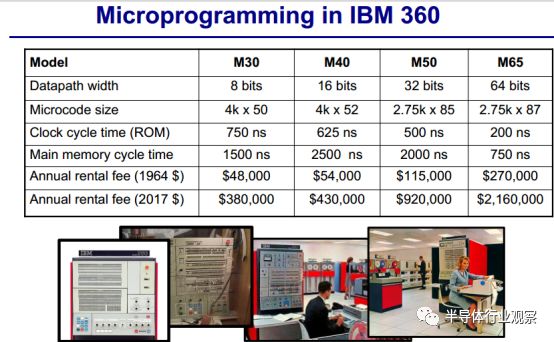

這幾條完全不兼容的產品線也使得當時的處理器設計變得異常復雜,設計者必須在數據存儲路徑和控制單元之間進行非常詳細的區分。可以說,早期的計算機設計者所面臨的最大問題就是控制單元的指令控制線是否正確,能夠起到作用。

此前,Maurice Wilkes在1958年提出了用微程序設計的思想來設計控制單元,簡化我們在設計過程中所遇到的問題,這種情況之下,我們只需要考慮一下幾個問題:ROM和RAM的價格問題,ROM比RAM便宜,而且ROM比RAM速度更快。

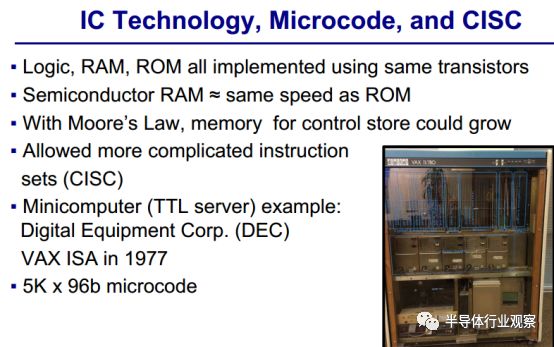

隨著IC技術、微指令和CISC的發展,Logic、RAM和ROM都應用了相同的晶體管;半導體RAM和ROM的速度也差不多;隨著摩爾定律的發展,控制指令的存儲空間也逐漸增加;允許更多的CISC;類似TTL 服務器這樣的小型計算機的出現,推動處理器產業進入了新階段。

伴隨而來的是微處理器技術的革新。

David Paterson表示,上世紀70年代,在MOS技術和主流ISA的推動下,計算機經歷了快速的發展,出現了以Intel i432為代表的產品。

之后也推出了Intel 8086等劃時代的產品。

之后就到了微指令機器的二十世紀八十年代。

從CISC到RISC,架構面臨瓶頸

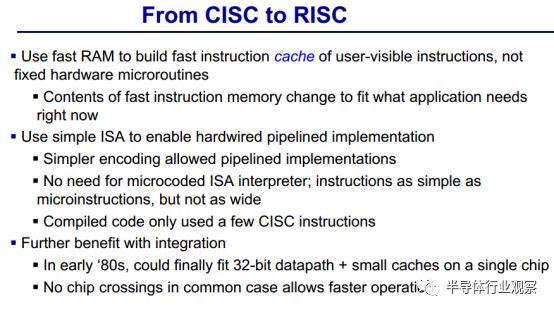

計算機發展之初,ROM比起RAM來說更便宜而且更快,所以并不存在片上緩存(cache)這個東西。在那個時候,復雜指令集(CISC)是主流的指令集架構。然而,隨著RAM技術的發展,RAM速度越來越快,成本越來越低,因此在處理器上集成指令緩存成為可能。

同時,由于當時編譯器的技術并不純熟,程序都會直接以機器碼或是匯編語言寫成,為了減少程序設計師的設計時間,逐漸開發出單一指令,復雜操作的程序碼,設計師只需寫下簡單的指令,再交由CPU去執行。

但是后來有人發現,整個指令集中,只有約20%的指令常常會被使用到,約占整個程序的80%;剩余80%的指令,只占整個程序的20%。

于是1979年,David Paterson教授提出了RISC的想法,主張硬件應該專心加速常用的指令,較為復雜的指令則利用常用的指令去組合。使用精簡指令集(RISC)可以大大簡化硬件的設計,從而使流水線設計變得簡化,同時也讓流水線可以運行更快。

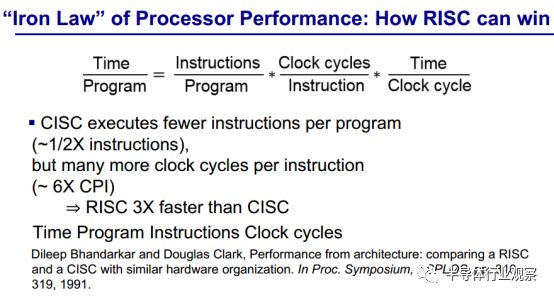

Paterson教授重申了評估處理器性能的指標,即程序運行時間。程序運行時間由幾個因素決定,即程序指令數,平均指令執行周期數(CPI)以及時鐘周期。程序指令數由程序代碼,編譯器以及ISA決定,CPI由ISA以及微架構決定,時鐘周期由微架構以及半導體制造工藝決定。對于RISC,程序指令數較多,但是CPI遠好于CISC,因此RISC比CISC更快。

據介紹,RISC有以下多個優點:

指令長度固定,方便CPU譯碼,簡化譯碼器設計。

盡量在CPU的暫存器(最快的存儲器元件)里操作,避免額外的讀取與載入時間。

由于指令長度固定,更能受益于執行線路管線化(pipeline)后所帶來的效能提升。

處理器簡化,晶體管數量少,易于提升運作時脈。比起同時脈的CISC處理器,耗電量較低。

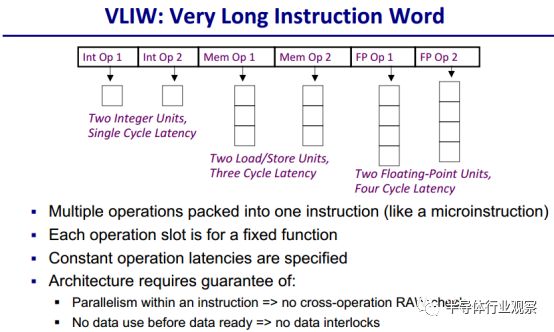

除了CISC和RISC之外,另一種流行(過)的ISA是超長指令字(VLIW)。

VLIW是美國Multiflow和Cydrome公司于20世紀80年代設計的體系結構,主要應用于Trimedia(全美達)公司的Crusoe和Efficeon系列處理器中。AMD的Athlon64處理器系列也是采用這一指令系統,包括其服務器處理器版本Operon。

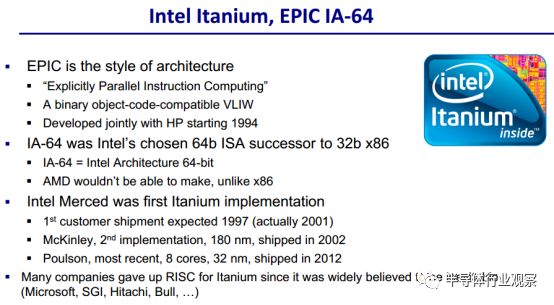

同樣Intel最新的IA-64架構中的EPIC也是從VLIW指令系統中分離出來的。VLIW架構采用了先進的EPIC(清晰并行指令)設計,我們也把這種構架叫做“IA-64架構”。每時鐘周期例如IA-64可運行20條指令,而CISC通常只能運行1-3條指令,RISC能運行4條指令,可見VLIW要比CISC和RISC強大的多。

之后David Paterson還談到了Intel 的安騰處理器和EPIC IA-64。

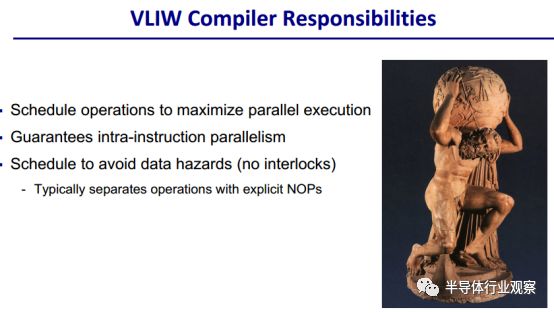

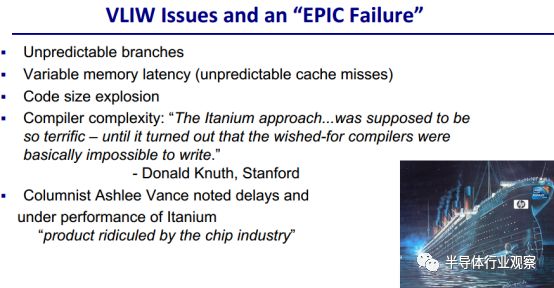

然而,VLIW架構遇到了巨大的失敗。VLIW的問題,包括分支預測困難,Cache miss無法解決,代碼爆炸以及最關鍵的,編譯器過于復雜以至于無法實現。

此外,基于VLIW指令集字的CPU芯片使得程式變得很大,需要更多的內存。更重要的是編譯器必須更聰明,一個低劣的VLIW編譯器對性能造成的負面影響遠比一個低劣的RISC或CISC編譯器造成的影響要大。

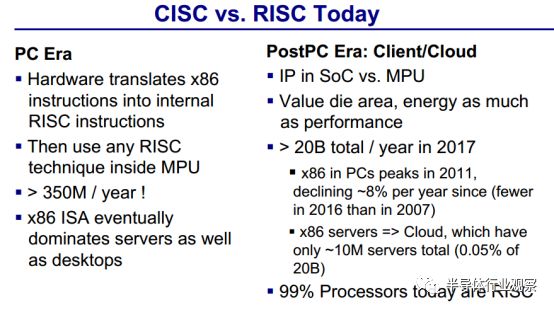

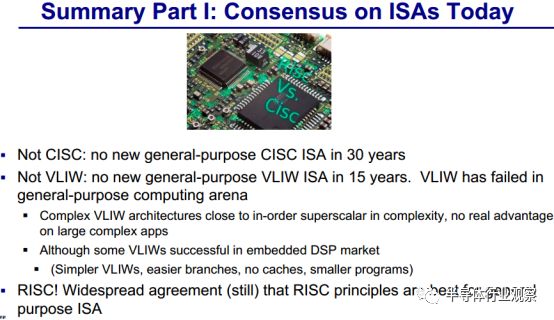

David Paterson還對今天的ISA做了一個總結。他指出,目前處理器的ISA,已經30多年沒有新的CISC ISA出現(Intel x86表面用的是CISC但是內部有硬件把CISC轉換成RISC再真正執行)。VLIW在一些嵌入式DSP市場獲得應用,但是在其他的市場都沒有獲得成功。考慮到處理器的數量,目前最主流的通用ISA還是RISC。

IT領域面臨新挑戰,TPU橫空出世

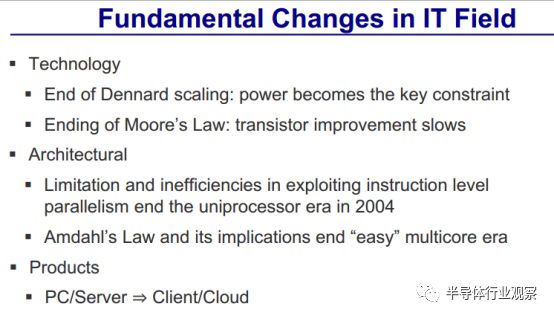

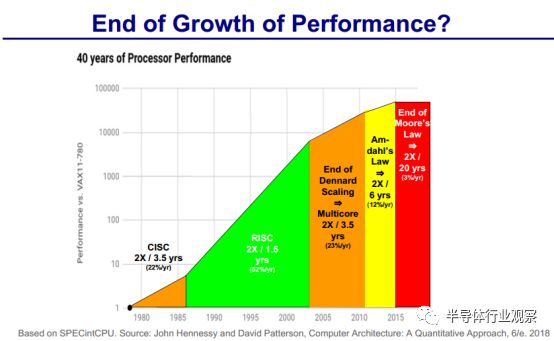

按照David Paterson的觀點,現在的IT技術面臨新的挑戰。例如登納德縮放定律的失效,功耗成為了關鍵的約束;摩爾定律也面臨困難,晶體管的提升變慢。另外,在架構上也有新的問題出現。

同時,處理器性能增長也面臨性能增長瓶頸。

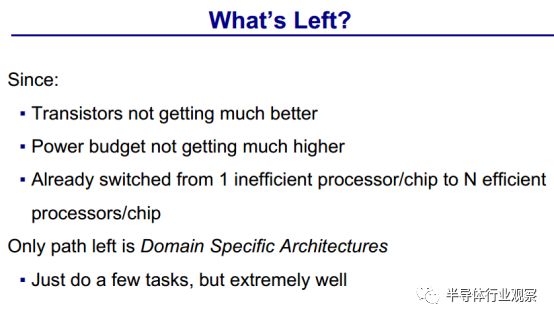

在David Paterson看來,對于任何運算來說,更換新硬件無非是為了兩個目的:更快的速度和更低的能耗。但由于面臨晶體管并沒有變得更好、功率預算也不高等問題。許多架構師認為,現在只有領域定制硬件(domain-specific hardware)能帶來成本、能耗、性能上的重大改進。

緊接著,David Paterson介紹了谷歌的TPU。

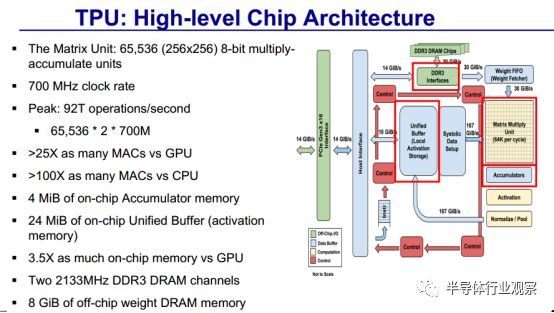

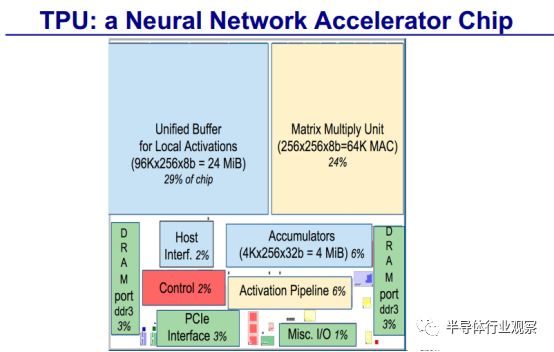

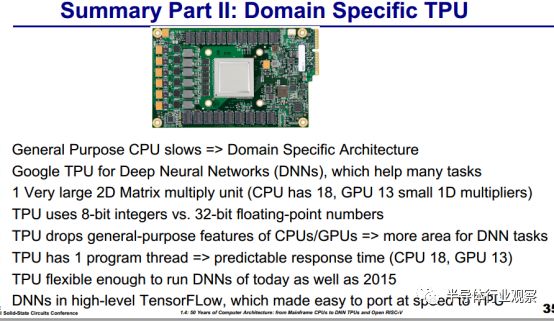

TPU 的核心是一個65,536的8位矩陣乘單元陣列(matrix multiply unit)和片上28MB的軟件管理存儲器,峰值計算能力為92 TeraOp/s(TOPS)。

與CPU和GPU由于引入了Cache、亂序執行、多線程和預取等造成的執行時間不確定相比,TPU 的確定性執行模塊能夠滿足 Google 神經網絡應用上 99% 相應時間需求。

CPU/GPU的結構特性對平均吞吐率更有效,而TPU針對響應延遲設計。正是由于缺乏主流的CPU/GPU硬件特性,盡管擁有數量巨大的矩陣乘單元 MAC 和極大的偏上存儲,TPU 的芯片相對面積更小,耗能更低。

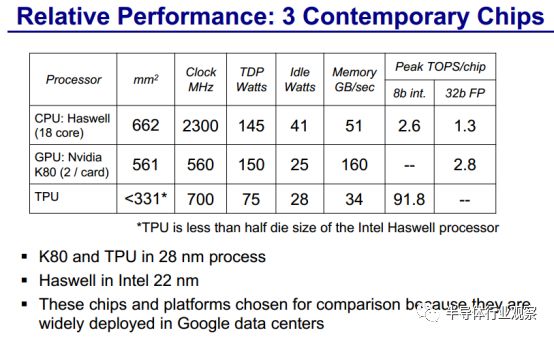

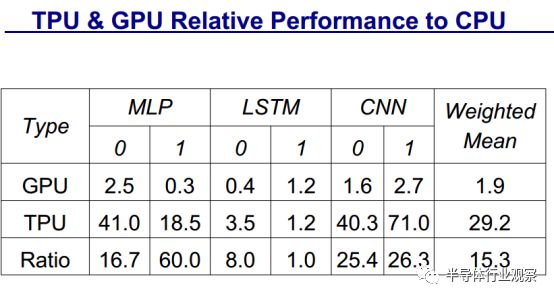

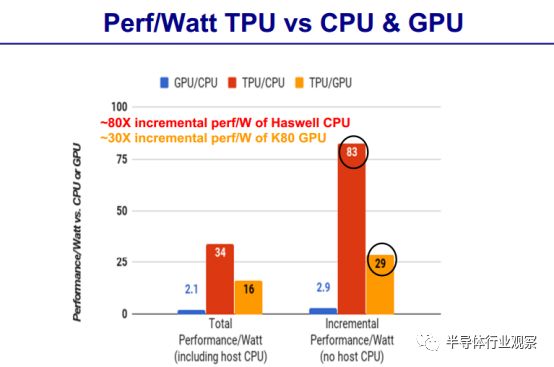

根據David Paterson的介紹,TPU是一個神經網絡加速器芯片,將 TPU 與服務器級的 Intel Haswell CPU 和 Nvidia K80 GPU 進行比較,這些硬件都在同一時期部署在同個數據中心。測試負載為基于 TensorFlow 框架的高級描述,應用于實際產品的 NN 應用程序(MLP,CNN 和 LSTM),這些應用代表了我們數據中心承載的95%的 NN 推理需求。

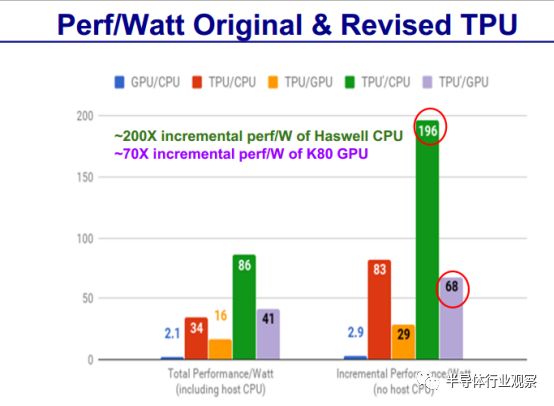

盡管在一些應用上利用率很低,但 TPU 平均比當前的 GPU 或 CPU 快15~30倍,性能功耗比(TOPS/Watt)高出約 30~80 倍。此外,在 TPU 中采用 GPU 常用的 GDDR5 存儲器能使性能TPOS指標再高 3 倍,并將能效比指標 TOPS/Watt 提高到 GPU 的 70 倍,CPU 的 200 倍。

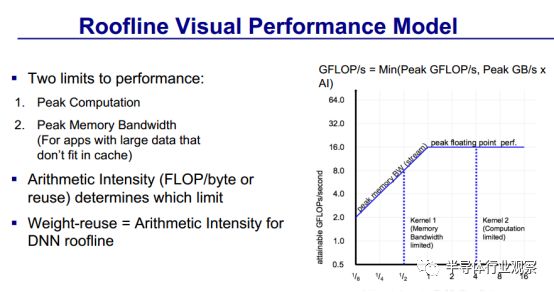

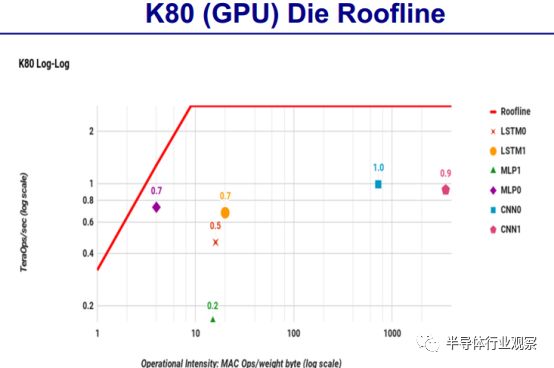

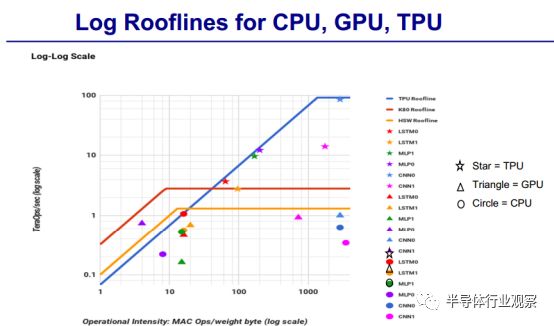

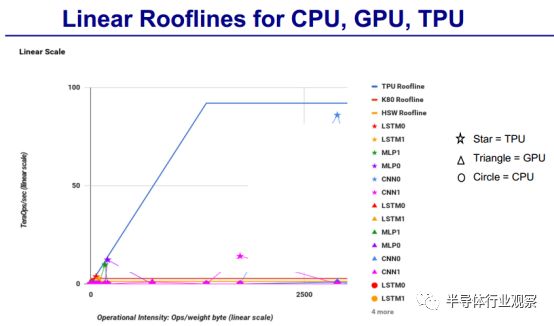

David Paterson還做了一個可視的性能模型。

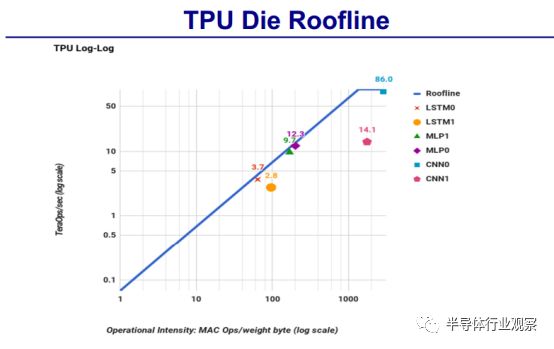

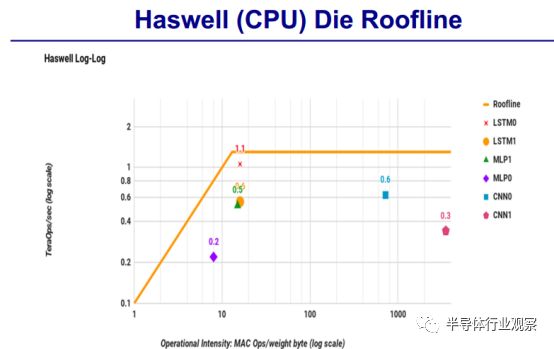

還對TPU /CPU/GPU 的Die Roofline做了對比。

TPU:

CPU:

GPU:

之后David Paterson還對CPU、GPU和TPU的Log Rooflines做了對比。

另外還有Linear Rooflines

他還將TPU & GPU的相關性能與CPU對比

在性能方面,David Paterson也做了對比。

還對TPU做了數據對比

按照David Paterson的總結了通用CPU開始變慢,特定架構的處理器將會流行與谷歌的TPU在DNN中發生重要作用,能夠幫助完成不少任務等問題:

RISC V也是未來的一個機遇

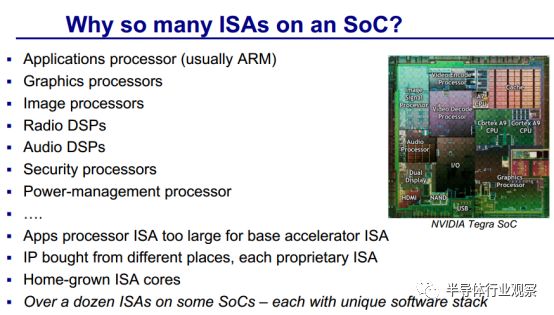

David Paterson表示,SoC上擁有了很多ISA。

緊接著,他提出,我們是否真的需要不同的ISA?這些指令集是否真的需要歸屬于專人?

況且在ISA領域,之前并沒有公認的標準,也沒有開源免費的ISA,僅有商用的ISA,這讓整個ISA領域的生態顯得死氣沉沉。David Paterson就提出了是否存在一個免費的ISA讓所有人都能夠使用的問題?于是,RISC-V應運而生。

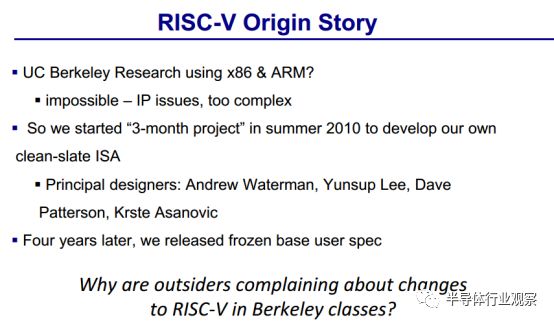

要做開源的ISA,基于x86和ARM都幾乎不可能,因為它們都太復雜,而且還存在IP的問題。

在2010年夏天,Paterson教授帶領團隊開始從頭開始設計一個干凈的ISA。經歷了很多年,經過多次流片驗證,終于在2014年發布了最終版spec,就是RISC-V(V是第五代的意思)。

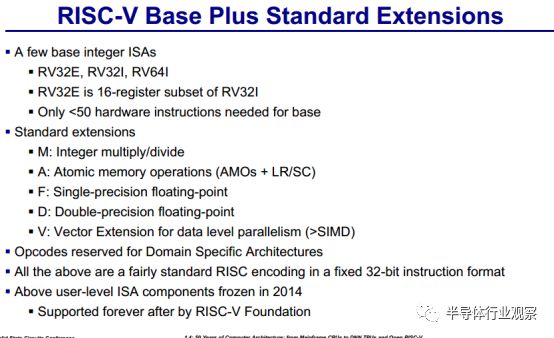

RISC-V作為一個開源ISA,首先要滿足對ISA的一般要求。

首先,它必須與現存的主流編程語言和軟件兼容。

第二,它必須有直接硬件實現,而不是一個虛擬機。

第三,它必須有很好的彈性,能滿足小至微控制器(MCU)大到超級計算機的需求。

第四,能與各種實現方式兼容,包括FPGA,ASIC,全定制CPU,以及未來的其他實現。

第五,需要與各種微架構配適,包括有序執行,無序執行,單發射,超標量等等。

最后,還需要滿足可擴展性(可以作為基礎ISA,在特殊用途中加上額外的增強ISA),以及穩定性(不會一直變化,不會突然消失等等)。

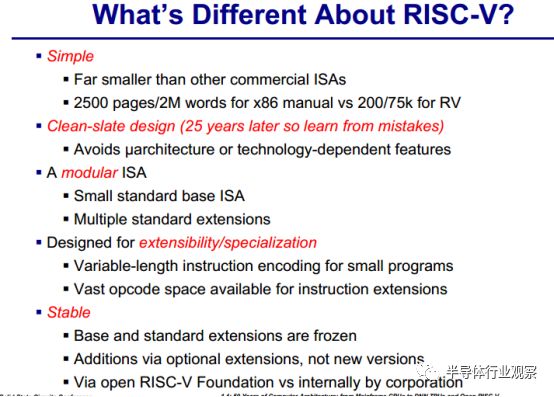

除了滿足一般的需求外,RISC-V還有自己的特色。

這個新近流行的架構還具備以下特點:

首先,它很簡單,比其他的商用ISA規模都要小很多。

第二,它很干凈,例如在用戶與特權ISA之間涇渭分明,有非常清晰的界限。另外,RISC-V中沒有與微架構或實現方式有關的特性,因此具有普適性。

第三,RISC-V是模塊化的ISA,它的基礎ISA集很小,但是可以根據用戶需求去加載擴展集。

最后,RISC-V特別為了可擴展性和專精化做了優化,使用了可變長度的指令編碼,并且有許多空間以供指令集擴展。

最特別的一點是,RISC-V支撐了一個開源的社區,包含了非盈利基金會以及開源代碼庫。RISC-V的愿景是未來各種靈活而低價處理器芯片的基礎。RISC-V一開始的貢獻者包括伯克利和SiFive(一家初創公司),目前在征求各類設計者加入開源社區,需要代碼以及其他硬件IP(如PLL,PHY等等)。

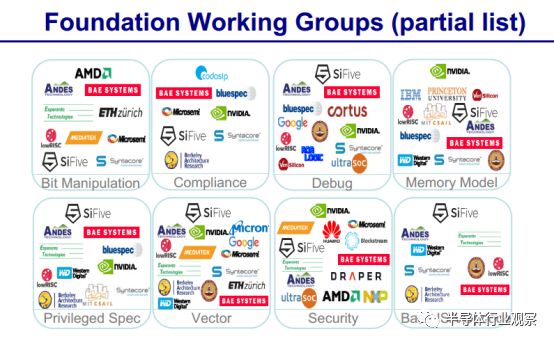

現在的RISC-V聯盟擁有了過百個會員:

另外還有很多的工作組:

David Paterson最后還總結一下幾大使用RISC和RISC-V的理由。

第一,35年以來,RISC始終是一個好主意。

第二,RISC-V是免費開源架構,無須付費。

第三,它的ISA比起其他ISA來說簡單許多,因此驗證起來也方便許多。RISC-V可以在各種設計中比起其他ISA更高效,面積、功耗和性能都更好

第四,RISC-V很穩定,不用擔心突然發生很大變化或者直接就消失。

第五,RISC-V可以作為各種SoC核的基礎ISA。

現在RISC-V的小目標,是成為一種適合各種計算設備的業界標準ISA。一個新的處理器時代即將到來。

-

ISA

+關注

關注

0文章

55瀏覽量

43747 -

TPU

+關注

關注

0文章

141瀏覽量

20730 -

開源架構

+關注

關注

0文章

8瀏覽量

6957 -

處理器架構

+關注

關注

0文章

8瀏覽量

6681

原文標題:David Paterson眼里的處理器架構未來

文章出處:【微信號:icbank,微信公眾號:icbank】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

專家與處理器架構未來

專家與處理器架構未來

評論