在高速數字電路設計中,信號完整性(SI)是確保系統性能和可靠性的核心要素。高速信號線的走線規則對于維持信號質量、減少噪聲干擾以及優化時序性能至關重要。本文將深入探討高速信號線走線的關鍵規則,旨在為工程師提供全面的設計指導和實踐建議。

一、屏蔽與接地規則

屏蔽處理:對于時鐘等關鍵高速信號,必須進行屏蔽處理。屏蔽線能夠減少電磁干擾(EMI)的泄露,提高信號的抗干擾能力。建議每1000mil處打孔接地,以增強屏蔽效果。

就近接地:屏蔽線應盡可能就近接地,以減少接地回路的電感,降低噪聲干擾。

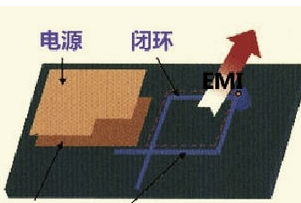

二、避免閉環與開環結構

在多層板走線時,應避免高速信號網絡形成閉環或開環結構。閉環結構可能產生環形天線效應,增加EMI輻射強度;而開環結構則可能形成線形天線,同樣增加EMI輻射。因此,確保高速信號走線不形成環路是減少天線效應、降低EMI輻射的關鍵。

三、特性阻抗連續規則

高速信號在層間切換時,必須確保特性阻抗的連續性。同層布線寬度應保持一致,不同層間的走線阻抗也應保持連續。這有助于減少信號反射和衰減,提高信號傳輸質量。

四、布線方向規則

相鄰兩層間的走線應遵循垂直走線原則。這種走線方式可以抑制線間串擾,降低信號間的互相干擾,提高信號傳輸的穩定性。

五、拓撲結構規則

根據信號頻率的不同,選擇合適的拓撲結構至關重要。低頻信號可采用菊花鏈式拓撲結構,而高頻信號則宜采用后端星形對稱結構。這種布局可以平衡信號負載,提高信號傳輸效率。

六、走線長度諧振規則

為避免諧振現象的產生,必須檢查信號線長度及信號頻率是否構成諧振條件。當布線長度為信號波長1/4的整數倍時,可能產生諧振。因此,在布線設計時,應調整信號線長度,避免諧振現象的發生。

七、回流路徑規則

高速信號必須擁有良好的回流路徑。工程師應盡可能減少時鐘等高速信號的回流路徑面積,以降低輻射強度。良好的回流路徑有助于減少電磁輻射,提高信號完整性。

八、退耦電容擺放規則

合理的退耦電容擺放位置可有效減少電源噪聲對信號的影響。退耦電容應靠近電源管腳,確保電容的電源走線和地線所包圍的面積盡可能小。這有助于抑制電源噪聲,提高信號質量。

九、差分傳輸線規則

高速信號通常通過差分傳輸線進行傳輸,以提高抗干擾性和信噪比。確保差分線對稱匹配、長度相等以及阻抗匹配是關鍵。這有助于減少差分信號間的串擾,提高信號完整性。

十、仿真與分析規則

使用電磁仿真工具(如SIWave、HyperLynx等)來分析高速信號的傳輸和反射是設計過程中的重要步驟。仿真可以幫助發現潛在問題并進行優化,確保設計滿足信號完整性的要求。

結論

綜上所述,高速信號線的走線規則是確保信號完整性的關鍵要素。通過遵循屏蔽與接地、避免閉環與開環結構、保持特性阻抗連續、遵循布線方向、選擇合適的拓撲結構、避免諧振、優化回流路徑、合理擺放退耦電容、使用差分傳輸線以及進行仿真與分析等規則,工程師可以設計出高性能、高可靠性的高速數字電路。隨著技術的不斷發展,未來將有更多先進的技術和方法被應用于高速信號線走線規則中,為電子產品的設計和制造提供更高效、更可靠的解決方案。

審核編輯:陳陳

-

信號完整性

+關注

關注

68文章

1417瀏覽量

95695 -

走線

+關注

關注

3文章

117瀏覽量

24002 -

高速信號

+關注

關注

1文章

232瀏覽量

17771 -

數字電路設計

+關注

關注

0文章

22瀏覽量

12693

發布評論請先 登錄

相關推薦

硬件工程師談高速PCB信號走線規則TOP9

評論