眾所周知,工業產品所應用的電磁環境之惡劣。要想產品在如此惡劣的電磁環境下正常工作,需要具備強大的抗干擾能力方能勝任。其中以靜電干擾最為常見且棘手。本文將手把手教你如何將工業產品做到可靠的防靜電設計。

1.了解靜電

你想要打倒對手,必須先深入地了解他,才能有的放矢。什么是靜電放電?相信大家都有著深刻且痛的領悟:冬天懶懶地從椅子上起身給開門,在你的手與金屬門把手即將親密接觸那一刻,一股精神倍爽的刺痛感自手指神經未梢迅速傳至慵懶的大腦皮層,讓你情不自禁的“啊”出來。讓你產生刺痛感的,便是靜電放電(ESD)在搞的鬼!

生活中和電子產品所承受的靜電放電,主要來自于摩擦起電。任何兩個物質摩擦都會產生靜電,只是起電量大小不同而已,得電子的帶負電,失電子的帶正電。這個是小學三年級都會學習的知識點。但也就是這在小學就學過的小小靜電放電,卻成為不少電子工程師心中揮之不去的夢魘。

2.靜電放電為何會影響電子產品正常工作

科學家們根據物質相互摩擦后得失電子的能力,排序整理出了一份摩擦生產序列表。這里由正到負列舉部分材料序列:兔皮、玻璃、絲綢、鋁片、琥珀、滌綸、硅……。這些生活中常見的材料包含了導體、半導體和絕緣體。兩種絕緣體物質摩擦生電后,因絕緣體內電子不能自由移動,得到的電子將集聚在帶負電物質表面,形成強靜電場,其持續時間可長達數小時或幾天。當外界其它物質靠近帶電物質時,則可以形成強烈的ESD現象。

ESD有兩種典型的模型:人體模型HBM和機械模型MM。人體模型用于表示帶電人體放電時與器件或物體的相互作用。機械模型表示帶電導體源放電與器件或物體的相互作用。以下將最為常見及基本的人體模型來說明ESD是如何影響電子產品正常工作。

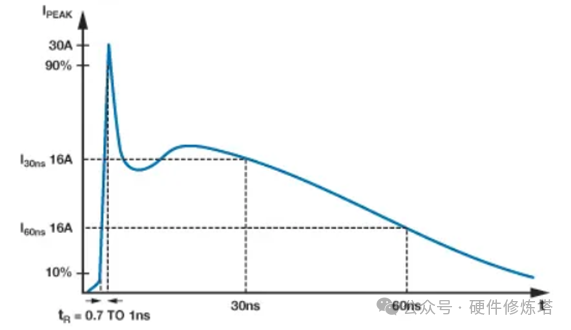

ESD對電子產品的影響主要體現在兩方面:過電應力EOS和電磁干擾EMI。在日常生活中因摩擦可使人體帶上幾千甚至上萬伏的靜電,國家標準GB/T 17626.2《電磁兼容試驗和測量技術靜電放電抗擾度試驗》規定的接觸放電試驗電壓為±8kV,空氣放電試驗電壓為±15kV。ESD的高電壓大電流會導致半導體器件出現閂鎖效應,甚至直接將多數半導體器件損壞。另外其放電波形如下圖示,ESD放電脈沖上升沿的時間非常短,只有0.7~1ns。這將形成強烈的電磁輻射干擾,帶寬可達400MHz以上,通過傳導和空間輻射的方式對系統中的敏感信號造成干擾。

3.工業產品防靜電設計

老生常談,產品設計之前必須了解設計需求:工業產品在無產品標準要求的情況下,需要滿足行業標準GB/T 17799.2-2003《電磁兼容通用標準工業環境中的抗擾度試驗》,靜電抗擾度試驗接觸放電±8kV,空氣放電±15kV。

3.1.原理圖設計

首先是芯片及核心板方案選型,有一顆強大的心臟才能支撐強健四肢去完成高難度的任務。

其次接口電路增加ESD保護設計,滿足先保護后濾波原則。根據不同接口電路的信號特性,選擇不同ESD保護器件。比如高速信號接口,需選擇寄生電容小的器件,否則會產生信號失真,導致通信失敗。

再者各電源電路必須增加大小規格的去耦電容,進行寬頻帶的濾波設計。比如常見的:10uF+1nF組合。

最后針對一些特殊的敏感信號線增加ESD保護和濾波設計,比如復位、AD采樣、時鐘等信號線。

3.2.PCB設計

靜電放電主要是以傳導和空間輻射的方式在板級進行干擾,因此PCB設計的核心思想是信號完整性和減小信號環路面積。故PCB的防靜電設計需要滿足的幾個重要原則:

電源、地平面盡量完整;

信號走線盡量等寬、等距、等長;

過孔數量盡量少;

不跨分隔區走線;

盡量單點接地走線;

信號環路面積盡量小;

接口和芯片濾波和保護器件盡量靠近接口和芯片放置;

3.3.結構設計

結構上防靜電有屏蔽與接地兩大方法。

屏蔽可從整機結構上設計,但這樣設計成本較高,產品體積較大,實現起來比較困難。除非是原本就是金屬結構的產品,利用原有金屬結構來做屏蔽效果。若是絕緣材料外殼產品,則需要在外殼內壁做噴涂導電漆。噴涂導電漆雖然是一種有效的屏蔽措施,但其生產工藝比較復雜,一致性控制難度大。整機設備中往往會存在不少死角的區域,讓噴涂導電漆工序難上加難。另外可針對單獨敏感電路模塊增加屏蔽殼,最為典型的便是手機屏蔽結構設計。

結構的接地設計需要考慮如何將靜電能量以最快的速度泄放掉。這就必須滿足接地良好,接地阻抗越小越好。特別是需要進行靜電放電試驗的區域,接地連續性要得到保證。在此要特別注意的一點是,作為靜電泄放的接地線不要從敏感信號或模塊上方經過,否則靜電泄放瞬間大電流所產生的強電磁場會對這些電路造成干擾,引起不必要的麻煩。

-

電子產品

+關注

關注

6文章

1170瀏覽量

58369 -

防靜電

+關注

關注

3文章

152瀏覽量

13026

原文標題:產品如何做到可靠的防靜電設計??

文章出處:【微信號:芯長征科技,微信公眾號:芯長征科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

對防靜電鞋的靜電效果檢查方法

汽車如何防靜電

電子產品防靜電方案介紹

電子產品防靜電設施

實施防靜電措施對產品設計及制造中的好處

請教下:不接地系統,如何做到預防靜電呢?

請問工控板在沒有接地的情況下,如何做到防雷,防靜電設計!

防靜電跨接線/法蘭靜電跨接線產品用途

防靜電椅怎么測試?

《電子產品防靜電設計》PPT全文分享

工廠常見的錯誤防靜電方法 靜電測試(ESD)方法

防靜電門禁的靜電檢測阻值標準是什么

防靜電地樁工程的流程和步驟

產品如何做到可靠的防靜電設計

產品如何做到可靠的防靜電設計

評論