1. TTL電平簡(jiǎn)介

TTL電平是一種數(shù)字信號(hào)標(biāo)準(zhǔn),它定義了邏輯高(1)和邏輯低(0)的電壓范圍。在TTL電路中,邏輯高通常是指+5V(或接近+5V)的電壓,而邏輯低是指0V(或接近0V)的電壓。這種電平標(biāo)準(zhǔn)使得TTL電路能夠清晰地區(qū)分?jǐn)?shù)字信號(hào)的高低狀態(tài)。

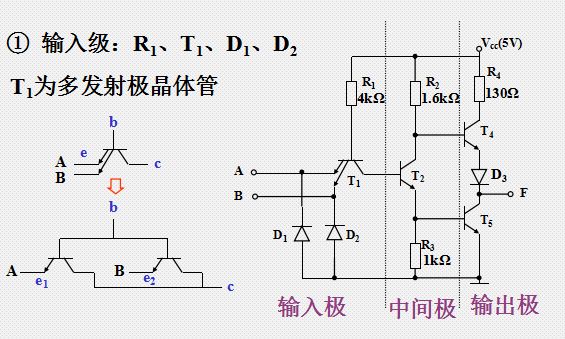

2. TTL電路的基本結(jié)構(gòu)

TTL電路的基本單元是邏輯門(mén),包括與門(mén)(AND)、或門(mén)(OR)、非門(mén)(NOT)、與非門(mén)(NAND)、或非門(mén)(NOR)等。每個(gè)邏輯門(mén)由多個(gè)晶體管組成,這些晶體管通過(guò)特定的連接方式實(shí)現(xiàn)邏輯功能。

3. TTL電路的工作原理

TTL電路的工作原理基于晶體管的開(kāi)關(guān)特性。在TTL電路中,晶體管通常工作在飽和區(qū)或截止區(qū),以實(shí)現(xiàn)邏輯門(mén)的功能。

- 飽和區(qū) :當(dāng)晶體管的基極-發(fā)射極電壓(VBE)大于晶體管的開(kāi)啟電壓(通常約為0.7V),晶體管導(dǎo)通,集電極-發(fā)射極電壓(VCE)接近0V,晶體管處于飽和狀態(tài)。

- 截止區(qū) :當(dāng)VBE小于開(kāi)啟電壓時(shí),晶體管截止,VCE接近電源電壓,晶體管不導(dǎo)電。

4. TTL邏輯門(mén)的實(shí)現(xiàn)

以一個(gè)簡(jiǎn)單的與門(mén)為例,它由兩個(gè)晶體管串聯(lián)組成。只有當(dāng)兩個(gè)輸入都為高電平時(shí),輸出才為高電平。這是因?yàn)橹挥挟?dāng)兩個(gè)晶體管都導(dǎo)通時(shí),電流才能從電源流到輸出端。

- 輸入高電平 :兩個(gè)晶體管導(dǎo)通,輸出為低電平(接近0V)。

- 輸入低電平 :至少有一個(gè)晶體管截止,輸出為高電平(接近+5V)。

5. TTL電路的優(yōu)點(diǎn)

- 速度快 :TTL電路的開(kāi)關(guān)速度相對(duì)較快,適合高速數(shù)字邏輯應(yīng)用。

- 功耗低 :盡管TTL電路的功耗相對(duì)較高,但與早期的電子管邏輯電路相比,它的功耗已經(jīng)大大降低。

- 成本低 :TTL電路的制造成本較低,適合大規(guī)模生產(chǎn)。

6. TTL電路的局限

- 噪聲容限小 :TTL電路的噪聲容限相對(duì)較小,容易受到噪聲干擾。

- 功耗較高 :與CMOS電路相比,TTL電路的功耗較高,不適合功耗敏感的應(yīng)用。

7. TTL與其他邏輯電平的比較

TTL電平與其他邏輯電平(如CMOS電平)的主要區(qū)別在于電壓范圍和功耗。CMOS電平使用更寬的電壓范圍,并且功耗更低,這使得CMOS電路在現(xiàn)代電子設(shè)備中更為流行。

8. TTL電路的應(yīng)用

TTL電路被廣泛應(yīng)用于計(jì)算機(jī)、微控制器、數(shù)字信號(hào)處理器等數(shù)字系統(tǒng)中,用于實(shí)現(xiàn)各種邏輯功能和接口電路。

9. 結(jié)論

TTL電平是一種歷史悠久的數(shù)字信號(hào)標(biāo)準(zhǔn),它通過(guò)晶體管的開(kāi)關(guān)特性實(shí)現(xiàn)了數(shù)字邏輯功能。盡管TTL電路在某些方面存在局限,但它的簡(jiǎn)單性和可靠性使其在許多應(yīng)用中仍然具有價(jià)值。

-

晶體管

+關(guān)注

關(guān)注

77文章

9723瀏覽量

138598 -

數(shù)字信號(hào)

+關(guān)注

關(guān)注

2文章

975瀏覽量

47604 -

集電極

+關(guān)注

關(guān)注

4文章

218瀏覽量

22214 -

TTL電平

+關(guān)注

關(guān)注

1文章

116瀏覽量

12042

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

TTL電平與信號(hào)降噪技術(shù)的區(qū)別

使用TTL電平時(shí)的常見(jiàn)問(wèn)題

TTL電平與高電平信號(hào)的轉(zhuǎn)換

TTL電平噪聲容忍度分析

TTL電平與低電平信號(hào)的區(qū)別

TTL電平的傳輸距離限制

TTL電平在數(shù)字電路中的作用

TTL電平標(biāo)準(zhǔn)的介紹與解析

TTL電平的應(yīng)用場(chǎng)景和實(shí)例

TTL電平與CMOS電平的區(qū)別是什么

TTL逆變器的定義和工作原理

TTL反相器的工作原理、應(yīng)用及優(yōu)勢(shì)

ttl與非門(mén)有哪些主要性能參數(shù) TTL與非門(mén)的工作原理

cmos電平與ttl電平如何轉(zhuǎn)換 怎么判斷ttl電路高低電平

TTL與非門(mén)典型電路及其工作原理詳解

TTL電平的工作原理詳解

TTL電平的工作原理詳解

評(píng)論