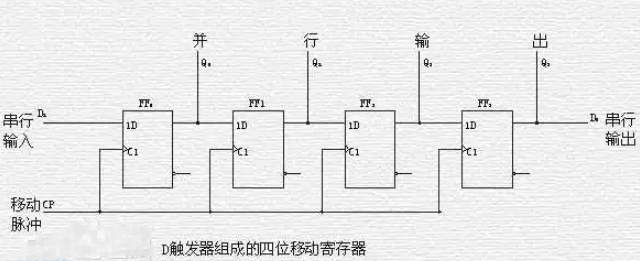

一、移位寄存器

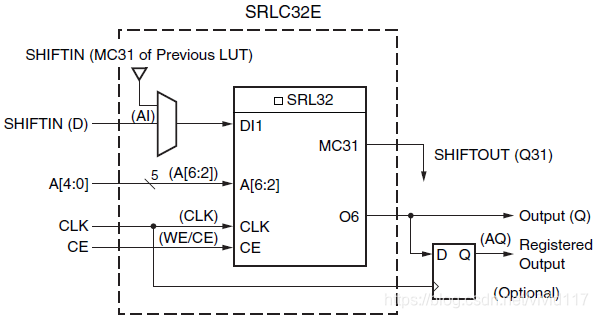

SLICEM函數發生器也可以配置為32位移位寄存器,而無需使用slice中可用的觸發器。以這種方式使用,每個LUT可以將串行數據延遲1到32個時鐘周期。

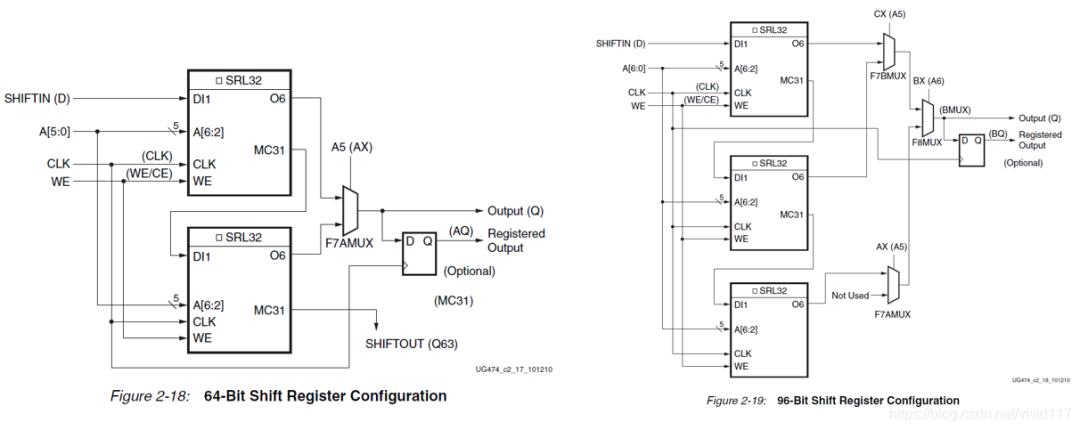

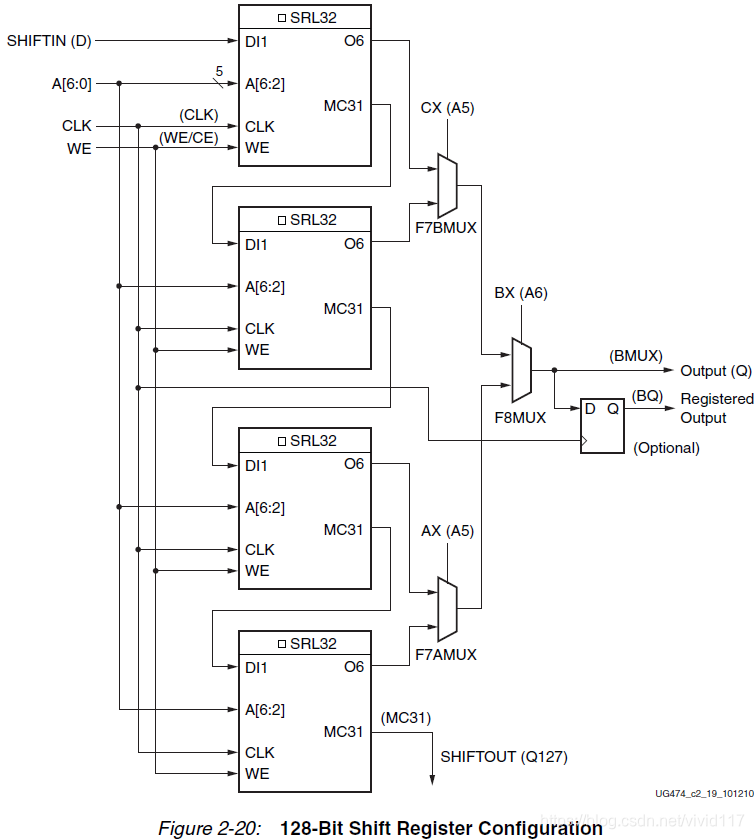

移入D(DI1 LUT引腳)和移出Q31(MC31 LUT引腳)線路將LUT級聯,以形成更大的移位寄存器。因此,SLICEM中的四個LUT被級聯以產生高達128個時鐘周期的延遲。也可以在多個SLICEM上組合移位寄存器。

寄存器,LUT B / C / D的MC31輸出也不可用。由此產生的可編程延遲可用于平衡數據流水線的時序。

下圖是SRL32位移位寄存器的框圖:

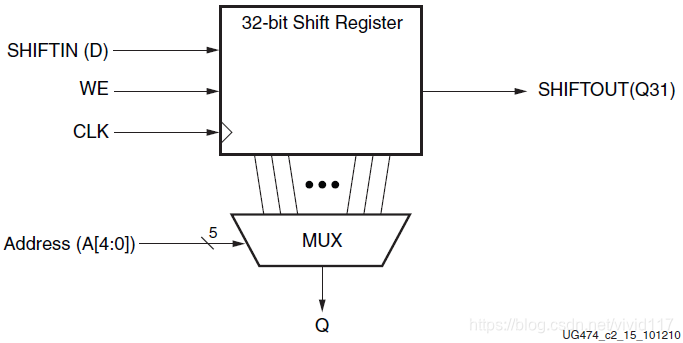

下圖是占用一個32位函數發生器的示例移位寄存器配置

二、 移位寄存器的功能與應用

移位寄存器的功能

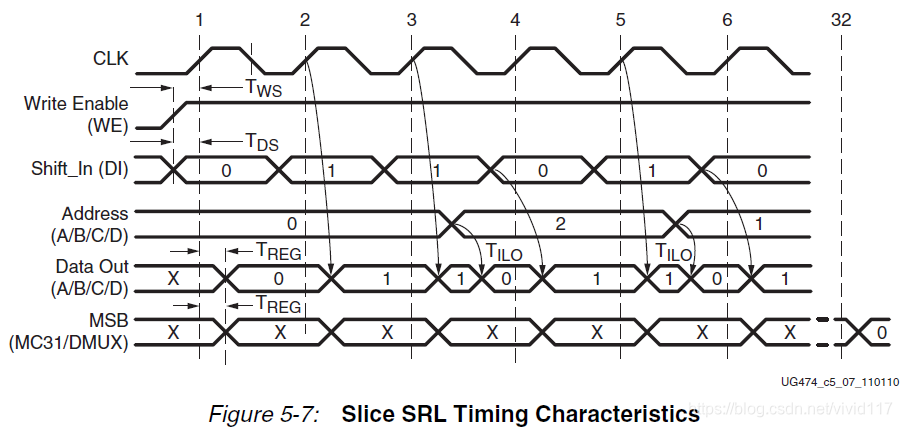

1)寫操作

2)與時鐘輸入(CLK)和可選的時鐘使能(CE)同步

3)修復對Q31的讀取訪問

4)動態讀取訪問

5)通過5位地址總線A [4:0]執行

LUT地址的LSB未使用,軟件自動將其綁定為邏輯高電平。

6)通過改變地址可以異步讀取32位中的任何一位(在O6 LUT輸出上,在原語上稱為Q)

7)此功能對于創建較小的移位寄存器(少于32位)很有用。

例如,當構建13位移位寄存器時,將地址設置為第13位。

8)存儲單元或觸發器可用于實現同步讀取。

觸發器的時鐘輸出決定了總延遲并改善了性能。但是,增加了一個時鐘延遲周期。

移位寄存器的應用:

1)延遲或延遲補償

2)同步FIFO和內容可尋址存儲器(CAM)

三、XILINX FPGA 中LUT 中移位寄存器的復用情況

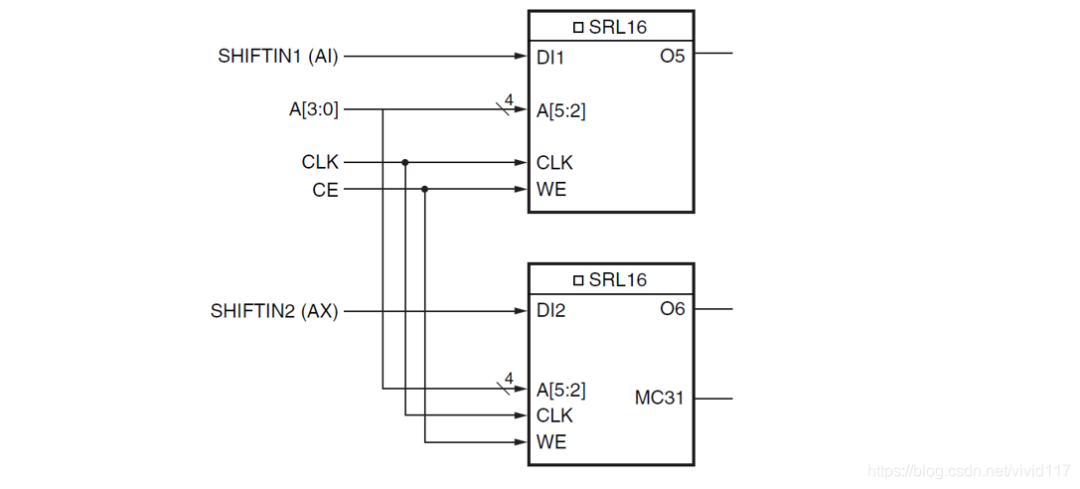

一個LUT可以用于產生2個16bit移位寄存器,地址是復用的。

用兩個SRL16組成一個32位的移位寄存器

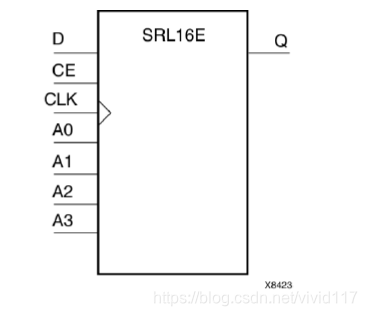

下圖是一個SRL 16E 帶使能信號的移位寄存器:

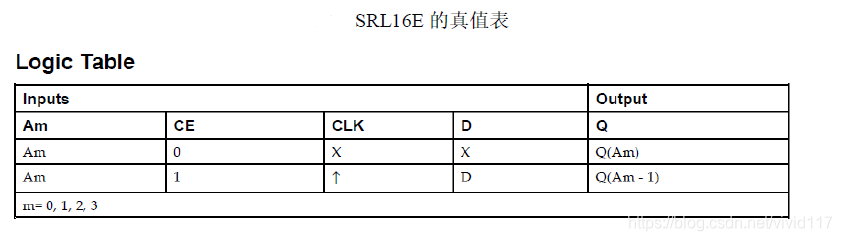

移位寄存器查找表,它的輸入這是一個移位寄存器查找表,它的輸入 A3,A2,A1和 A0選擇移位輸出的長度。

移位寄存器可以是固定的、靜態的長度,移位寄存器的長度可以從 1位到 16位不等,由下面公式決定:

長度 =(8 x A3)+(4 x A2)+(2 x A1)+A0+1

如果 A3,A2,A1,A0都是 0(0000),移位寄存器的長度就是 ),移位寄存器的長度就是 1位長;如果它們 都是 1(1111),移位寄存器的長度就是 ),移位寄存器的長度就是 ),移位寄存器的長度就是 16位長。

下表是SRL16E的真值表:

2.利用SRL32 組成 64/96/128 bit的移位寄存器,利用地址A5和F7AMUX切換SRL32

四、移位寄存器數據流

下圖舉例說明在7系列FPGA Slice(一個配置為SRL的LUT)中實現的移位寄存器的時序特性:

-

FPGA

+關注

關注

1639文章

21887瀏覽量

610859 -

移位寄存器

+關注

關注

3文章

284瀏覽量

22565 -

函數發生器

+關注

關注

0文章

151瀏覽量

19421

原文標題:XILINX FPGA CLB單元 之 移位寄存器

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

評論