在DC-DC芯片的應用設計中,PCB布板是否合理對于芯片能否表現出其最優性能有著至關重要的影響。不合理的PCB布板會造成芯片性能變差如線性度下降(包括輸入線性度以及輸出線性度)、帶載能力下降、工作不穩定、EMI輻射增加、輸出噪聲增加等,更嚴重的可能會直接造成芯片損壞。

一般DC-DC芯片的使用手冊中都會有其對應的PCB布板設計要求以及布板示意圖,本次我們就以同步BUCK芯片為例簡單講一講關于DC-DC芯片應用設計中的PCB Layout設計要點。

1、關注芯片工作的大電流路徑

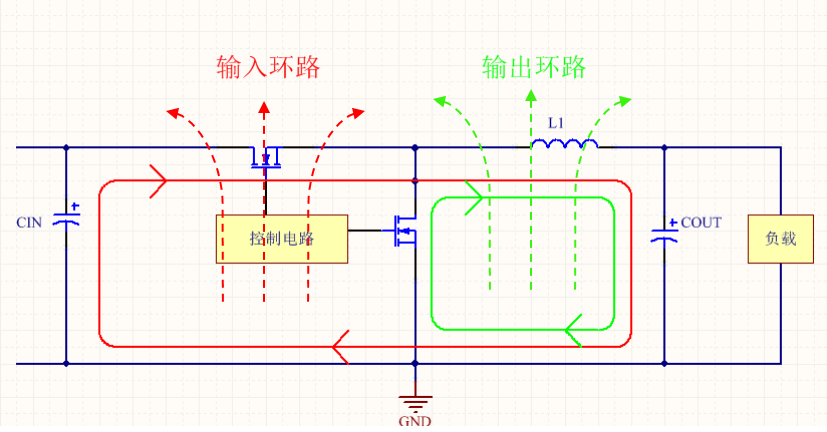

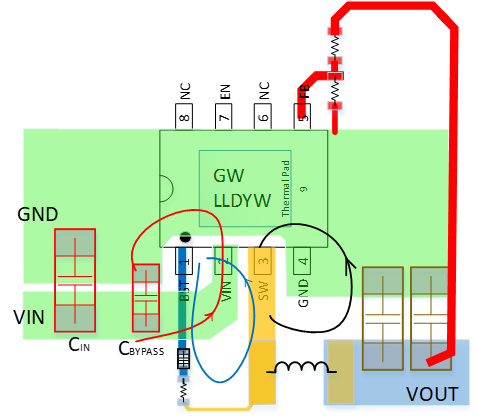

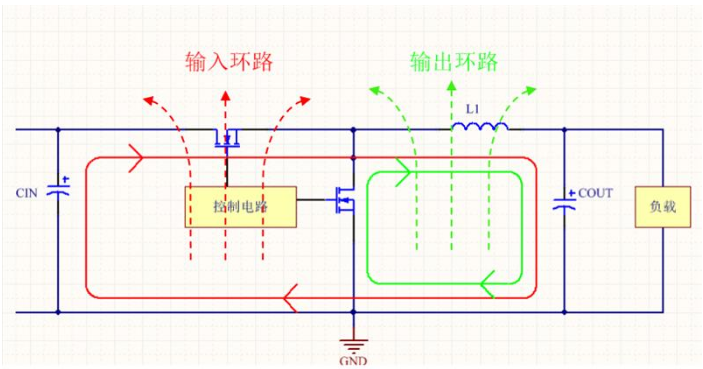

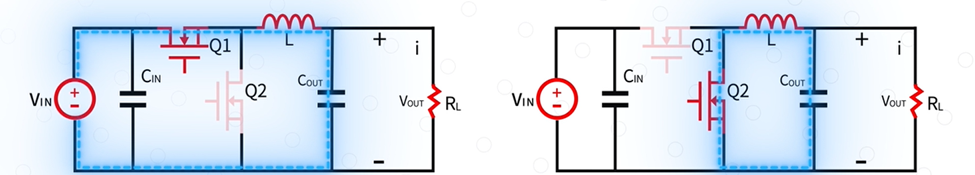

DC-DC芯片布板需遵循一個非常重要的原則,即開關大電流環路面積盡可能小。下圖所示的BUCK拓補結構中可以看到芯片開關過程中存在兩個大電流環路。紅色為輸入環路,綠色為輸出環路。每一個電流環都可看作是一個環路天線,會對外輻射能量,引起EMI問題,輻射的大小與環路面積呈正比。

(注意:當芯片引腳設置不足以讓我們同時兼顧輸入環路與輸出環路最小時,對于BUCK而言,應優先考慮輸入部分回路布線最優化。因為輸出回路中電流是連續的,而輸入回路中電流是跳變的,會產生較大的di/dt,會引起EMI問題的可能性更高。如果是BOOST芯片,則應優先考慮輸出回路布線最優化。)學硬件,熟能生巧,理論聯系實際,做整理多總結吧!2、輸入電容的配置

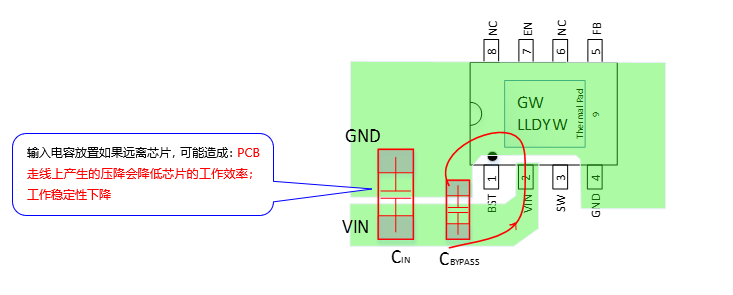

① 對于BUCK芯片而言,要想使輸入環路盡可能小,輸入電容應盡可能靠近芯片引腳放置;

② 為了讓電容濾波效果更好,讓電源先經過輸入電容,再進入芯片內部;

③ CIN使用的大容量電容器,一般情況下頻率特性差,所以要與CIN并聯頻率特性好的高頻率去耦電容器CBYPASS;

④ 電流容量小的電源(IO≤1A)場合,容量值也變小,所以有時可用1個陶瓷電容器兼具CIN和CBYPASS功能;

3、電感的配置

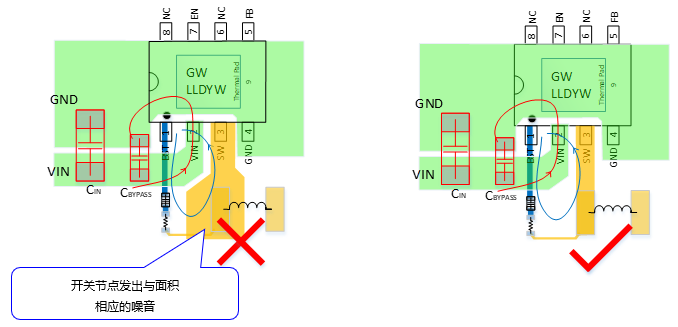

① 對于BUCK芯片而言,要想使輸入環路盡可能小,電感要靠近芯片SW引腳放置;

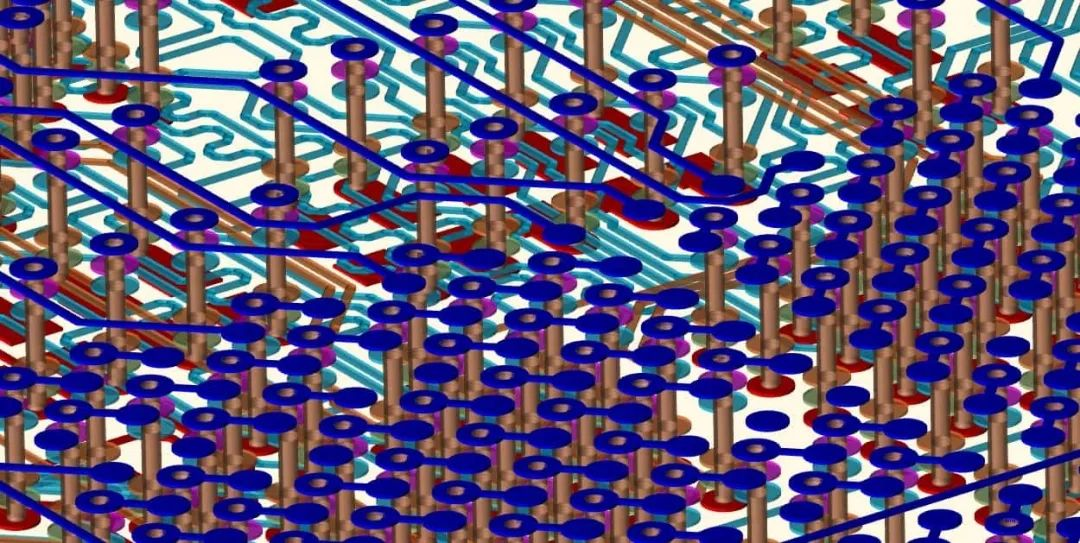

② 以覆銅方式走線減小寄生電感、電阻;

③ SW節點要以最小面積處理大電流,防止銅箔面積變大會起到天線的作用,使 EMI增加;

④ 電感附近不要走敏感信號線;

⑤ 自舉電路這一塊,自舉電路要盡量去靠近SW pin腳來縮短整個高頻的流通路徑;

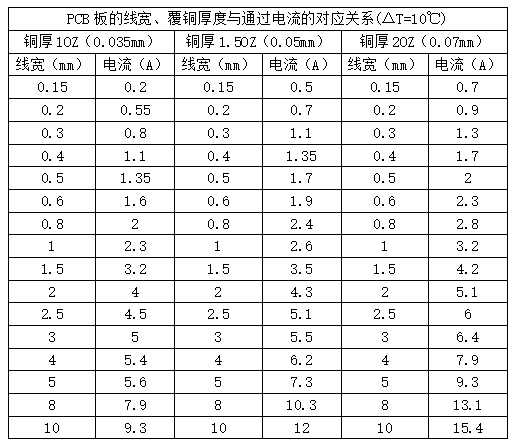

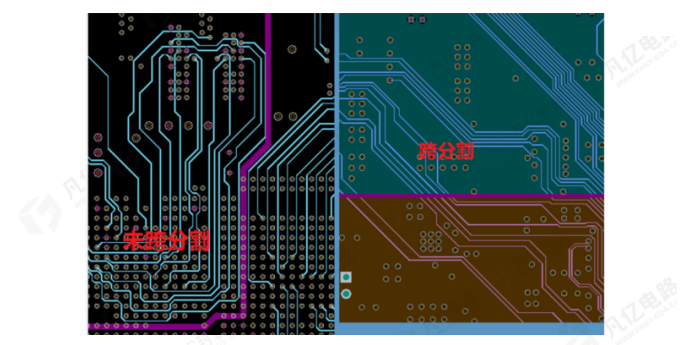

附上溫升10℃時,PCB板的線寬、覆銅厚度與通過電流的對應關系供參考。

4、輸出電容的配置

5、反饋路徑的布線

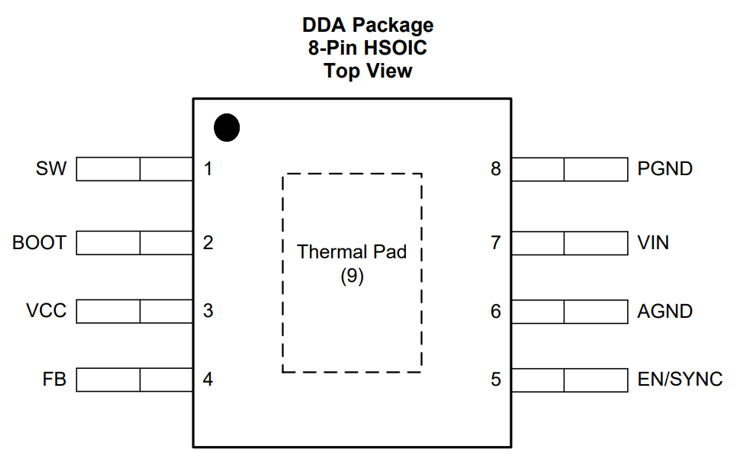

① 通常FB反饋網絡處的分壓電阻都采用K級,10K級或上百K的阻值,阻值越大,越容易受干擾,應遠離各種噪聲源如電感、SW、續流二極管等;

② FB、COMP腳的信號地盡可能地與走大電流的功率地隔離開,然后進行單點相連,盡量不要讓大電流信號的地去干擾到小信號電流的地;

③ FB的分壓電阻要從VOUT上進行采樣,采樣點要靠近輸出電容處才能獲得更準確的實際輸出電壓值;

聲明:

本號對所有原創、轉載文章的陳述與觀點均保持中立,推送文章僅供讀者學習和交流。文章、圖片等版權歸原作者享有,如有侵權,聯系刪除。

-

芯片

+關注

關注

456文章

51062瀏覽量

425810 -

buck電路

+關注

關注

28文章

485瀏覽量

46534 -

Pcb layout

+關注

關注

6文章

98瀏覽量

29185

發布評論請先 登錄

相關推薦

PCB Layout的設計要點

求AD10的詳細使用教程(包括線路原理圖設計和PCB LAYOUT)

PCB Layout pcb布局的基本原則

PCB Layout過孔散熱設計

關于PCB layout的EMC設計檢查建議

5條DC-DC PCB layout建議

非常詳細的BUCK電路 PCB layout建議

非常詳細的BUCK電路 PCB layout建議

評論