在現代電子設計中,PCB信號完整性是一個日益受到關注的話題。隨著物聯網和人工智能技術的快速發展,設備的小型化與高性能需求常常相互矛盾。芯片越小,操作復雜性越高,隨之而來的電磁干擾問題也日益凸顯。盡管解決這些問題可能充滿挑戰,但通過科學的設計方法和技術手段,完全可以在惡劣環境下實現信號完整性。以下是幾項關鍵的實踐建議。

1. 材料選擇是基礎

確保PCB信號完整性始于對材料的正確選擇。無論是元件還是基板,所選材料必須具備低損耗特性,能夠最大限度地減少信號衰減,同時適應極端環境的要求。比如,低介電常數的材料有助于降低高頻信號的干擾。

此外,材料的環境適應性也很重要。例如,高濕度環境可能導致某些基板材料吸濕,從而影響性能。為此,新型低耗散因數的聚合物材料(在10GHz下損耗因數低至0.001)正成為熱門選擇。盡管這些尖端材料可能增加成本,但在要求嚴苛的應用中,它們是值得投資的。

2. 優化走線長度和寬度

減少信號丟失的另一關鍵策略是優化PCB走線。過寬或過長的走線容易導致串擾或信號衰減。設計中應盡量縮短信號路徑,優化元件之間的布局,并保持信號回路緊湊。

如今,3D打印技術為優化走線提供了新的可能性。通過3D打印,可以直接在基板上構建微細走線,避免傳統開槽工藝的限制,進一步提高信號完整性。

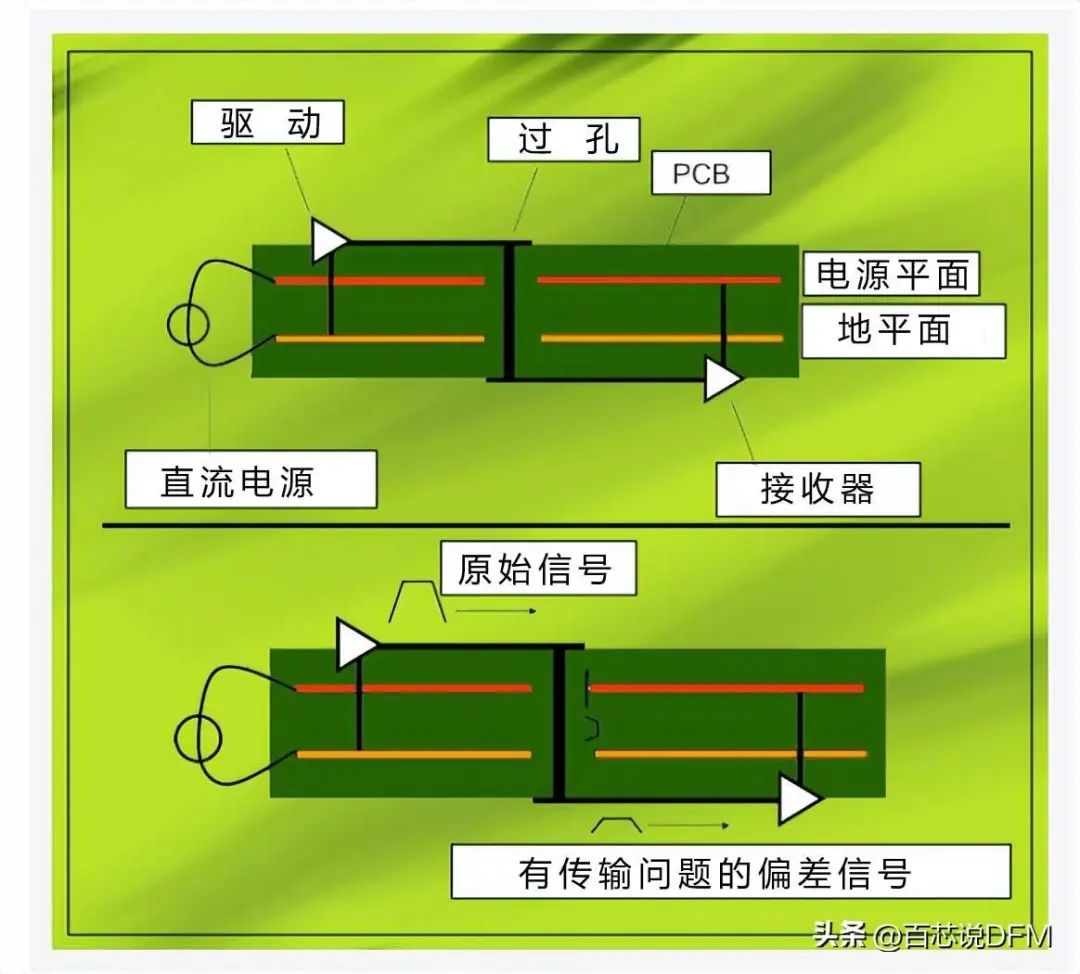

3. 合理接地與去耦設計

接地設計是高頻電路中的核心要素。多點接地平面不僅能有效抑制電磁干擾(EMI),還可提高電路的熱管理效率。在復雜電路中,建議為模擬信號和數字信號設置獨立接地,但需謹慎避免分離過大的接地點,因為這可能引發新的信號完整性問題。

去耦電容的布置同樣需要精確規劃。將去耦電容靠近信號源,并與電阻器配對使用,可在高頻環境下顯著提升性能。

4. 熱管理不可忽視

在尺寸受限且功率密集的PCB設計中,熱管理是確保信號完整性的關鍵。除傳統散熱器外,熱通孔和散熱墊也能有效引導熱量遠離敏感區域。通過優化元件布局,合理分散熱源,確保氣流通暢,可以避免局部過熱對信號質量的影響。

5. 電磁干擾(EMI)屏蔽

高頻PCB設計中,EMI屏蔽是信號完整性保障的重要環節。常見的屏蔽材料包括高導電性金屬網和彈性體絕緣材料。在某些應用中,濾波器也是良好的選擇,尤其是高功率設備可使用三相濾波器進行更全面的干擾抑制。

6. 全面測試設計

設計的可靠性需要通過多層次測試驗證。現代仿真工具可在設計階段模擬EMI、熱效應及阻抗特性,但仍需結合物理測試來應對真實使用環境。例如,軍用設備的MIL-STD-810標準要求設備在極端溫度、機械沖擊等條件下進行驗證,以確保其性能符合預期。

7. 借助人工智能提升設計效率

人工智能(AI)設計工具正在為PCB設計注入新的活力。AI可以快速識別設計中的瓶頸,并提出優化建議。例如,有些團隊已通過AI在10天內顯著提升芯片性能,同時降低功耗。然而,AI工具也需要經過嚴謹的訓練和驗證,設計師應結合實際測試結果使用這些工具。

持續改進是關鍵

在未來,隨著設備功能和環境要求的不斷提升,PCB信號完整性面臨的挑戰只會更加嚴峻。通過靈活應用上述最佳實踐,并密切關注新興技術和材料的動態,設計師能夠有效應對這些挑戰,開發出性能卓越、可靠性強的產品。

-

pcb

+關注

關注

4324文章

23143瀏覽量

398935 -

信號完整性

+關注

關注

68文章

1413瀏覽量

95551

原文標題:惡劣環境中的PCB信號完整性維護:挑戰與實踐

文章出處:【微信號:FANYPCB,微信公眾號:凡億PCB】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

惡劣環境中的PCB信號完整性維護的實踐建議

惡劣環境中的PCB信號完整性維護的實踐建議

評論