文章來源:半導體與物理

原文作者:jjfly686

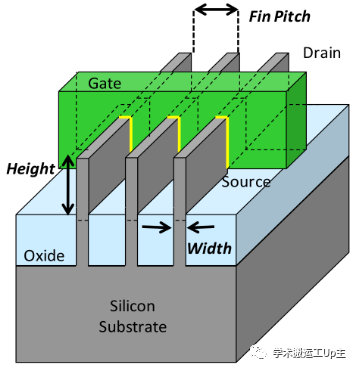

本文介紹了FinFET(鰭式場效應晶體管)制造過程中后柵極高介電常數金屬柵極工藝的具體步驟。

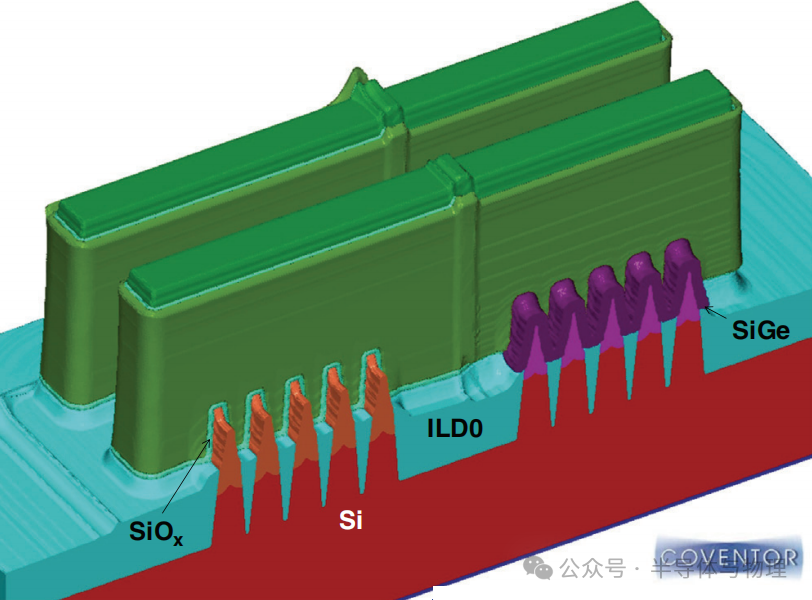

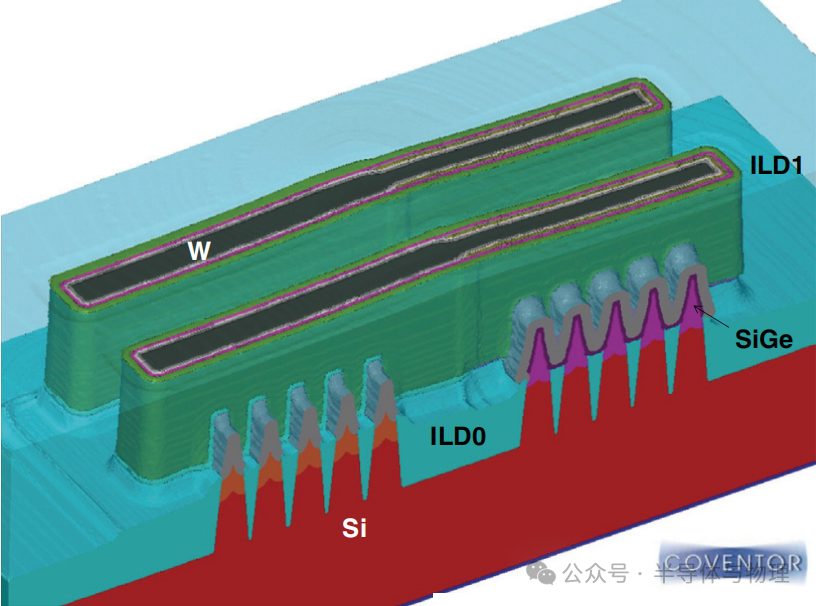

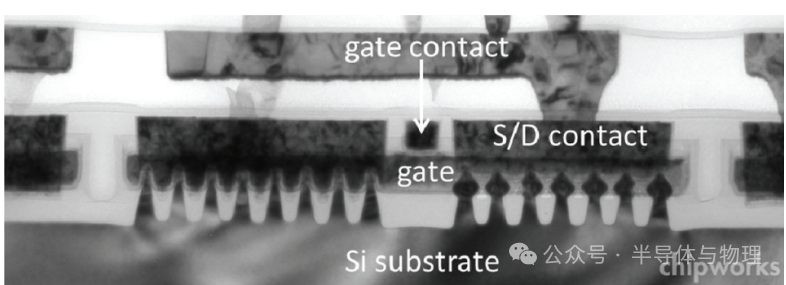

在FinFET(鰭式場效應晶體管)制造過程中,當自對準硅化物(self-aligned silicide, salicide)過程完成,在源(Source)和漏(Drain)區形成了低電阻接觸之后,晶圓就準備好進入替換柵極(replacement gate)或稱為后柵極(gate-last)高介電常數金屬柵極(High-k Metal Gate, HKMG)工藝階段。以下是該過程中每一步驟的具體內容及其作用:

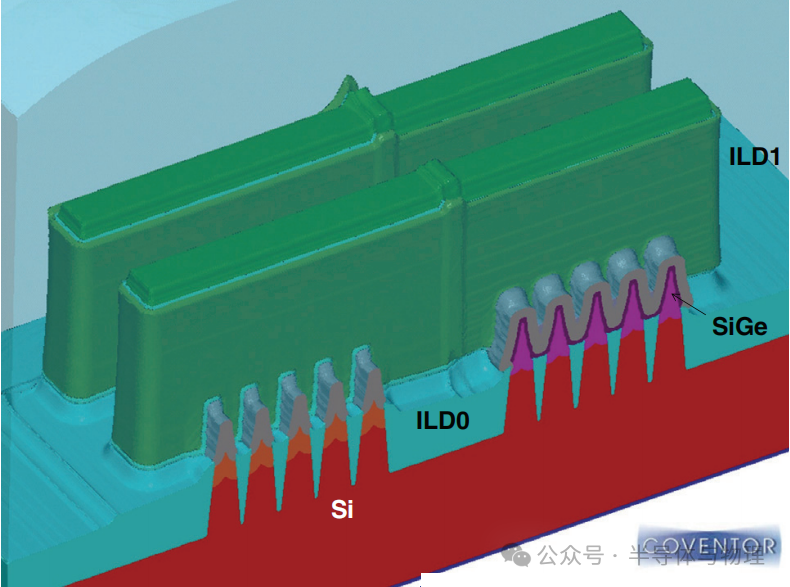

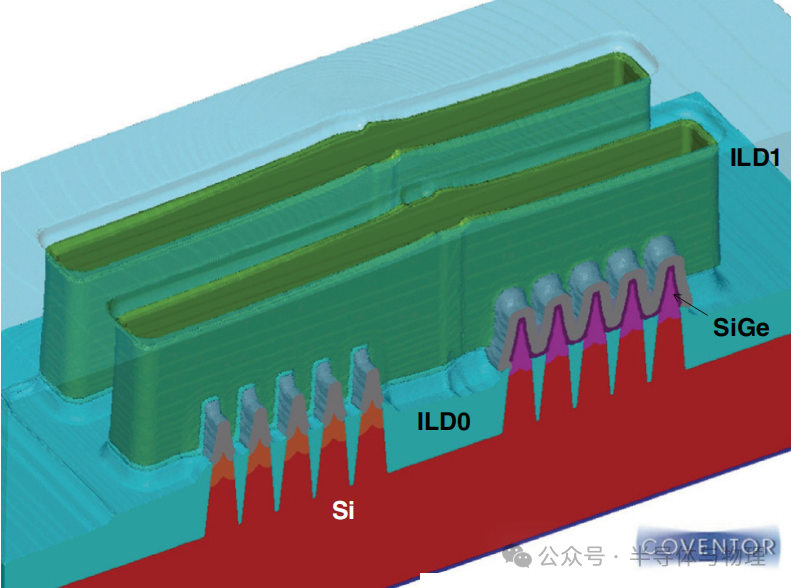

1. ILD1沉積

步驟描述:首先,在已經形成的源漏極區域上沉積一層絕緣層材料ILD1(Inter Layer Dielectric 1)。這一步驟的主要目的是為后續CMP平坦化提供一個平整的基礎,并且作為柵極和其他結構之間的絕緣層。

作用解釋:

提供平坦化基礎: 確保接下來的CMP處理能夠順利進行。

絕緣功能: 防止不同導電層之間的短路問題。

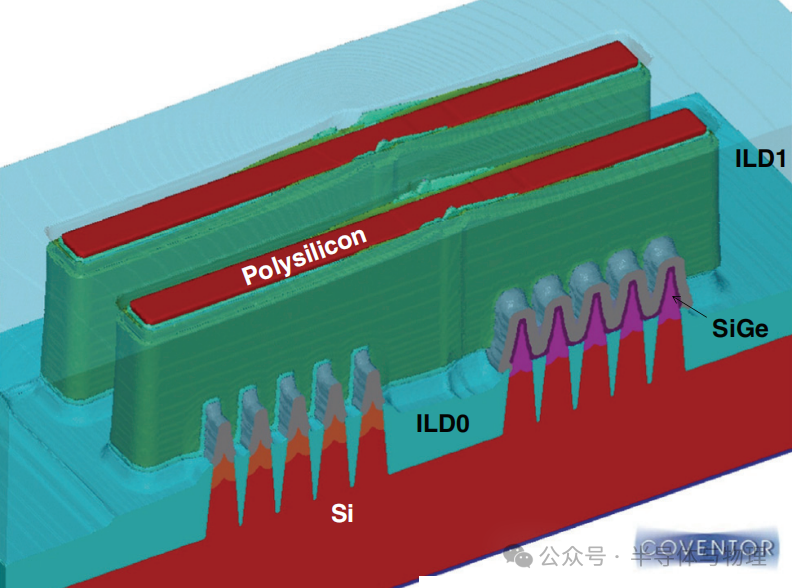

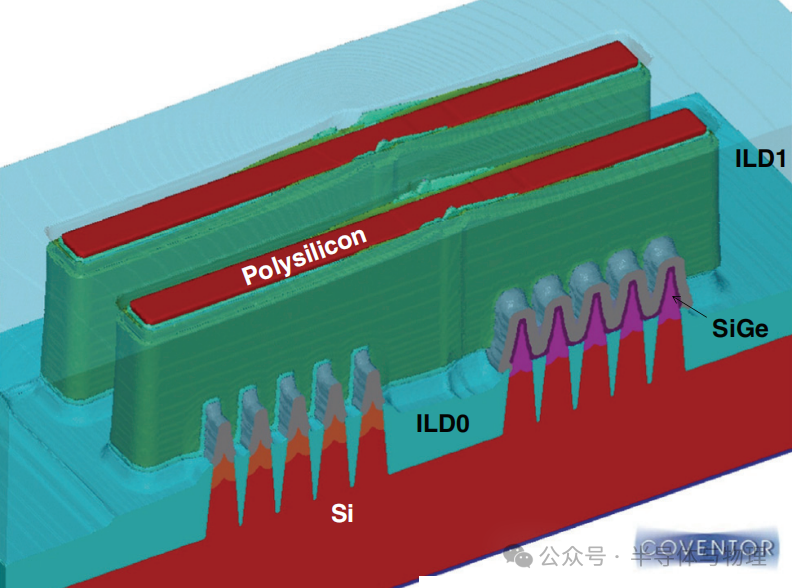

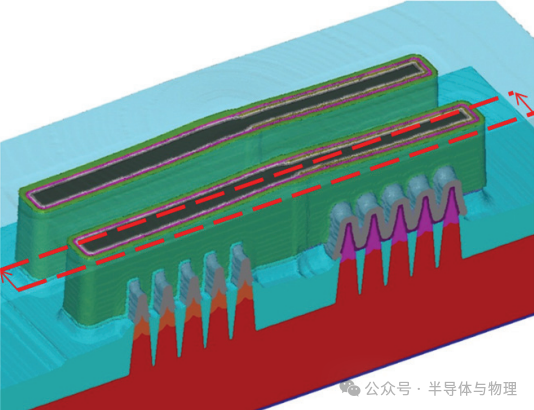

2. CMP平坦化

步驟描述:使用化學機械平坦化(Chemical Mechanical Polishing, CMP)技術去除部分ILD1,暴露出之前用作占位符的偽多晶硅柵極(dummy polysilicon gates)。

作用解釋:

暴露偽柵極: 使得后續可以準確地移除這些臨時柵極。

表面平整度: 確保后續工藝中材料沉積的一致性和均勻性。

3. 偽柵極移除與清潔

步驟描述:接下來,通過濕法蝕刻等工藝移除偽多晶硅柵極及其上的氧化層,并進行徹底清洗以保證界面干凈無污染。

作用解釋:

準備新柵極位置: 為新的HKMG結構騰出空間。

確保高質量界面: 清潔后的界面有助于提高新材料的附著質量。

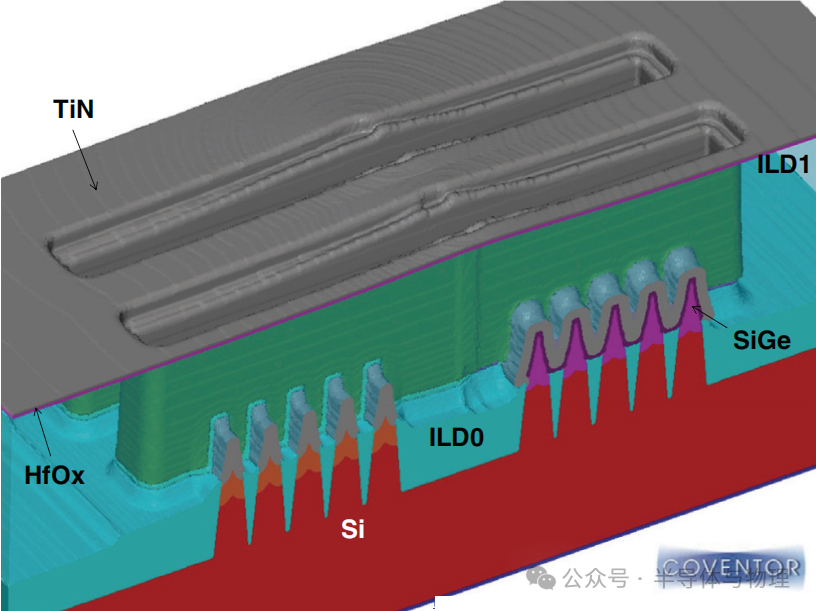

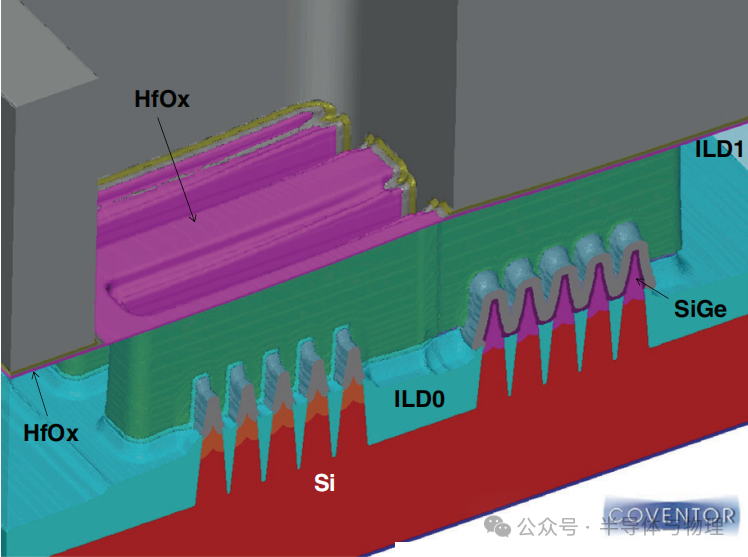

4. 高k介電材料沉積

步驟描述:采用原子層沉積(Atomic Layer Deposition, ALD)技術,在清理后的區域沉積一層鉿基高介電常數材料(如HfO2),作為新的柵極絕緣層。

作用解釋:

改善電氣性能: 減少柵極泄漏電流并提升晶體管性能。

控制閾值電壓: 高k材料的選擇對于調整晶體管的工作點至關重要。

5. 功函數金屬沉積

步驟描述:對于PMOS器件,接著會在其上沉積鈦氮化物(TiN),它將作為調整閾值電壓的工作函數金屬。隨后還會沉積鉭氮化物(TaN)作為屏障金屬,防止后續沉積的鎢擴散到高k介電層中。

作用解釋:

調節閾值電壓: TiN用于設定PMOS器件的功函數,從而影響其開啟/關閉特性。

阻擋層功能: TaN阻止其他金屬成分擴散,保護高k介電層。

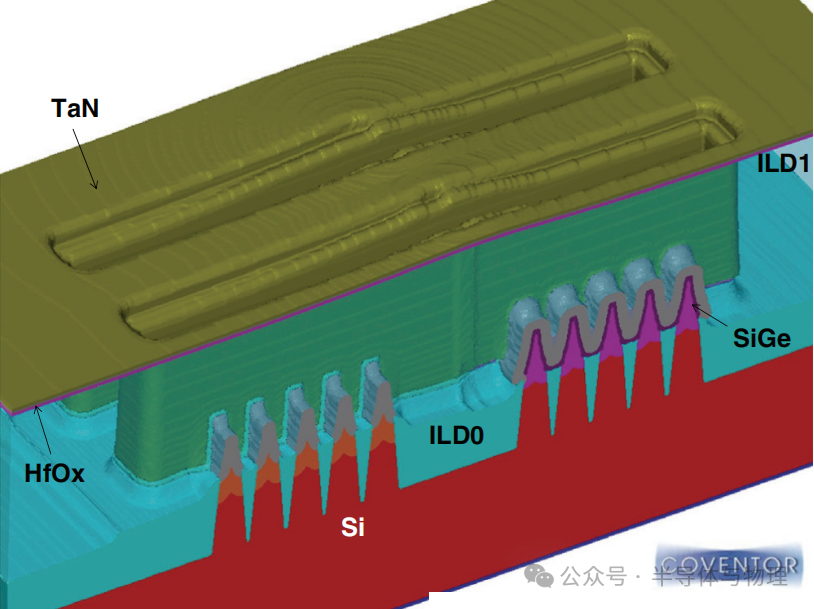

6. NMOS掩模應用與選擇性蝕刻

步驟描述:為了處理NMOS區域,需要對整個晶圓表面涂覆光刻膠,并應用NMOS掩模來保護PMOS區域,而暴露出來的NMOS區域則會被蝕刻掉TaN屏障層和TiN PMOS工作函數金屬。

作用解釋:

保護PMOS: 確保PMOS區域不受下一步蝕刻的影響。

暴露NMOS: 準備NMOS區域接受特定的工作函數金屬。

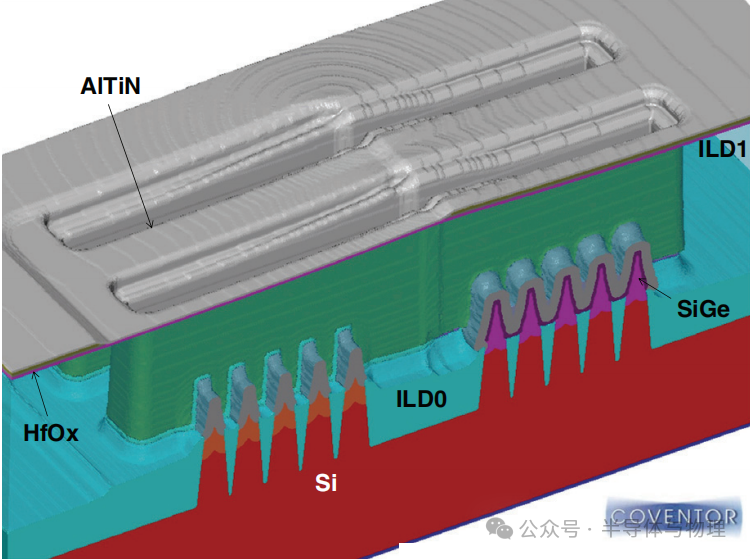

7. NMOS功函數金屬沉積

步驟描述:移除光刻膠并再次清洗晶圓后,利用ALD技術在NMOS區域沉積適合的功函數金屬,例如鈦鋁氮化物(TiAlN),用于調整NMOS器件的閾值電壓。

作用解釋:

定制NMOS閾值電壓: TiAlN等材料用于優化NMOS晶體管的性能。

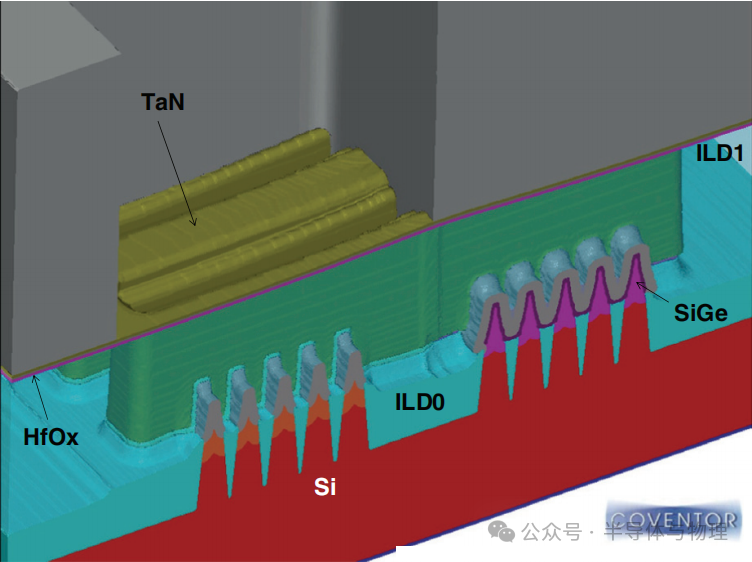

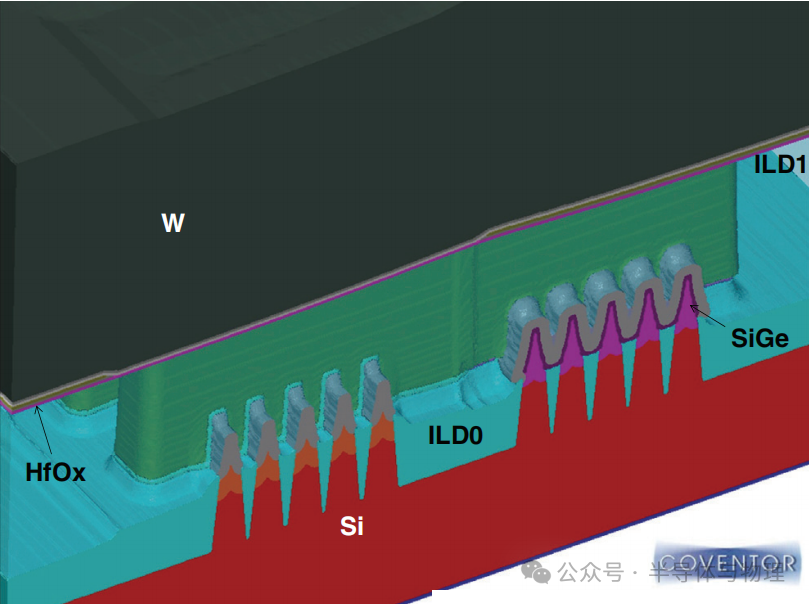

8. 粘附層沉積與WCMP填充

步驟描述:最后,沉積一層鈦氮化物(TiN)作為粘附層,然后進行鎢化學機械拋光(WCMP),以填充柵極溝槽。WCMP過程中,過量的鎢以及其他金屬層被去除,只留下位于柵極溝槽內的HKMG結構。

作用解釋:

增強粘合強度: TiN作為中間層增加了金屬與下方結構之間的結合力。

精確填充: WCMP確保了柵極溝槽被充分但不過度填充。

9. 過拋光

步驟描述:所有其他金屬層和高k介電層都會在過拋光步驟中從晶圓表面去除,只留下位于柵極溝槽內的HKMG結構。

作用解釋:

清除多余材料: 確保最終產品具有良好的電氣特性和可靠性。

表面平整: 為后續工藝提供一個平滑的工作面。

-

晶圓

+關注

關注

52文章

4956瀏覽量

128176 -

晶體管

+關注

關注

77文章

9731瀏覽量

138649 -

柵極

+關注

關注

1文章

174瀏覽量

21011 -

FinFET

+關注

關注

12文章

251瀏覽量

90287

原文標題:FinFet Process Flow-后柵HKMG形成

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

聊聊Rust與C語言交互的具體步驟

22nm技術節點的FinFET制造工藝流程

STM32WB配置SMPS模塊具體步驟是什么?

請問UCGUI中移植觸摸的具體步驟是什么?

STM32新建工程具體步驟

學電機的具體步驟

西門子V20變頻器PID控制恒壓供水的具體步驟

FinFET制造工藝的具體步驟

FinFET制造工藝的具體步驟

評論