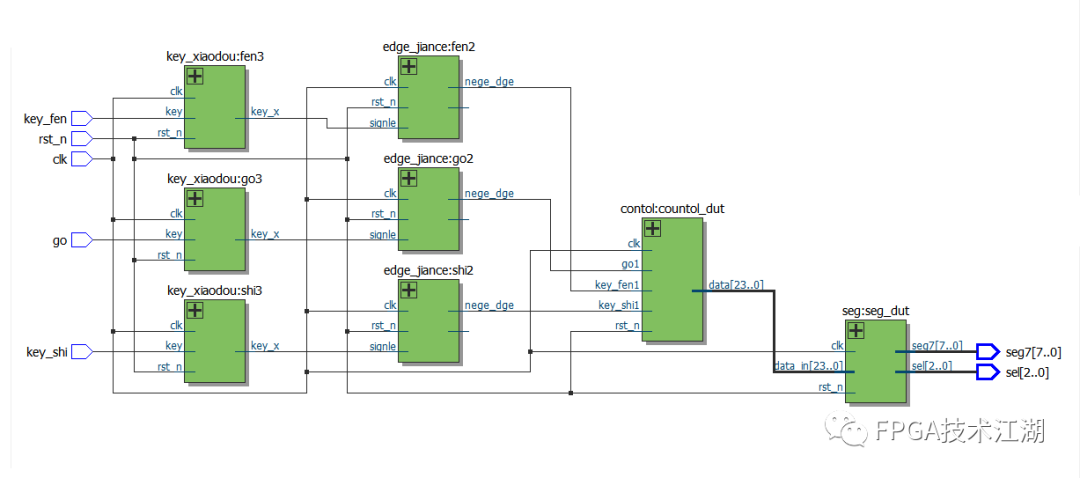

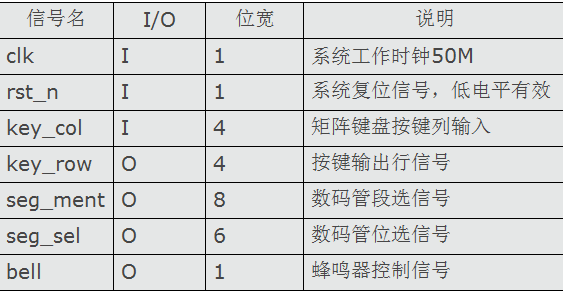

本次的設計的數字鐘思路描述如下,使用3個key按鍵,上電后,需要先配置數字時鐘的時分秒,設計一個按鍵來控制數字時鐘的時,第二個按鍵來控制數字時鐘的分,本次設計沒有用按鍵控制數字時鐘的秒,原理一樣,大家可以自己做拓展設計再使用一個按鍵控制數字時鐘的,然后用第三個按鍵來控制數字時鐘的運行。采取"Top to down"設計思想,分模塊設計,由于本次設計比較簡單,這里就沒有設計總設計框架圖,上面也大致描述了設計思路,給大家截取RTL級視圖提供參考,具體設計如下:

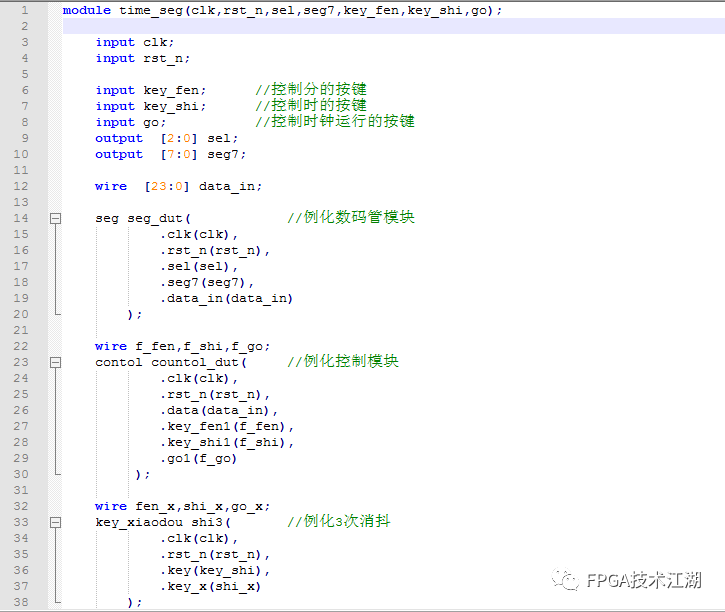

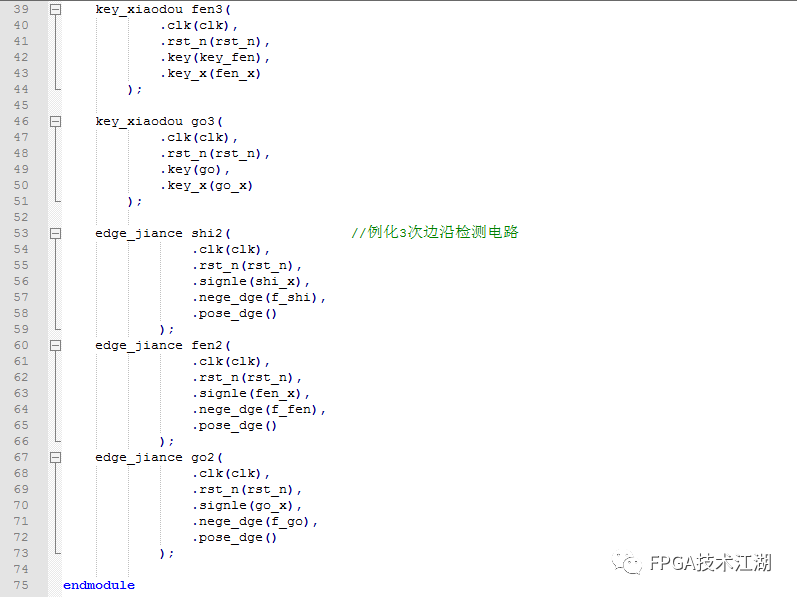

附設計代碼:(源碼文件可從公眾號內部獲取) 總模塊:

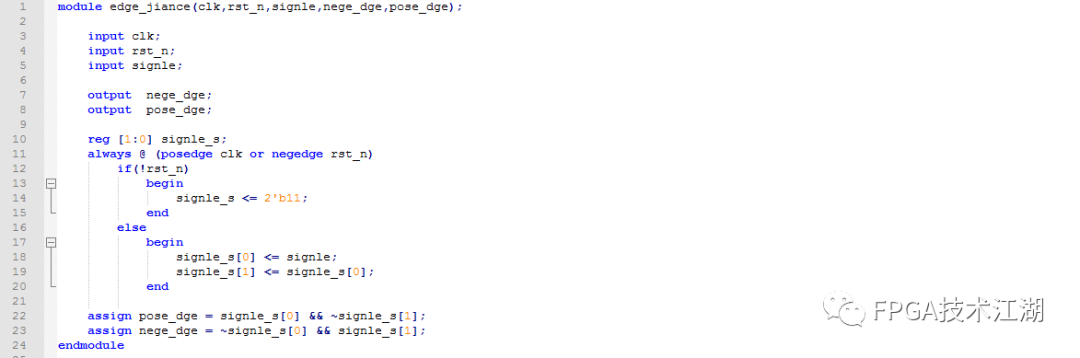

按鍵模塊:

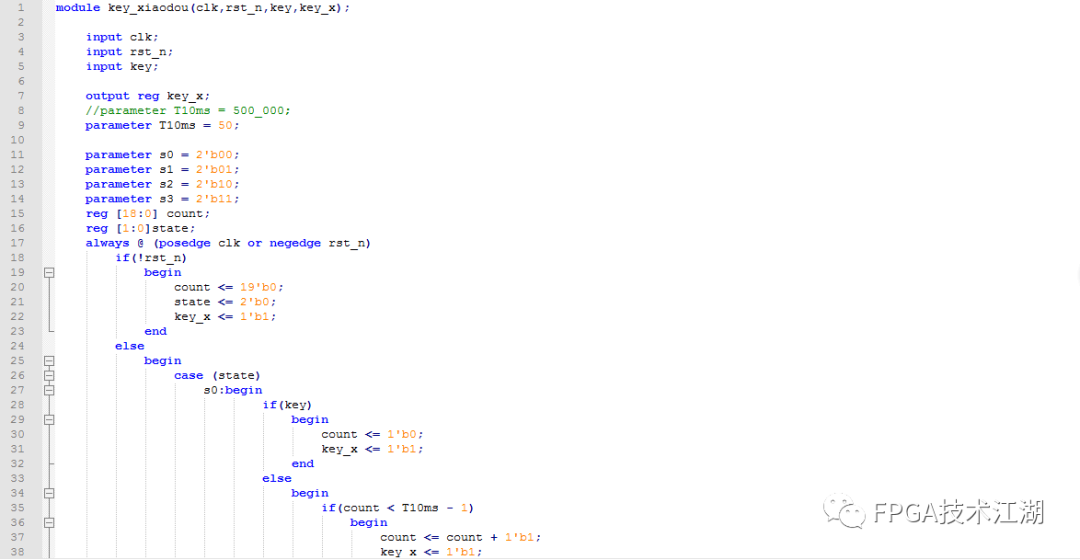

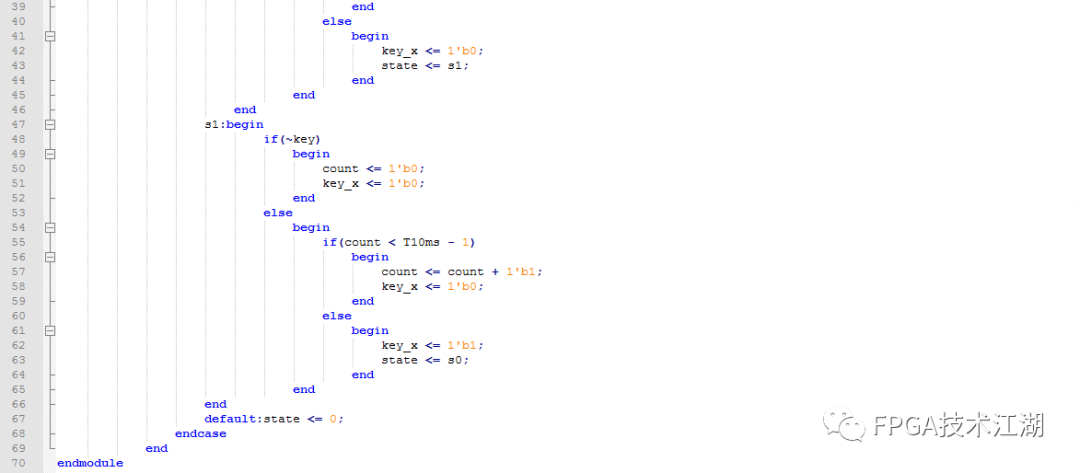

消抖模塊:

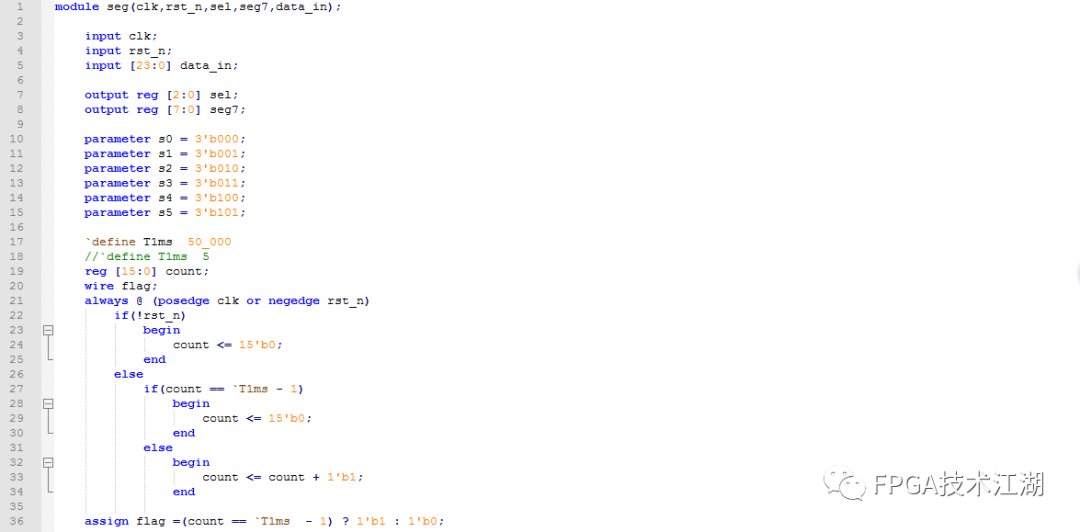

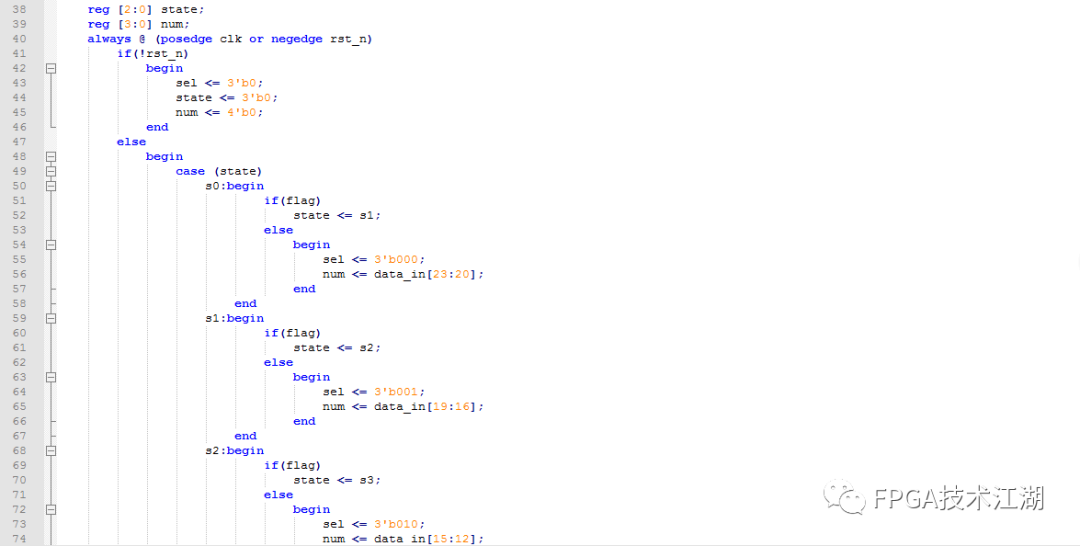

數碼管模塊:

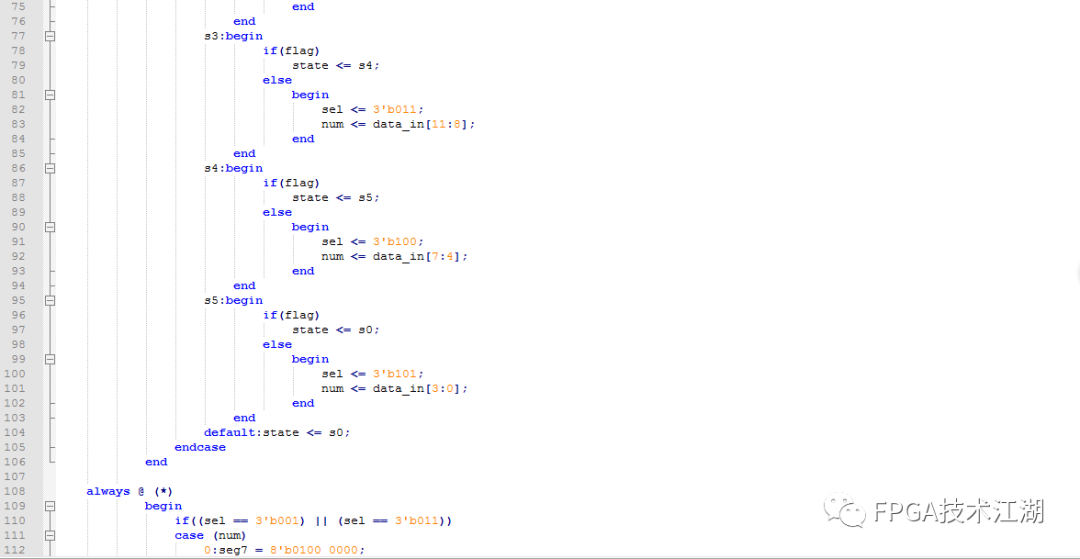

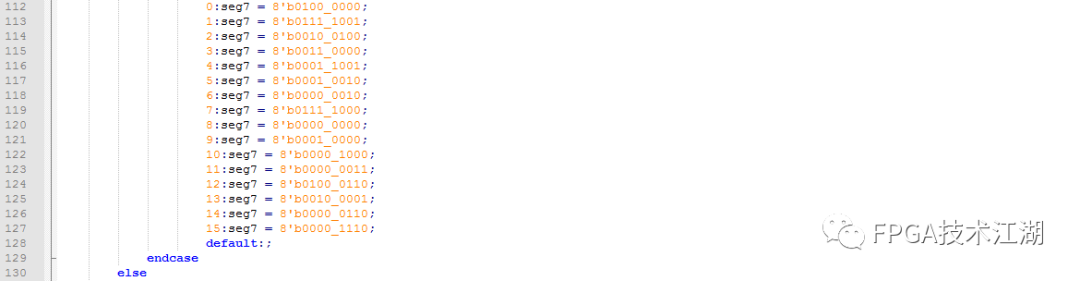

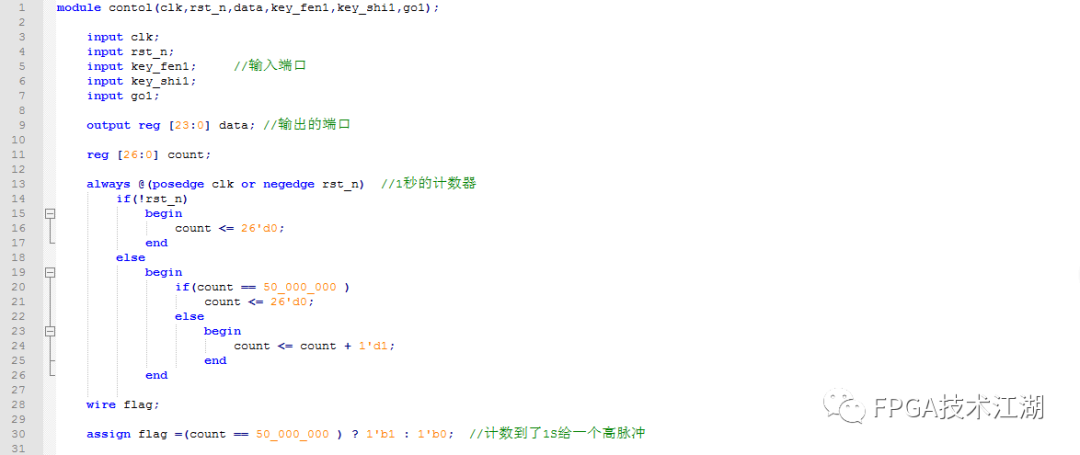

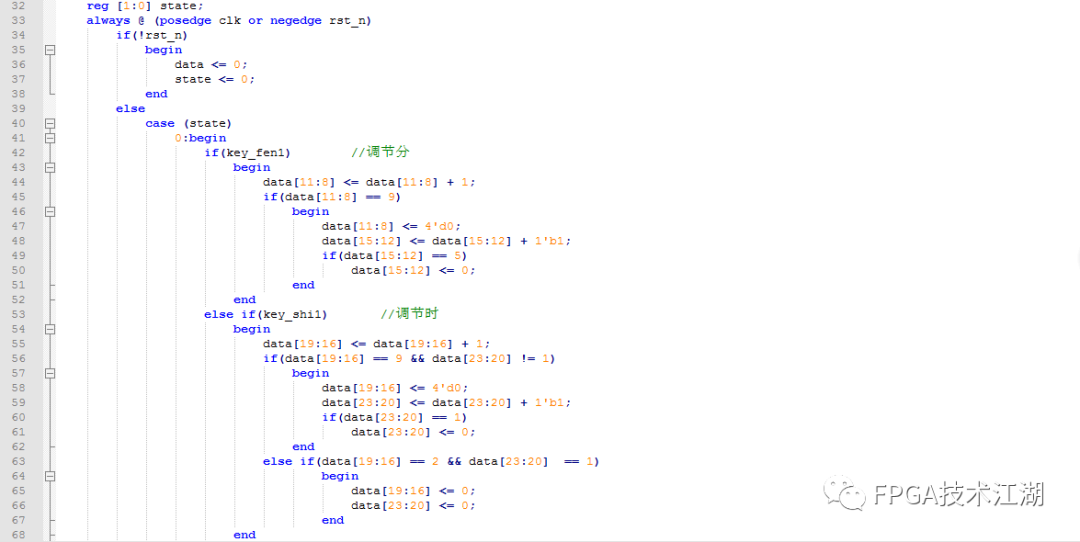

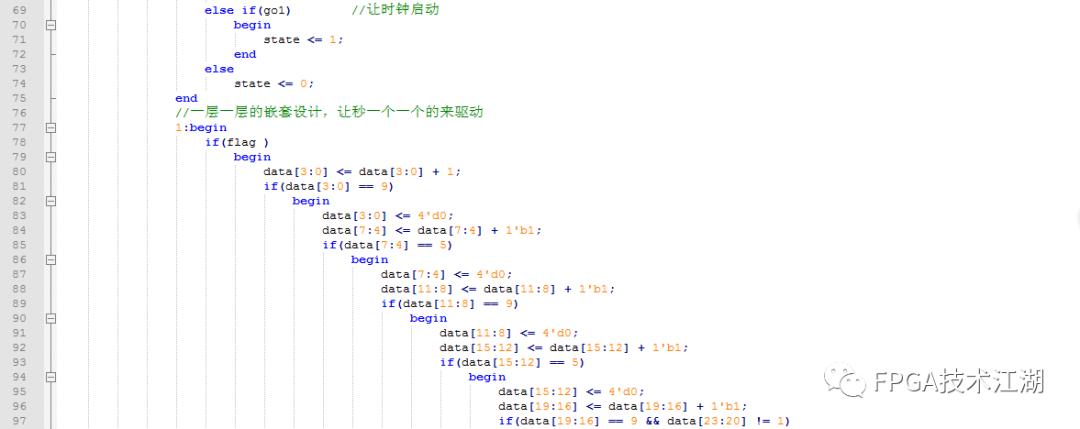

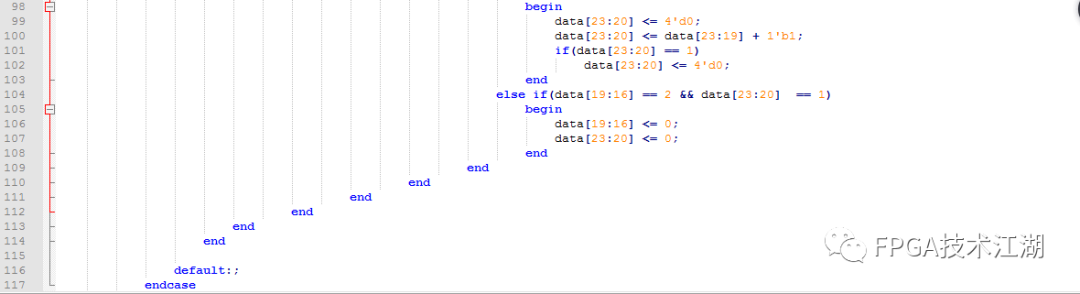

控制模塊:

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1630文章

21782瀏覽量

604980 -

代碼

+關注

關注

30文章

4816瀏覽量

68862 -

數字時鐘

+關注

關注

2文章

151瀏覽量

20408

原文標題:源碼系列:基于FPGA數字時鐘的設計(附源工程)

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

如何把握FPGA的數字時鐘管理器

,什么時候用DCM、PLL、PMCD和MMCM四大類型中的哪一種,讓他們頗為困惑。賽靈思現有的FPGA中沒有一款同時包含這四種資源(見表1)。 這四大類中的每一種都針對特定的應用。例如,數字時鐘管理器(DCM)適用于實現延遲鎖相

FPGA的數字時鐘電路解析

FPGA 在通信領域的應用可以說是無所不能,得益于 FPGA 內部結構的特點,它可以很容易地實現分布式的算法結構,這一點對于實現無線通信中的高速數字信號處理十分有利。

發表于 01-24 13:46

?856次閱讀

FPGA的外部時鐘周期性地打開和關閉

嗨,我是FPGA的新手。我想知道我是否可以有一個設計,我的FPGA的外部時鐘周期性地打開和關閉。我知道Xilinx FPGA使用數字

發表于 01-10 10:59

基于FPGA的時鐘設計

在FPGA設計中,為了成功地操作,可靠的時鐘是非常關鍵的。設計不良的時鐘在極限的溫度、電壓下將導致錯誤的行為。在設計PLD/FPGA時通常采用如下四種類型

發表于 09-21 18:38

?3765次閱讀

FPGA實現數字時鐘

在Quartus Ⅱ開發環境下,用Verilog HDL硬件描述語言設計了一個可以在FPGA芯片上實現的數字時鐘. 通過將設計代碼下載到FPGA的開發平臺Altera DE2開發板上進

發表于 11-29 16:51

?183次下載

基于FPGA的數字時鐘

發表于 12-26 10:33

?42次下載

基于fpga的數字時鐘設計應用

本工程包括矩陣鍵盤和數碼管顯示模塊,共同實現一個帶有鬧鐘功能、可以設置時間的數字時鐘。具體功能如下:1. 數碼管可以顯示時十位、時個位、分十位、分個位、秒十位、秒個位。2. 上電后,數碼管顯示000000,并開始每秒計時。

發表于 04-19 10:27

?1.6w次閱讀

基于FPGA的數字時鐘實現

EDA技術使得電子線路的設計人員能在計算機上完成電路的功能設計、邏輯設計、時序測試直至印刷電路板的自動設計。本文介紹了以 VHDL 語言和硬件電路為表達方式,以 Quartus II 軟件為設計工具,最終通過 FPGA 器件實現數字時鐘

發表于 05-25 16:28

?39次下載

基于FPGA的數字時鐘設計

基于FPGA的數字時鐘設計

評論