第一期

智多晶DDR Controller介紹

本期主要介紹智多晶DDR Controller的常見應用領域、內部結構、各模塊功能、配置界面、配置參數等內容。

01智多晶DDR Controller應用領域

1.1工控領域

在工業控制系統中,設備需要長時間穩定運行,同時對數據的實時性和準確性要求極高。智多晶DDR Controller的高可靠性和精準時序控制能力,使其成為工控領域的理想選擇。例如,在PLC(可編程邏輯控制器)中,它能夠快速響應各種傳感器信號,實時處理和存儲大量的控制數據,確保生產設備的精準控制和高效運行。此外,智多晶的SEAL 5000的SA5Z-30、SA5Z-50、SA5Z-100等FPGA器件內置了ARM核和DDR Controller,這種一體化的設計不僅提高了系統的集成度,還降低了功耗和成本。在一些復雜的工業自動化場景中,如機器人控制、智能工廠的生產調度系統等,這種FPGA內置DDR Controller的方案能夠實現軟硬件協同設計,將控制流與算法流分開處理,大幅提升運算速度和系統性能,同時兼顧了性能和成本的平衡。

1.2通信領域

隨著5G、6G等高速通信技術的發展,對數據傳輸速率和帶寬的要求越來越高。智多晶DDR Controller支持多種高速接口和高性能DDR存儲,能夠滿足通信設備對大數據量快速存儲和讀取的需求。在基站設備中,它能夠高效處理大量的信號數據,支持高速的數據緩存和傳輸,確保信號的實時處理和發送。同時,在網絡交換機、路由器等設備中,智多晶DDR Controller能夠快速調度和轉發數據包,提高網絡的吞吐量和響應速度,為用戶提供更流暢的通信體驗。

1.3消費電子領域

在手持設備等消費電子產品中,用戶對設備的性能和功耗都非常關注。智多晶DDR Controller的高效數據傳輸能力和低功耗設計,使其能夠為這些設備提供強勁的性能支持。例如,在手持設備中,它能夠快速讀取和存儲應用程序數據、高清圖片和視頻等,提升設備的運行速度和響應能力。同時,通過優化的時序控制和電源管理,有效降低了內存訪問過程中的功耗,延長了設備的續航時間,讓用戶能夠更長時間地享受各種功能。

1.4汽車電子領域

隨著汽車智能化的發展,汽車電子系統需要處理越來越多的數據,如自動駕駛輔助系統中的圖像識別、傳感器數據融合等。智多晶DDR Controller的高可靠性和實時性,能夠滿足汽車電子系統對數據處理的嚴格要求。在自動駕駛輔助系統中,它能夠快速處理來自攝像頭、雷達等傳感器的大量數據,實時生成準確的環境感知信息,為車輛的自動駕駛決策提供有力支持。

02智多晶DDR Controller介紹

智多晶的Seal 5000系列FPGA芯片,內置DDR Controller硬核。其中SA5Z-30系列中的D1_U213內嵌了128Mb的DDR2顆粒、D2_U256內嵌了512Mb的DDR2顆粒、D3_U256內嵌了1Gb的DDR3顆粒;這對用戶來說,不但降低了設計的難度,也有助于降低系統功耗,有利于提升產品競爭力。SA5Z-30系列(D0_U324)、SA5Z-50系列、SA5T-100系列、SA5T-366系列,可以外掛DDR3顆粒,其中SA5T-366系列還支持外掛DDR4顆粒。

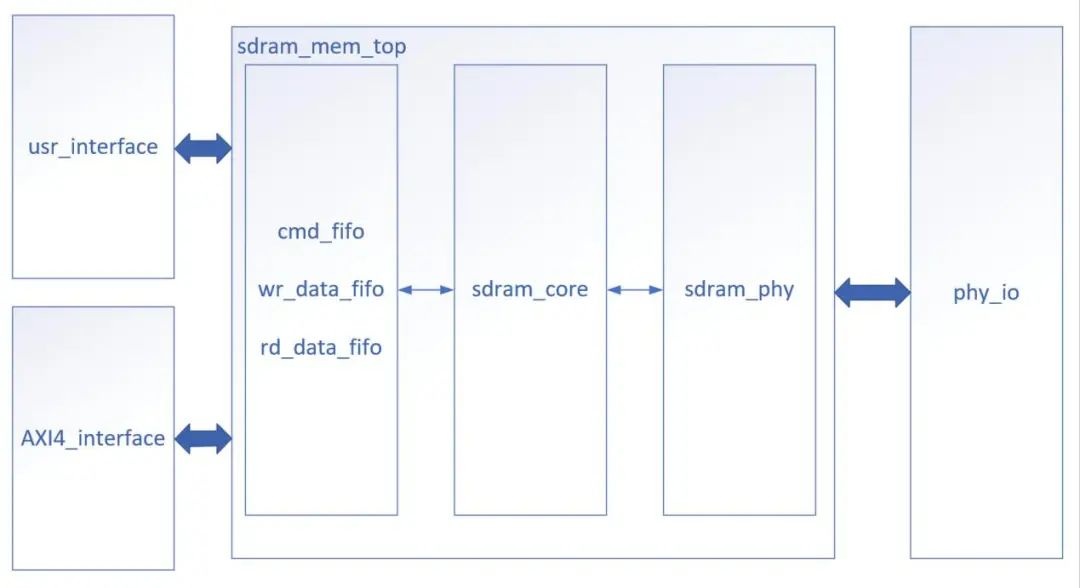

2.1 DDR Controller結構框圖

DDR Controller結構框圖,如圖一所示,其中user_interface模塊為DDR2/3 Controller的用戶接口部分,由軟邏輯實現;sdram_mem_top模塊DDR2/3 Controller的核心控制部分,由硬核實現;phy_io模塊是DDR2/3 Controller的模擬電路部分,由軟邏輯和原語實現。

圖一 DDR Controller結構框圖

2.1.1各模塊功能簡述

user_interface模塊,采用類似于AXI-Stream總線的方式,通過ready、valid和last信號握手方式,實現命令和讀寫數據的控制。

AXI4_interface模塊(目前僅支持SA5T-100系列),采用標準的AXI4接口。

sdram_mem_top模塊包含:interface_fifo模塊、sdram_core模塊和sdram_phy模塊。sdram_phy模塊中包含Initialization Logic、Read Training Logic和Write Leveling Logic等子模塊。

phy_io模塊,在SA5Z-30器件DDR Controller使用ODDRx2/IDDRx2,其余器件DDR Controller使用ODDRx4/IDDRx4。

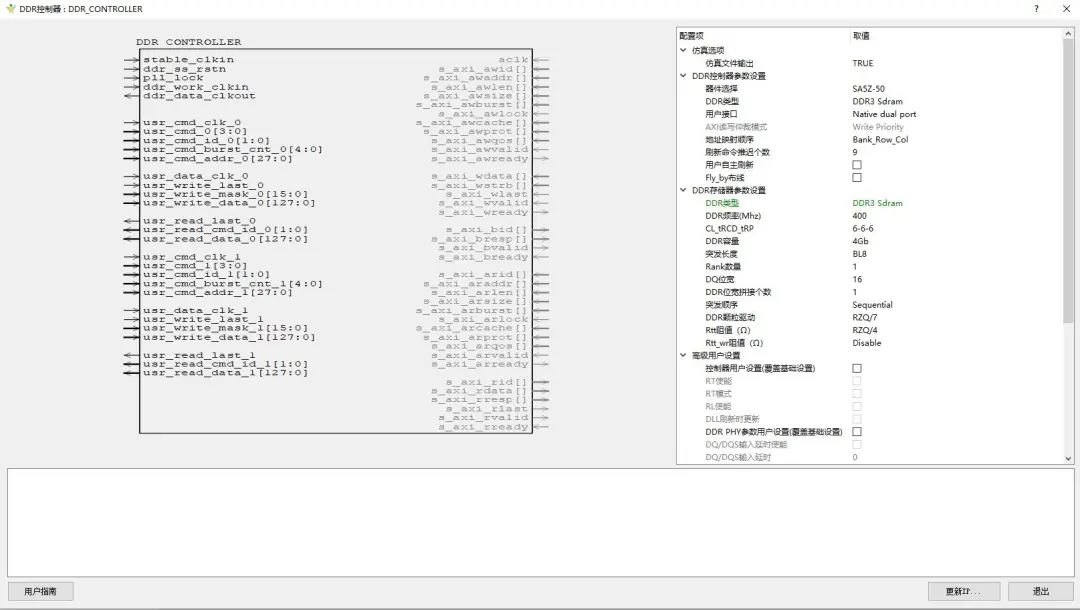

2.2 DDR Controller配置界面

圖二為智多晶DDR Controller的配置界面,可以看到包含一些必須的配置參數,方便客戶根據自己的硬件設計,靈活地配置;下面會對其配置參數做詳細的介紹。

圖二 DDR Controller配置界面

2.3 DDR Controller配置界面參數含義

2.3.1 器件選擇

根據設計中使用的芯片,可以選擇為SA5Z-30、SA5Z-50、SA5T-100、SA5T-336。

2.3.2 DDR 類型

DDR 類型,可以選擇為 DDR2 Sdram 或 DDR3 Sdram。SA5Z-30-D1-U213和 SA5Z-30-D2-U256為合封DDR2,SA5Z-30-D3-U256為合封DDR3;其余芯片需要外掛DDR顆粒。

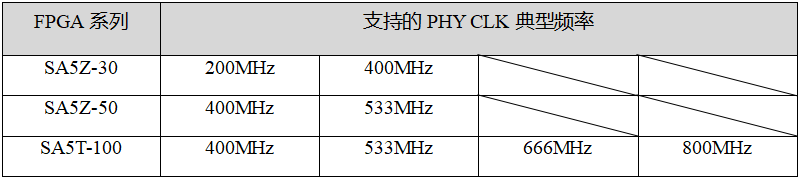

2.3.3 DDR 頻率

不同型號的FPGA器件,DDR Controller支持的頻率范圍不一樣。用戶只能在限定的頻率范圍內選擇合適的頻率值(表中未包含的更低的頻率,器件也可支持,參數的選擇可以咨詢FAE)。

2.3.4CL-tRCD-tRP

DDR 的第一時序參數,會根據用戶選擇的“DDR 類型”以及輸入的“DDR 頻率”自 動生成相應的時序參數供用戶選擇。單位為一個PHY CLK時鐘周期。

2.3.5DDR 容量

在選擇 DDR 類型后,會自動生成可支持的 DDR 容量大小。不同的 DDR 容量與 DQ 位寬相關,會影響 BANK、ROW、COL 的寬度。

2.3.6 突發長度

數據傳輸的突發長度分為 BL4和 BL8。只有 SA5Z-30 系列器件支持 BL4和 BL8 選項,其余系列器件只支持 BL8 選項。

2.3.7 Rank 數量

選擇使用rank的數量,最大支持2個rank(SA5Z-30 僅支持單rank)。

2.3.8DQ 位寬

數據傳輸通道的寬度,與DDR 位寬拼接個數共同決定單個時鐘周期的數據傳輸量。有 8 通道器件和 16 通道器件兩個選項,不同 DQ 位寬與 DDR 容量共同影響 ROW、BANK、COL 的寬度。

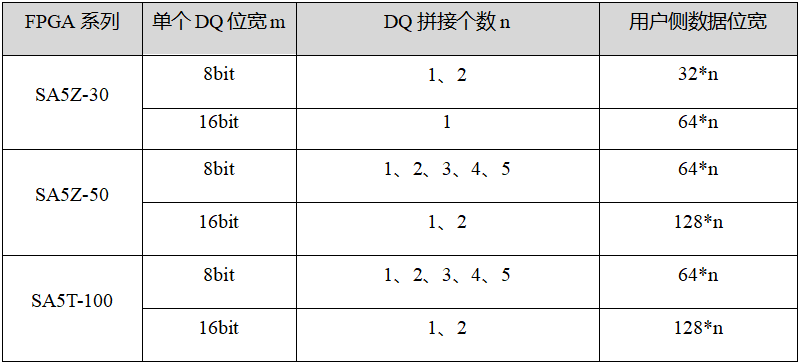

2.3.9DDR 位寬拼接個數

根據硬件板卡掛載的DDR顆粒的 DQ 位寬,選擇合適的DDR位寬拼接個數。對于不同的器件可以拼接的個數不同,下表列出了可以拼接的個數和對應的用戶側數據位寬。

注:DDR Controller支持最多32bit的DQ位寬;如果不使用DDR Controller的硬核,用戶可以使用軟邏輯以支持更寬的位寬。

2.3.10突發順序

支持 Sequential 和 Interleaved 兩種突發順序。Sequential 按照連續地址順序訪問存儲單 元。Interleaved 按照協議規定的交錯模式下訪問存儲單元。

2.3.11DDR 顆粒驅動

DDR 顆粒驅動選擇。DDR2 Sdram 中可選“Full Strength”和“Reduced Strength”。相 比與 Full Strength,Reduced Strength 驅動信號的強度減弱。DDR3 Sdram 中可選擇 RZQ/7 和 RZQ/6 兩種阻值。選擇后會自動修改 MR 寄存器中的設定。

2.3.12Rtt 阻值

與WL 相關ODT 的阻抗設置,RZQ/n,RZQ = 240Ω ,n = 2、4、6、8、12。

2.3.13Rtt_wr 阻值

與寫操作相關的動態 ODT 的阻抗設置。

下一期我們將繼續講解智多晶DDR Controller使用時的注意事項,敬請關注。

-

傳感器

+關注

關注

2552文章

51362瀏覽量

755703 -

FPGA

+關注

關注

1630文章

21791瀏覽量

605095 -

DDR

+關注

關注

11文章

714瀏覽量

65440 -

交換機

+關注

關注

21文章

2656瀏覽量

99964

原文標題:“芯”技術分享 | 智多晶DDR Controller介紹第一期

文章出處:【微信號:智多晶,微信公眾號:智多晶】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

智多晶DDR Controller介紹

智多晶DDR Controller介紹

評論