為高頻交易(High Frequency Trading,HFT)公司開(kāi)發(fā)硬件一直是 FPGA 工程師最熱門(mén)的職位之一。由于該行業(yè)提供的高薪,甚至可以被稱(chēng)為該領(lǐng)域許多人的“夢(mèng)想職業(yè)”。本文根據(jù)自己和其他人的親身經(jīng)歷,寫(xiě)了一篇關(guān)于測(cè)試職位是什么樣子以及如何準(zhǔn)備面試的文章。

HFT 世界是什么樣的

為了理解這些術(shù)語(yǔ)并以更合適的方式做好準(zhǔn)備,我們首先來(lái)談?wù)?HFT 是什么,以及為什么 FPGA 在交易行業(yè)中占有一席之地。

高頻交易是算法交易(https://www.investopedia.com/articles/active-trading/101014/basics-algorithmic-trading-concepts-and-examples.asp)的一種變體,算法交易本身是自動(dòng)日間交易的一種變體,從根本上講,是由算法而不是人來(lái)下訂單。人編寫(xiě)和監(jiān)控算法,但不手動(dòng)下交易。在 HFT 中,所有這些都被推向極致,利用可能只持續(xù)幾毫秒的機(jī)會(huì),通常是套利機(jī)會(huì)。為了有效地利用這樣的機(jī)會(huì)并賺錢(qián),人們需要在極短的時(shí)間內(nèi)消化市場(chǎng)數(shù)據(jù)、做出決策并下大量訂單。這就是比賽的開(kāi)始。

在那本令人驚嘆的書(shū)《Trading at the speed of Light,光速交易》中,唐納德·麥肯齊解釋了即使在芝加哥場(chǎng)內(nèi)交易的日子里,人們也通過(guò)創(chuàng)建系統(tǒng)來(lái)適應(yīng)環(huán)境,使某些人的交易速度比其他人快得多。本質(zhì)上,設(shè)計(jì)交易是一個(gè)可以利用信息不對(duì)稱(chēng)的游戲,如果此時(shí)你有一些信息尚未傳達(dá)給其他人,那么就存在一種不對(duì)稱(chēng),你可以預(yù)測(cè)其他人在獲得這些信息后會(huì)做什么,并據(jù)此做出決定。這種不對(duì)稱(chēng)是套利機(jī)會(huì)和許多其他可以賺錢(qián)的復(fù)雜場(chǎng)景的基礎(chǔ)。由于交易所本身所使用的技術(shù)的重大進(jìn)步,這些不對(duì)稱(chēng)的機(jī)會(huì)已經(jīng)變得極為罕見(jiàn)且短暫。

然而,事實(shí)是,僅僅因?yàn)殡x交易所較近的人比離交易所較遠(yuǎn)的人獲取數(shù)據(jù)的速度更快,也就無(wú)法消除這種不對(duì)稱(chēng)現(xiàn)象。那些能夠更快傳輸數(shù)據(jù)的人也是如此(微波塔、租用光纖線路)。同樣,那些能夠在收到數(shù)據(jù)后做出更快決策的人也可以在這場(chǎng)競(jìng)爭(zhēng)中領(lǐng)先。這正是 HFT 公司聘請(qǐng) FPGA 工程師來(lái)幫助解決的問(wèn)題。

交易所允許公司在附近的特定建筑物中設(shè)置計(jì)算機(jī)。無(wú)論與哪個(gè)股票經(jīng)紀(jì)人交易,那里可能都有一臺(tái)機(jī)器。這稱(chēng)為主機(jī)托管。交易所確保從這些機(jī)器到交易所計(jì)算機(jī)的光纖長(zhǎng)度對(duì)于主機(jī)托管中的每個(gè)參與者來(lái)說(shuō)都是完全相同的。

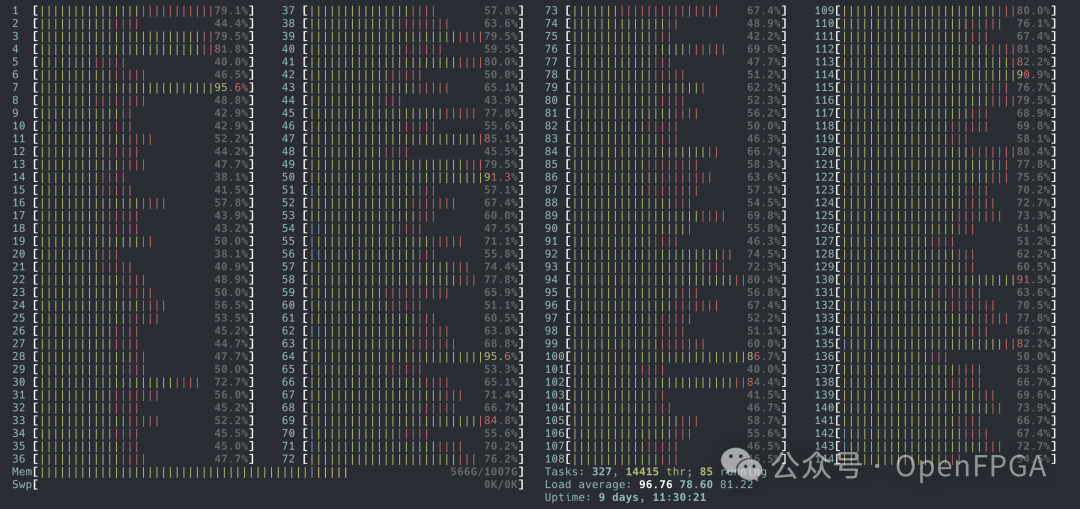

在這種情況下,再靠近交易所的空間已經(jīng)不大了。不過(guò),我們可以做的是盡量減少消化數(shù)據(jù)和發(fā)出訂單所需的時(shí)間。為了實(shí)現(xiàn)這一點(diǎn),這些服務(wù)器在處理速度、內(nèi)存速度和延遲方面都擁有極高的規(guī)格。它們被超頻并優(yōu)化到了它們所能提供的極限。

盡管進(jìn)行了這些優(yōu)化,但 CPU 從根本上來(lái)說(shuō)仍存在兩個(gè)對(duì) HFT 不太友好的”怪癖“。

更高的執(zhí)行延遲

CPU 需要將算法分解為 ISA 并按順序執(zhí)行,盡管速度可能很快,由于關(guān)鍵路徑中有幾個(gè)交互元素,在處理交互元素的過(guò)程會(huì)產(chǎn)生很大的開(kāi)銷(xiāo)。

不確定的執(zhí)行延遲

交易算法并不是 CPU 上運(yùn)行的唯一程序。操作系統(tǒng)同時(shí)管理著許多進(jìn)程和線程。這可能導(dǎo)致同一程序在不同執(zhí)行中花費(fèi)的時(shí)間不同。對(duì)于那些押注大量資金并保證該過(guò)程將花費(fèi)一定時(shí)間的人來(lái)說(shuō),這可能是一個(gè)巨大的問(wèn)題。如果只是這一次花費(fèi)的時(shí)間長(zhǎng),就可能意味著巨額損失。

FPGA 如何提供幫助

FPGA 可幫助解決上述兩個(gè)主要問(wèn)題。它們能解決不確定性問(wèn)題。可以預(yù)先知道某種操作在 FPGA 中需要多少個(gè)時(shí)鐘周期,并確保在整個(gè)操作過(guò)程中它不會(huì)發(fā)生變化。

FPGA 還經(jīng)常(并非總是)幫助解決高處理延遲的問(wèn)題。在解碼市場(chǎng)數(shù)據(jù) -> 做出決策 -> 發(fā)送訂單的整個(gè)流程中,多個(gè)子功能可以使用基于 FPGA 的加速。

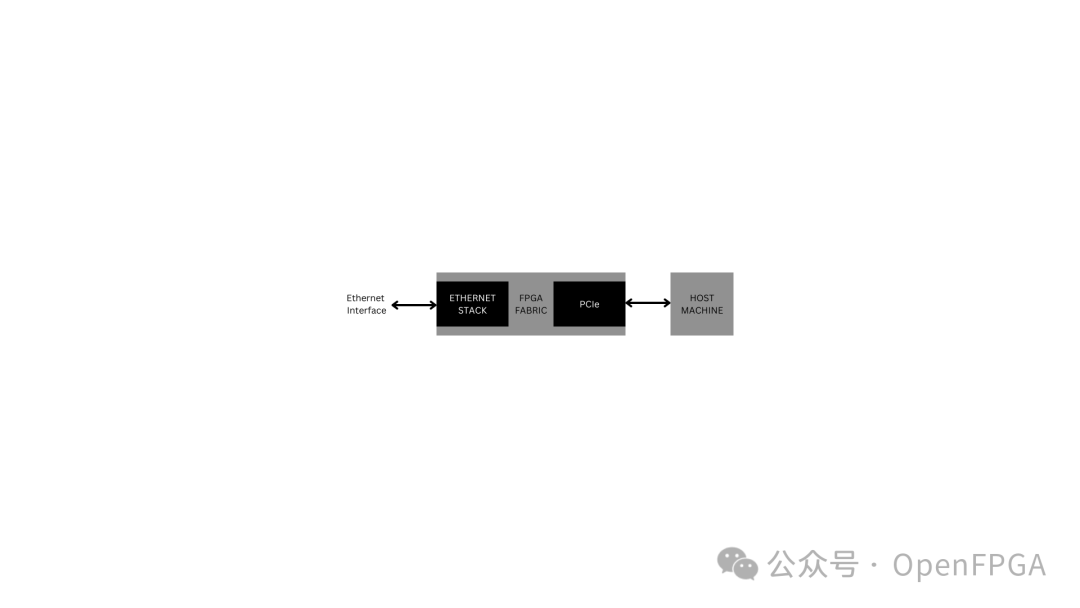

FPGA 不能很好地處理復(fù)雜的數(shù)學(xué)運(yùn)算,因此工程師們仔細(xì)分析了它們的處理管道,并找出了實(shí)現(xiàn)選擇性過(guò)程大幅加速的方法。以下是與 FPGA 連接的交易機(jī)的處理流程:

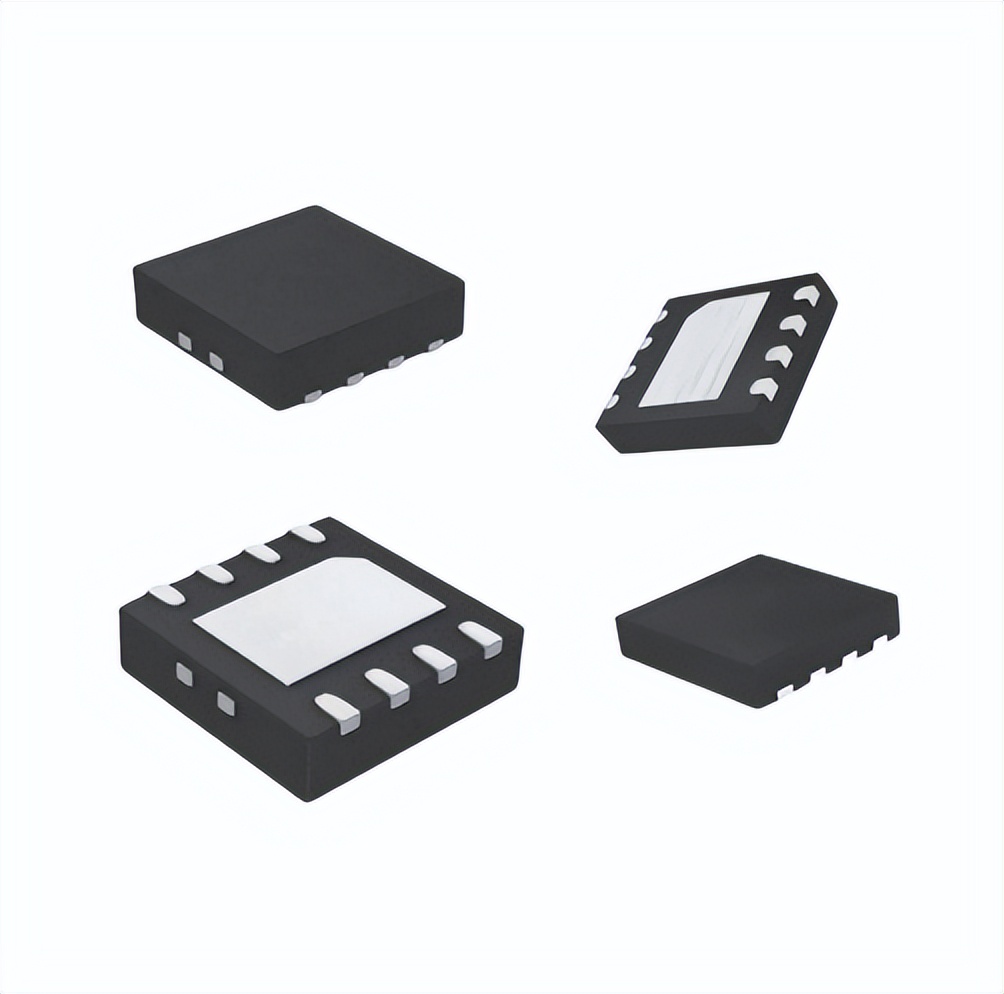

截至今天,市場(chǎng)上有許多流行的開(kāi)發(fā)板,通過(guò)處理諸如以太網(wǎng)和 PCIe 之類(lèi)的一些棘手的模塊,為 HFT 相關(guān)的 FPGA 開(kāi)發(fā)提供工作臺(tái)。

面試準(zhǔn)備

現(xiàn)在,對(duì)HFT世界有了一個(gè)很好的印象,我希望對(duì)使用這些尖端工具的興趣會(huì)越來(lái)越濃厚。讓我們來(lái)談?wù)勛鳛?HFT FPGA 工程師在日常工作中需要具備的技能。

數(shù)字電路和 RTL 設(shè)計(jì)

精通數(shù)字邏輯、Verilog 和微架構(gòu)開(kāi)發(fā)。

這些是基礎(chǔ)。應(yīng)聘者需要具備編寫(xiě) RTL、調(diào)試和在板上部署 RTL 的經(jīng)驗(yàn)。面試通常要求應(yīng)聘者當(dāng)場(chǎng)編寫(xiě) RTL。

問(wèn)題陳述也可能相當(dāng)復(fù)雜和令人費(fèi)解,與傳統(tǒng)的 FPGA 工作(例如網(wǎng)絡(luò)或國(guó)防工業(yè))不同。這既考驗(yàn)應(yīng)聘者的智商,也考驗(yàn)應(yīng)聘者的 RTL 技能。

公司非常重視編寫(xiě)花費(fèi)更少時(shí)間來(lái)完成某項(xiàng)任務(wù)的代碼,這通常需要集思廣益,想出完成同一件事的不同方法,并提出一種低延遲的替代方案,同時(shí)保持足夠合理以便在限制時(shí)間內(nèi)實(shí)現(xiàn)。

狀態(tài)機(jī)編碼:狀態(tài)機(jī)是FPGA中另一個(gè)非常常見(jiàn)的模塊。

先進(jìn)先出(FIFO):FIFO 無(wú)處不在,同步、異步等各種類(lèi)型。

驗(yàn)證基礎(chǔ)知識(shí):

如前所述,F(xiàn)PGA 團(tuán)隊(duì)在 HFT 中規(guī)模很小,因此單個(gè)開(kāi)發(fā)人員必須身兼數(shù)職才能完成一個(gè)項(xiàng)目。此外,由于交易規(guī)模巨大(一次數(shù)百萬(wàn)美元),設(shè)計(jì)中的一個(gè)錯(cuò)誤就可能導(dǎo)致?lián)p失大量資金,損失金額可能相當(dāng)于幾年的年薪。

因此驗(yàn)證成為一項(xiàng)非常重要的任務(wù)。盡管 FPGA 可以多次重新編程,但風(fēng)險(xiǎn)很高,必須小心謹(jǐn)慎,確保不會(huì)出現(xiàn)任何錯(cuò)誤。

為代碼編寫(xiě)高效的測(cè)試臺(tái)和測(cè)試用例是一項(xiàng)寶貴的技能。對(duì)于經(jīng)驗(yàn)更豐富的人,了解 System Verilog 和 UVM 可能是一個(gè)加分點(diǎn)。

網(wǎng)絡(luò)基礎(chǔ)知識(shí):

工作中實(shí)際實(shí)施的項(xiàng)目通常圍繞網(wǎng)絡(luò)展開(kāi)。

傳入的市場(chǎng)數(shù)據(jù)通過(guò) TCP 通道傳輸,交易機(jī)器需要維護(hù) TCP 連接,這可能是另一個(gè)潛在加速的領(lǐng)域。

類(lèi)似地,可能需要過(guò)濾一些數(shù)據(jù),并將其打包成數(shù)據(jù)包發(fā)送到不同的地方(通常是另一個(gè)交換機(jī))。TCP 或 UDP 可用于通信的這一部分,這也是一種很好的加速方式。

掌握以太網(wǎng)協(xié)議及其細(xì)節(jié)的基本知識(shí)在競(jìng)爭(zhēng)中保持領(lǐng)先大有幫助。

以太網(wǎng)、PCIe 和網(wǎng)絡(luò)架構(gòu)(可選、高級(jí)):

許多資金雄厚的大公司自己實(shí)現(xiàn)相關(guān)的協(xié)議棧。但大多數(shù)其他公司直接使用經(jīng)過(guò)驗(yàn)證的 IP。只有少數(shù)大公司才需要以下技能。

對(duì)于以太網(wǎng),需要掌握的知識(shí)非常豐富,包括對(duì) SERDES、PHY 與 PCS 層功能、MAC 層功能以及針對(duì)特定目的的潛在優(yōu)化的理解。如果沒(méi)有在行業(yè)環(huán)境中進(jìn)行過(guò)相關(guān)實(shí)踐,很難獲得這些知識(shí)和經(jīng)驗(yàn)。

推薦下面的文章:

https://support.ixiacom.com/sites/default/files/resources/whitepaper/PCS_white_paper.pdf

PCIe 屬于同一類(lèi)別。它是另一種廣泛的協(xié)議,包含大量細(xì)節(jié)和文檔。除非初學(xué)者使用過(guò)它,否則幾乎不可能知道這些。但是,有一些宏觀概念總是好的。

同樣,F(xiàn)PGA 并不是網(wǎng)絡(luò)上唯一的機(jī)器,還有許多其他東西,如交換機(jī)、NIC、其他交易機(jī)器等,它們可以在做出決策時(shí)進(jìn)行交互操作。對(duì)網(wǎng)絡(luò)架構(gòu)有充分的了解,并且知道可以調(diào)整哪些方面以獲得那一點(diǎn)點(diǎn)延遲優(yōu)勢(shì),這可能是一個(gè)很大的優(yōu)勢(shì)。

實(shí)用技巧:

靜態(tài)時(shí)序分析(STA)

對(duì)于初學(xué)者來(lái)說(shuō),靜態(tài)時(shí)序分析是一種測(cè)試邏輯是否滿足 FPGA 時(shí)序約束和可靠功能的方法。如上所述,推薦下面的文章

https://thedatabus.io/interview_list

這一點(diǎn)非常重要。通常,由于對(duì)延遲極其敏感,HFT 應(yīng)用的 RTL 是用非常低的流水線編寫(xiě)的,可以在更少的時(shí)鐘內(nèi)完成大量工作。這顯然會(huì)導(dǎo)致綜合、布局布線工具將 LUT 放置得非常近,以改善延遲。

一旦完成并驗(yàn)證了 RTL 編碼,由于這種擁塞,工具可能無(wú)法滿足設(shè)計(jì)的 FPGA 的時(shí)序,這種情況很常見(jiàn)。這就需要對(duì) STA 有很深的了解,才能處理邏輯并重新構(gòu)建它以嘗試滿足時(shí)序。

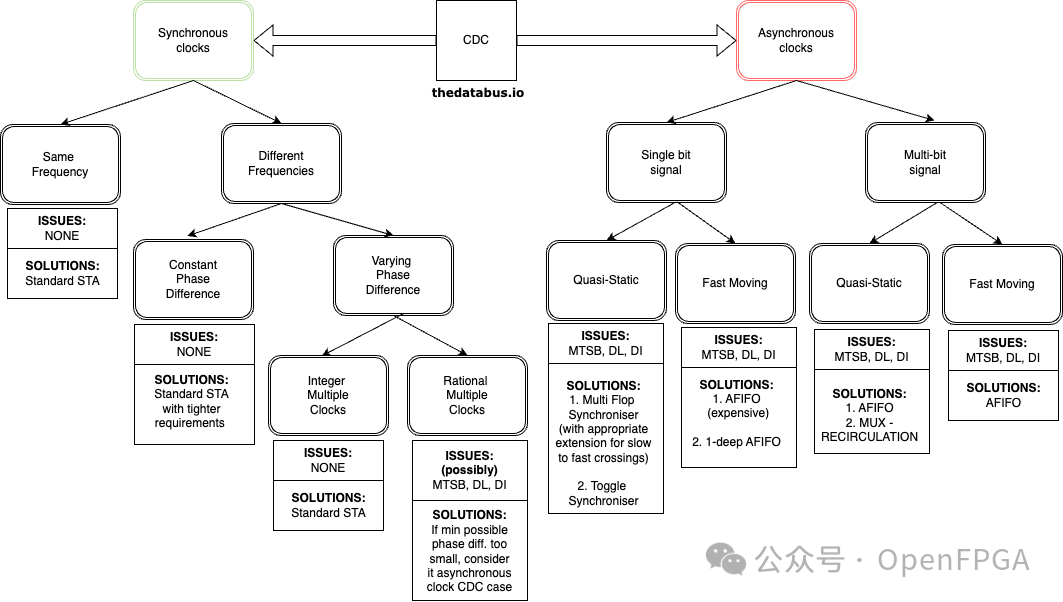

跨時(shí)鐘域 (CDC)

這是任何 RTL 設(shè)計(jì)師都需要的一項(xiàng)基本技能,無(wú)論是否需要 HFT。幾乎每個(gè)面試官在完成 STA 后都會(huì)詢問(wèn)你所了解的不同 CDC 技術(shù)。他們甚至可能會(huì)問(wèn)你為什么一種方法比另一種更好,甚至可能讓你編寫(xiě)一些代碼。

去讀一下關(guān)于 CDC 的這篇文章,或許對(duì)你有所幫助

https://thedatabus.in/cdc_complete_guide

假設(shè)使用雙觸發(fā)同步器執(zhí)行 CDC,你會(huì)為該元素向 .xdc 文件(約束文件)添加哪些約束?ASFIFO 呢?

區(qū)域優(yōu)化

這與前面提到的時(shí)序優(yōu)化密切相關(guān)。

HFT 應(yīng)用的設(shè)計(jì)通常不是很大,它們不會(huì)占據(jù) FPGA 的大部分空間,但邏輯元件彼此之間距離太近,導(dǎo)致?lián)砣l(fā)各種問(wèn)題。解決此問(wèn)題的唯一方法是準(zhǔn)確了解 RTL 推斷的內(nèi)容,以及如何對(duì)其進(jìn)行修改以減少擁塞。

通常,對(duì) FPGA 架構(gòu)及其基本元素(LUT、BRAM、DSP 等)的良好了解可以很好的做出決策。

此外,與其只是編寫(xiě) RTL 并對(duì)其進(jìn)行仿真,不如將其貫穿整個(gè)實(shí)施流程(綜合、布局和布線等),這樣可以更深入地了解 RTL 在到達(dá)硅片時(shí)最終會(huì)發(fā)生什么。下一步是嘗試以一種能夠減少資源利用率和設(shè)備區(qū)域擁塞的方式控制這種“推斷”。

硬件測(cè)試

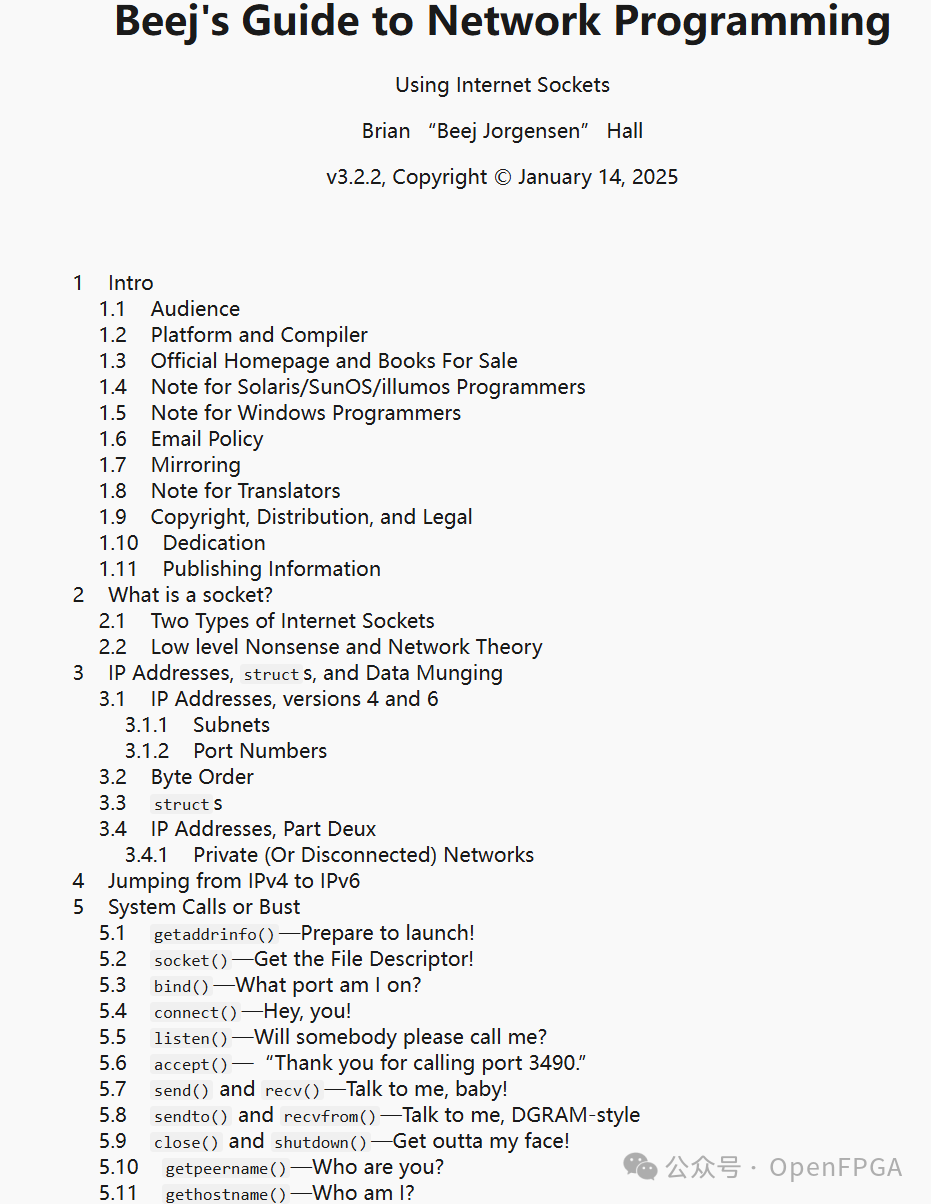

網(wǎng)絡(luò)知識(shí)

https://beej.us/guide/bgnet/html/#intro

把這本書(shū)從頭到尾讀一遍,然后嘗試在基于 Linux 的計(jì)算機(jī)上練習(xí)所有內(nèi)容。

以太網(wǎng)實(shí)踐知識(shí)

以太網(wǎng)知識(shí)是HFT工作的必需品。學(xué)會(huì)一些調(diào)試工具(如wireshark等工具)的使用。

在此過(guò)程中,還將使用許多 Linux 命令。

C++ 和驅(qū)動(dòng)程序

在任何類(lèi)型的嵌入式系統(tǒng)中,例如帶有 FPGA 的交易機(jī),都需要編寫(xiě)與硬件對(duì)話的驅(qū)動(dòng)程序。作為 FPGA 開(kāi)發(fā)人員,需要至少在一定程度上完成這項(xiàng)工作,這足以在真實(shí)硬件上測(cè)試設(shè)計(jì),并為實(shí)際軟件人員提供概念驗(yàn)證。

金融和交易知識(shí)

這不是必需的,也不會(huì)要求了解或?qū)W習(xí)這一點(diǎn)。

DSA/計(jì)算機(jī)科學(xué)技能

通常在編寫(xiě)任何代碼時(shí),為了處理數(shù)據(jù)或測(cè)試硬件,將編寫(xiě)大量軟件。編寫(xiě)良好的代碼可以大大減少使其運(yùn)行并完成手頭任務(wù)所需的時(shí)間。本著這種精神,如果面試官問(wèn)你幾個(gè)與數(shù)據(jù)結(jié)構(gòu)和算法相關(guān)的問(wèn)題,也不要感到驚訝。

總結(jié)

本文是國(guó)外的一個(gè)朋友在準(zhǔn)備相關(guān)行業(yè)面試的時(shí)候總結(jié)的一篇文章,和國(guó)內(nèi)可能會(huì)有所差異,但是可以作為參考,有從事相關(guān)行業(yè)的大佬可以在評(píng)論區(qū)聊聊從事該行業(yè)的注意點(diǎn)~

PS:前面提到的《光速交易》這本書(shū)非常有趣,即使沒(méi)有在相關(guān)行業(yè)工作,它也能讓你對(duì)這個(gè)世界有很深的了解。

-

FPGA

+關(guān)注

關(guān)注

1630文章

21794瀏覽量

605131 -

cpu

+關(guān)注

關(guān)注

68文章

10901瀏覽量

212644 -

Linux

+關(guān)注

關(guān)注

87文章

11339瀏覽量

210120

原文標(biāo)題:高頻交易中 FPGA 的作用及面試指南

文章出處:【微信號(hào):HXSLH1010101010,微信公眾號(hào):FPGA技術(shù)江湖】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

【面試題】人工智能工程師高頻面試題匯總:概率論與統(tǒng)計(jì)篇(題目+答案)

【面試題】人工智能工程師高頻面試題匯總:機(jī)器學(xué)習(xí)深化篇(題目+答案)

【面試題】人工智能工程師高頻面試題匯總:Transformer篇(題目+答案)

傅立葉變換在圖像處理中的作用

高頻旁路電容有哪些作用?國(guó)內(nèi)有哪些供應(yīng)商?

人工智能工程師高頻面試題匯總——機(jī)器學(xué)習(xí)篇

電感在高頻電路中的作用 電感在開(kāi)關(guān)電源中的應(yīng)用

2.34納秒超低時(shí)延,滿足金融市場(chǎng)高頻交易,AMD發(fā)布新一代金融加速卡

高頻功率變壓器磁芯的作用

高頻旁路電容的選擇原則

igbt在高頻電源的作用有哪些

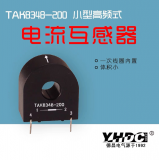

高頻電流互感器CT的作用和應(yīng)用場(chǎng)景

科普 | 一文了解FPGA

北斗衛(wèi)星同步時(shí)鐘對(duì)高頻率金融交易的應(yīng)用

一文解析高頻交易中FPGA的作用及面試建議

一文解析高頻交易中FPGA的作用及面試建議

評(píng)論