1、在verilog中有時會用signed修飾符來修飾定義的數據,運算的時候也會用$signed()任務來強制轉換數據,那么signed的修飾是為什么呢,是為了區分有符號數和無符號數的加法和乘法嗎?其實不是的,因為有符號數和無符號數據的加法強結果和乘法器結構是一樣的,signed的真正作用是決定如何對操作數擴位的問題。

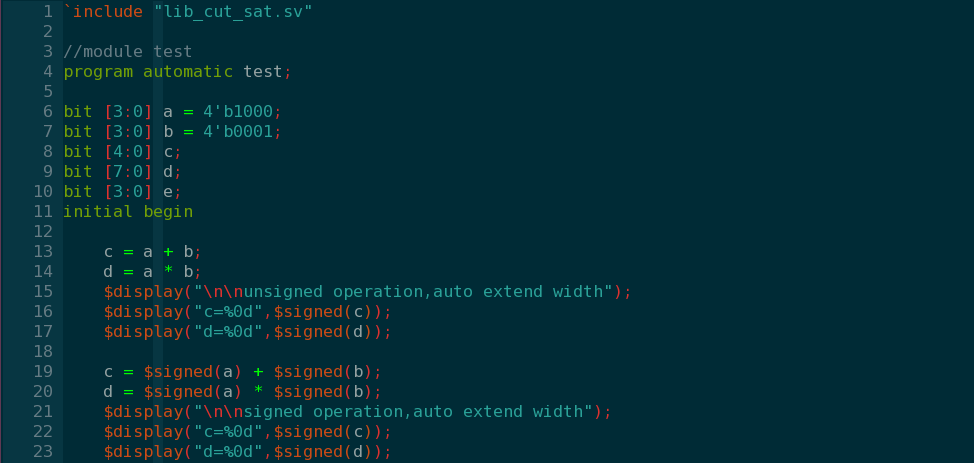

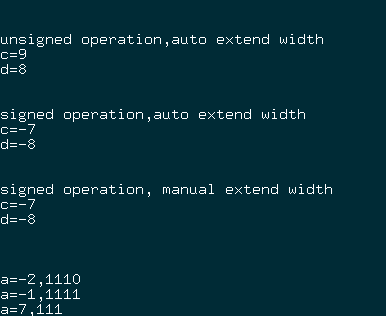

2、verilog中的加法和乘法操作前,會先對操作數據擴位成結果相同的位寬,然后進行加法或者乘法處理。比如a/b都為4位數據,c為5位數據,c = a + b,這個運算的時候會先把a和b擴位成5位,然后按照無符號加法進行相加。a/b沒有被signed修飾的時候會按照無符號數的擴位方式進行擴位,即高位補0,加法的結果當然也是a、b為無符號數相加的結果。

3、如果想把a、b作為有符號數來相加,那么就得在a/b數據定義的時候用signed修改,或者在計算的時候用$signed()來修飾,這樣在c = a + b,這個運算開始的擴位就會按照有符號數的方式進行擴位,在高位補符號位,加法得出的結果就是a、b視為有符號數的結果。當然c要視為有符號數據。

$signed()函數

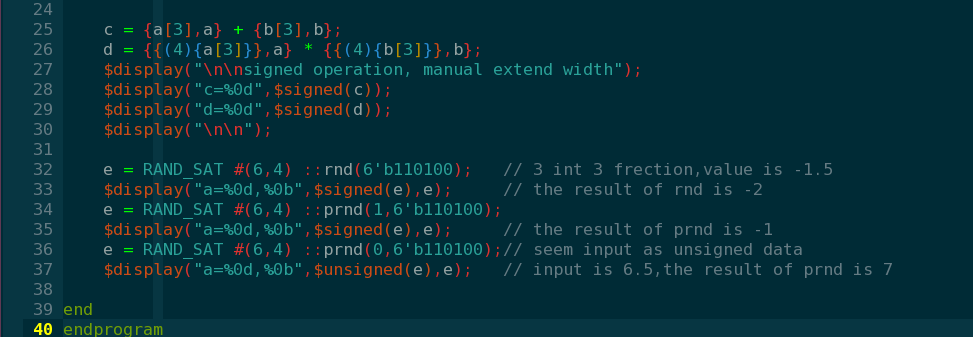

返回有符號的值,值得注意的是verilog中的負數其實是{1’b1,pos_num},而并非高級語言中的補碼。使用中最好通過增加$signed{1’b符號,正數}來實現轉換以避免錯誤。

此外在對signed wire 或signed reg 賦值時,右側的所有變量最好全部加上$signed函數轉換,以防止遺漏,造成數據錯誤

signed變量移位操作時最好使用<<<和>>>,防止對符號位進行操作,導致數據出錯

-

Verilog

+關注

關注

28文章

1355瀏覽量

110896

原文標題:Verilog 中signed和$signed()的用法

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

ADS7883的GND不連接能讀出數據,連接后讀取的數據全為0,為什么?

Verilog 電路仿真常見問題 Verilog 在芯片設計中的應用

Verilog 與 ASIC 設計的關系 Verilog 代碼優化技巧

Verilog 測試平臺設計方法 Verilog FPGA開發指南

Verilog與VHDL的比較 Verilog HDL編程技巧

Verilog硬件描述語言參考手冊

Linux lsof命令的基本用法

如何利用Verilog-A開發器件模型

Efinity編譯生成文件使用指導

評論