大學(xué)時(shí)代第一次接觸FPGA至今已有10多年的時(shí)間,至今記得當(dāng)初第一次在EDA實(shí)驗(yàn)平臺(tái)上完成數(shù)字秒表、搶答器、密碼鎖等實(shí)驗(yàn)時(shí)那個(gè)興奮勁。當(dāng)時(shí)由于沒有接觸到HDL硬件描述語言,設(shè)計(jì)都是在MAX+plus II原理圖環(huán)境下用74系列邏輯器件搭建起來的。

后來讀研究生,工作陸陸續(xù)續(xù)也用過Quartus II、FoundaTIon、ISE、Libero,并且學(xué)習(xí)了verilogHDL語言,學(xué)習(xí)的過程中也慢慢體會(huì)到verilog的妙用,原來一小段語言就能完成復(fù)雜的原理圖設(shè)計(jì),而且語言的移植性可操作性比原理圖設(shè)計(jì)強(qiáng)很多。

在學(xué)習(xí)一門技術(shù)之前我們往往從它的編程語言入手,比如學(xué)習(xí)單片機(jī)時(shí),我們往往從匯編或者C語言入門。所以不少開始接觸FPGA的開發(fā)人員,往往是從VHDL或者Verilog開始入手學(xué)習(xí)的。但我個(gè)人認(rèn)為,若能先結(jié)合《數(shù)字電路基礎(chǔ)》系統(tǒng)學(xué)習(xí)各種74系列邏輯電路,深刻理解邏輯功能,對(duì)于學(xué)習(xí)HDL語言大有裨益,往往會(huì)起到事半功倍的效果。

當(dāng)然,任何編程語言的學(xué)習(xí)都不是一朝一夕的事,經(jīng)驗(yàn)技巧的積累都是在點(diǎn)滴中完成,F(xiàn)PGA設(shè)計(jì)也無例外。下面就以我的切身體會(huì),談?wù)凢PGA設(shè)計(jì)的經(jīng)驗(yàn)技巧。

我們先談一下FPGA基本知識(shí):

1.硬件設(shè)計(jì)基本原則

FPGA(Field-Programmable Gate Array),即現(xiàn)場(chǎng)可編程門陣列,它是在PAL、GAL、CPLD等可編程器件的基礎(chǔ)上進(jìn)一步發(fā)展的產(chǎn)物。它是作為專用集成電路領(lǐng)域中的一種半定制電路而出現(xiàn)的,既解決了定制電路的不足,又克服了原有可編程器件門電路數(shù)有限的缺點(diǎn)。

速度與面積平衡和互換原則:

一個(gè)設(shè)計(jì)如果時(shí)序余量較大,所能跑的頻率遠(yuǎn)高于設(shè)計(jì)要求,能可以通過模塊復(fù)用來減少整個(gè)設(shè)計(jì)消耗的芯片面積,這就是用速度優(yōu)勢(shì)換面積的節(jié)約;

反之,如果一個(gè)設(shè)計(jì)的時(shí)序要求很高,普通方法達(dá)不到設(shè)計(jì)頻率,那么可以通過數(shù)據(jù)流串并轉(zhuǎn)換,并行復(fù)制多個(gè)操作模塊,對(duì)整個(gè)設(shè)計(jì)采用“乒乓操作”和“串并轉(zhuǎn)換”的思想進(jìn)行處理,在芯片輸出模塊處再對(duì)數(shù)據(jù)進(jìn)行“并串轉(zhuǎn)換”。從而實(shí)現(xiàn)了用面積復(fù)制換取速度的提高。

硬件原則:理解HDL本質(zhì)。

系統(tǒng)原則:整體把握。

同步設(shè)計(jì)原則:設(shè)計(jì)時(shí)序穩(wěn)定的基本原則。

2.Verilog作為一種HDL語言,對(duì)系統(tǒng)行為的建模方式是分層次的

比較重要的層次有系統(tǒng)級(jí)、算法級(jí)、寄存器傳輸級(jí)、邏輯級(jí)、門級(jí)、電路開關(guān)級(jí)。

3.實(shí)際工作中,除了描述仿真測(cè)試激勵(lì)時(shí)使用for循環(huán)語句外,極少在RTL級(jí)編碼中使用for循環(huán)

這是因?yàn)閒or循環(huán)會(huì)被綜合器展開為所有變量情況的執(zhí)行語句,每個(gè)變量獨(dú)立占用寄存器資源,不能有效的復(fù)用硬件邏輯資源,造成巨大的浪費(fèi)。一般常用case語句代替。

4. if…else…和case在嵌套描述時(shí)是有很大區(qū)別的

if…else…是有優(yōu)先級(jí)的,一般來說,第一個(gè)if的優(yōu)先級(jí)最高,最后一個(gè)else的優(yōu)先級(jí)最低。而case語句是平行語句,它是沒有優(yōu)先級(jí)的,而建立優(yōu)先級(jí)結(jié)構(gòu)需要耗費(fèi)大量的邏輯資源,所以能用case的地方就不要用if…else…語句。

補(bǔ)充:1.也可以用if…; if…; if…;描述不帶優(yōu)先級(jí)的“平行”語句。

5.FPGA一般觸發(fā)器資源比較豐富,而CPLD組合邏輯資源更豐富

6.FPGA和CPLD的組成

FPGA基本有可編程I/O單元、基本可編程邏輯單元、嵌入式塊RAM、豐富的布線資源、底層嵌入功能單元和內(nèi)嵌專用硬核等6部分組成。

CPLD的結(jié)構(gòu)相對(duì)比較簡(jiǎn)單,主要由可編程I/O單元、基本邏輯單元、布線池和其他輔助功能模塊組成。

7.Block RAM

3種塊RAM結(jié)構(gòu),M512 RAM(512bit)、M4K RAM(4Kbit)、M-RAM(64Kbit)。

M512 RAM:適合做一些小的Buffer、FIFO、DPRAM、SPRAM、ROM等;

M4K RAM: 適用于一般的需求;

M-RAM: 適合做大塊數(shù)據(jù)的緩沖區(qū)。

Xlinx 和 LatTIce FPGA的LUT可以靈活配置成小的RAM、ROM、FIFO等存儲(chǔ)結(jié)構(gòu),這種技術(shù)被稱為分布式RAM。

補(bǔ)充:但是在一般的設(shè)計(jì)中,不提倡用FPGA/CPLD的片內(nèi)資源配置成大量的存儲(chǔ)器,這是處于成本的考慮。所以盡量采用外接存儲(chǔ)器。

8.善用芯片內(nèi)部的PLL或DLL資源完成時(shí)鐘的分頻、倍頻率、移相等操作

不僅簡(jiǎn)化了設(shè)計(jì),并且能有效地提高系統(tǒng)的精度和工作穩(wěn)定性。

9.異步電路和同步時(shí)序電路的區(qū)別

異步電路:

電路核心邏輯有用組合電路實(shí)現(xiàn);

異步時(shí)序電路的最大缺點(diǎn)是容易產(chǎn)生毛刺;

不利于器件移植;

不利于靜態(tài)時(shí)序分析(STA)、驗(yàn)證設(shè)計(jì)時(shí)序性能。

同步時(shí)序電路:

電路核心邏輯是用各種觸發(fā)器實(shí)現(xiàn);

電路主要信號(hào)、輸出信號(hào)等都是在某個(gè)時(shí)鐘沿驅(qū)動(dòng)觸發(fā)器產(chǎn)生的;

同步時(shí)序電路可以很好的避免毛刺;

利于器件移植;

利于靜態(tài)時(shí)序分析(STA)、驗(yàn)證設(shè)計(jì)時(shí)序性能。

10.同步設(shè)計(jì)中,穩(wěn)定可靠的數(shù)據(jù)采樣必須遵從以下兩個(gè)基本原則:

(1)在有效時(shí)鐘沿到達(dá)前,數(shù)據(jù)輸入至少已經(jīng)穩(wěn)定了采樣寄存器的Setup時(shí)間之久,這條原則簡(jiǎn)稱滿足Setup時(shí)間原則;

(2)在有效時(shí)鐘沿到達(dá)后,數(shù)據(jù)輸入至少還將穩(wěn)定保持采樣寄存器的Hold時(shí)鐘之久,這條原則簡(jiǎn)稱滿足Hold時(shí)間原則。

11.同步時(shí)序設(shè)計(jì)注意事項(xiàng)

異步時(shí)鐘域的數(shù)據(jù)轉(zhuǎn)換。

組合邏輯電路的設(shè)計(jì)方法。

同步時(shí)序電路的時(shí)鐘設(shè)計(jì)。

同步時(shí)序電路的延遲。同步時(shí)序電路的延遲最常用的設(shè)計(jì)方法是用分頻或者倍頻的時(shí)鐘或者同步計(jì)數(shù)器完成所需的延遲,對(duì)比較大的和特殊定時(shí)要求的延時(shí),一般用高速時(shí)鐘產(chǎn)生一個(gè)計(jì)數(shù)器,根據(jù)計(jì)數(shù)產(chǎn)生延遲;對(duì)于比較小的延遲,可以用D觸發(fā)器打一下,這樣不僅可以使信號(hào)延時(shí)了一個(gè)時(shí)鐘周期,而且完成了信號(hào)與時(shí)鐘的初次同步。在輸入信號(hào)采樣和增加時(shí)序約束余量中使用。

另外,還有用行為級(jí)方法描述延遲,如“#5 a《=4’0101;”這種常用于仿真測(cè)試激勵(lì),但是在電路綜合時(shí)會(huì)被忽略,并不能起到延遲作用。

Verilog 定義的reg型,不一定綜合成寄存器。在Verilog代碼中最常用的兩種數(shù)據(jù)類型是wire和reg型,一般來說,wire型指定的數(shù)據(jù)和網(wǎng)線通過組合邏輯實(shí)現(xiàn),而reg型指定的數(shù)據(jù)不一定就是用寄存器實(shí)現(xiàn)。

12.常用設(shè)計(jì)思想與技巧

(1)乒乓操作;

(2)串并轉(zhuǎn)換;

(3)流水線操作;

(4)異步時(shí)鐘域數(shù)據(jù)同步。是指如何在兩個(gè)時(shí)鐘不同步的數(shù)據(jù)域之間可靠地進(jìn)行數(shù)據(jù)交換的問題。數(shù)據(jù)時(shí)鐘域不同步主要有兩種情況:

①兩個(gè)域的時(shí)鐘頻率相同,但是相差不固定,或者相差固定但是不可測(cè),簡(jiǎn)稱為同頻異相問題。

②兩個(gè)時(shí)鐘頻率根本不同,簡(jiǎn)稱異頻問題。

兩種不推薦的異步時(shí)鐘域操作方法:一種是通過增加Buffer或者其他門延時(shí)來調(diào)整采樣;另一種是盲目使用時(shí)鐘正負(fù)沿調(diào)整數(shù)據(jù)采樣。

13.模塊劃分基本原則

(1)對(duì)每個(gè)同步時(shí)序設(shè)計(jì)的子模塊的輸出使用寄存器(用寄存器分割同步時(shí)序模塊原則);

(2)將相關(guān)邏輯和可以復(fù)用的邏輯劃分在同一模塊內(nèi)(呼應(yīng)系統(tǒng)原則);

(3)將不同優(yōu)化目標(biāo)的邏輯分開;

(4)將送約束的邏輯歸到同一模塊;

(5)將存儲(chǔ)邏輯獨(dú)立劃分成模塊;

(6)合適的模塊規(guī)模;

(7)頂層模塊最好不進(jìn)行邏輯設(shè)計(jì)。

14.組合邏輯的注意事項(xiàng)

(1)避免組合邏輯反饋環(huán)路(容易毛刺、振蕩、時(shí)序違規(guī)等)。

解決:A.牢記任何反饋回路必須包含寄存器;B.檢查綜合、實(shí)現(xiàn)報(bào)告的warning信息,發(fā)現(xiàn)反饋回路(combinaTIonal loops)后進(jìn)行相應(yīng)修改。

(2)替換延遲鏈。

解決:用倍頻、分頻或者同步計(jì)數(shù)器完成。

(3)替換異步脈沖產(chǎn)生單元(毛刺生成器)。

解決:用同步時(shí)序設(shè)計(jì)脈沖電路。

(4)慎用鎖存器。

解決方式:

A、使用完備的if…else語句;

B、檢查設(shè)計(jì)中是否含有組合邏輯反饋環(huán)路;

C、對(duì)每個(gè)輸入條件,設(shè)計(jì)輸出操作,對(duì)case語句設(shè)置default 操作。特別是在狀態(tài)機(jī)設(shè)計(jì)中,最好有一個(gè)default的狀態(tài)轉(zhuǎn)移,而且每個(gè)狀態(tài)最好也有一個(gè)default的操作。

D、如果使用case語句時(shí),特別是在設(shè)計(jì)狀態(tài)機(jī)時(shí),盡量附加綜合約束屬性,綜合為完全條件case語句。

小技巧:仔細(xì)檢查綜合器的綜合報(bào)告,目前大多數(shù)的綜合器對(duì)所綜合出的latch都會(huì)報(bào)“warning”,通過綜合報(bào)告可以較為方便地找出無意中生成的latch。

15.時(shí)鐘設(shè)計(jì)的注意事項(xiàng)

同步時(shí)序電路推薦的時(shí)鐘設(shè)計(jì)方法:時(shí)鐘經(jīng)全局時(shí)鐘輸入引腳輸入,通過FPGA內(nèi)部專用的PLL或DLL進(jìn)行分頻/倍頻、移相等調(diào)整與運(yùn)算,然后經(jīng)FPGA內(nèi)部全局時(shí)鐘布線資源驅(qū)動(dòng)到達(dá)芯片內(nèi)所有寄存器和其他模塊的時(shí)鐘輸入端。

FPGA設(shè)計(jì)者的5項(xiàng)基本功:仿真、綜合、時(shí)序分析、調(diào)試、驗(yàn)證。

對(duì)于FPGA設(shè)計(jì)者來說,練好這5項(xiàng)基本功,與用好相應(yīng)的EDA工具是同一過程,對(duì)應(yīng)關(guān)系如下:

1. 仿真:Modelsim, Quartus II(Simulator Tool)

2. 綜合:Quartus II (Compiler Tool, RTL Viewer, Technology Map Viewer, Chip Planner)

3. 時(shí)序:Quartus II (TImeQuest Timing Analyzer, Technology Map Viewer, Chip Planner)

4. 調(diào)試:Quartus II (SignalTap II Logic Analyzer, Virtual JTAG, Assignment Editor)

5. 驗(yàn)證:Modelsim, Quartus II(Test Bench Template Writer)

掌握HDL語言雖然不是FPGA設(shè)計(jì)的全部,但是HDL語言對(duì)FPGA設(shè)計(jì)的影響貫穿于整個(gè)FPGA設(shè)計(jì)流程中,與FPGA設(shè)計(jì)的5項(xiàng)基本功是相輔相成的。

對(duì)于FPGA設(shè)計(jì)者來說,用好“HDL語言的可綜合子集”可以完成FPGA設(shè)計(jì)50%的工作——設(shè)計(jì)編碼。

練好仿真、綜合、時(shí)序分析這3項(xiàng)基本功,對(duì)于學(xué)習(xí)“HDL語言的可綜合子集”有如下幫助:

通過仿真,可以觀察HDL語言在FPGA中的邏輯行為。

通過綜合,可以觀察HDL語言在FPGA中的物理實(shí)現(xiàn)形式。

通過時(shí)序分析,可以分析HDL語言在FPGA中的物理實(shí)現(xiàn)特性。

對(duì)于FPGA設(shè)計(jì)者來說,用好“HDL語言的驗(yàn)證子集”,可以完成FPGA設(shè)計(jì)另外50%的工作——調(diào)試驗(yàn)證。

1.搭建驗(yàn)證環(huán)境,通過仿真的手段可以檢驗(yàn)FPGA設(shè)計(jì)的正確性。

2.全面的仿真驗(yàn)證可以減少FPGA硬件調(diào)試的工作量。

3.把硬件調(diào)試與仿真驗(yàn)證方法結(jié)合起來,用調(diào)試解決仿真未驗(yàn)證的問題,用仿真保證已經(jīng)解決的問題不在調(diào)試中再現(xiàn),可以建立一個(gè)回歸驗(yàn)證流程,有助于FPGA設(shè)計(jì)項(xiàng)目的維護(hù)。

FPGA 設(shè)計(jì)者的這5項(xiàng)基本功不是孤立的,必須結(jié)合使用,才能完成一個(gè)完整的FPGA設(shè)計(jì)流程。反過來說,通過完成一個(gè)完整的設(shè)計(jì)流程,才能最有效地練習(xí)這5項(xiàng)基本功。對(duì)這5項(xiàng)基本功有了初步認(rèn)識(shí),就可以逐個(gè)深入學(xué)習(xí)一些,然后把學(xué)到的知識(shí)再次用于完整的設(shè)計(jì)流程。如此反復(fù),就可以逐步提高設(shè)計(jì)水平。采用這樣的循序漸進(jìn)、螺旋式上升的方法,只要通過培訓(xùn)入了門,就可以自學(xué)自練,自我提高。

市面上出售的有關(guān)FPGA設(shè)計(jì)的書籍為了保證結(jié)構(gòu)的完整性,對(duì) FPGA設(shè)計(jì)的每一個(gè)方面分開介紹,每一方面雖然深入,但是由于缺少其他相關(guān)方面的支持,讀者很難付諸實(shí)踐,只有通讀完全書才能對(duì)FPGA設(shè)計(jì)獲得一個(gè)整體的認(rèn)識(shí)。這樣的書籍,作為工程培訓(xùn)指導(dǎo)書不行,可以作為某一個(gè)方面進(jìn)階的參考書。

對(duì)于新入職的員工來說,他們往往對(duì)FPGA的整體設(shè)計(jì)流程有了初步認(rèn)識(shí),5項(xiàng)基本功的某幾個(gè)方面可能很扎實(shí)。但是由于某個(gè)或某幾個(gè)方面能力的欠缺,限制了他們獨(dú)自完成整個(gè)設(shè)計(jì)流程的能力。入職培訓(xùn)的目的就是幫助他們掌握整體設(shè)計(jì)流程,培養(yǎng)自我獲取信息的能力,通過幾個(gè)設(shè)計(jì)流程來回的訓(xùn)練,形成自我促進(jìn)、自我發(fā)展的良性循環(huán)。在這一過程中,隨著對(duì)工作涉及的知識(shí)的廣度和深度的認(rèn)識(shí)逐步清晰,新員工的自信心也會(huì)逐步增強(qiáng),對(duì)個(gè)人的發(fā)展方向也會(huì)逐步明確,才能積極主動(dòng)地參與到工程項(xiàng)目中來。

最后總結(jié)幾點(diǎn):

1)看代碼,建模型

只有在腦海中建立了一個(gè)個(gè)邏輯模型,理解FPGA內(nèi)部邏輯結(jié)構(gòu)實(shí)現(xiàn)的基礎(chǔ),才能明白為什么寫Verilog和寫C整體思路是不一樣的,才能理解順序執(zhí)行語言和并行執(zhí)行語言的設(shè)計(jì)方法上的差異。在看到一段簡(jiǎn)單程序的時(shí)候應(yīng)該想到是什么樣的功能電路。

2)用數(shù)學(xué)思維來簡(jiǎn)化設(shè)計(jì)邏輯

學(xué)習(xí)FPGA不僅邏輯思維很重要,好的數(shù)學(xué)思維也能讓你的設(shè)計(jì)化繁為簡(jiǎn),所以啊,那些看見高數(shù)就頭疼的童鞋需要重視一下這門課哦。舉個(gè)簡(jiǎn)單的例子,比如有兩個(gè)32bit的數(shù)據(jù)X[31:0]與Y[31:0]相乘。當(dāng)然,無論Altera還是Xilinx都有現(xiàn)成的乘法器IP核可以調(diào)用,這也是最簡(jiǎn)單的方法,但是兩個(gè)32bit的乘法器將耗費(fèi)大量的資源。那么有沒有節(jié)省資源,又不太復(fù)雜的方式來實(shí)現(xiàn)呢?我們可以稍做修改:

將X[31:0]拆成兩部分X1[15:0]和X2[15:0],令X1[15:0]=X[31:16],X2[15:0]=X[15:0],則X1左移16位后與X2相加可以得到X;同樣將Y[31:0]拆成兩部分Y1[15:0]和Y2[15:0],令 Y1[15:0]=Y[31:16],Y2[15:0]=Y[15:0],則Y1左移16位后與Y2相加可以得到Y(jié);則X與Y的相乘可以轉(zhuǎn)化為X1和X2 分別與Y1和Y2相乘,這樣一個(gè)32bit*32bit的乘法運(yùn)算轉(zhuǎn)換成了四個(gè)16bit*16bit的乘法運(yùn)算和三個(gè)32bit的加法運(yùn)算。轉(zhuǎn)換后的占用資源將會(huì)減少很多,有興趣的童鞋,不妨綜合一下看看,看看兩者差多少。

3)時(shí)鐘與觸發(fā)器的關(guān)系

“時(shí)鐘是時(shí)序電路的控制者” 這句話太經(jīng)典了,可以說是FPGA設(shè)計(jì)的圣言。FPGA的設(shè)計(jì)主要是以時(shí)序電路為主,因?yàn)榻M合邏輯電路再怎么復(fù)雜也變不出太多花樣,理解起來也不沒太多困難。但是時(shí)序電路就不同了,它的所有動(dòng)作都是在時(shí)鐘一拍一拍的節(jié)奏下轉(zhuǎn)變觸發(fā),可以說時(shí)鐘就是整個(gè)電路的控制者,控制不好,電路功能就會(huì)混亂。

打個(gè)比方,時(shí)鐘就相當(dāng)于人體的心臟,它每一次的跳動(dòng)就是觸發(fā)一個(gè) CLK,向身體的各個(gè)器官供血,維持著機(jī)體的正常運(yùn)作,每一個(gè)器官體統(tǒng)正常工作少不了組織細(xì)胞的構(gòu)成,那么觸發(fā)器就可以比作基本單元組織細(xì)胞。時(shí)序邏輯電路的時(shí)鐘是控制時(shí)序邏輯電路狀態(tài)轉(zhuǎn)換的“發(fā)動(dòng)機(jī)”,沒有它時(shí)序邏輯電路就不能正常工作,因?yàn)闀r(shí)序邏輯電路主要是利用觸發(fā)器存儲(chǔ)電路的狀態(tài),而觸發(fā)器狀態(tài)變換需要時(shí)鐘的上升或下降沿!由此可見時(shí)鐘在時(shí)序電路中的核心作用!

最后簡(jiǎn)單說一下體會(huì)吧,歸結(jié)起來就多實(shí)踐、多思考、多問。實(shí)踐出真知,看 100遍別人的方案不如自己去實(shí)踐一下。實(shí)踐的動(dòng)力一方面來自興趣,一方面來自壓力,我個(gè)人覺得后者更重要。有需求會(huì)容易形成壓力,也就是說最好能在實(shí)際的項(xiàng)目開發(fā)中鍛煉,而不是為了學(xué)習(xí)而學(xué)習(xí)。

在實(shí)踐的過程中要多思考,多想想問題出現(xiàn)的原因,問題解決后要多問幾個(gè)為什么,這也是經(jīng)驗(yàn)積累的過程,如果有寫項(xiàng)目日志的習(xí)慣更好,把問題及原因、解決的辦法都寫進(jìn)去。最后還要多問,遇到問題思索后還得不到解決就要問了,畢竟個(gè)人的力量是有限的,問同學(xué)同事、問搜索引擎、問網(wǎng)友都可以,一篇文章、朋友們的點(diǎn)撥都可能幫助自己快速解決問題。

-

FPGA

+關(guān)注

關(guān)注

1629文章

21736瀏覽量

603421 -

C語言

+關(guān)注

關(guān)注

180文章

7604瀏覽量

136842

原文標(biāo)題:從匯編、C語言為起點(diǎn),我十年FPGA開發(fā)設(shè)計(jì)經(jīng)驗(yàn)總結(jié)

文章出處:【微信號(hào):weixin21ic,微信公眾號(hào):21ic電子網(wǎng)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

fpga時(shí)序分析案例 調(diào)試FPGA經(jīng)驗(yàn)總結(jié)

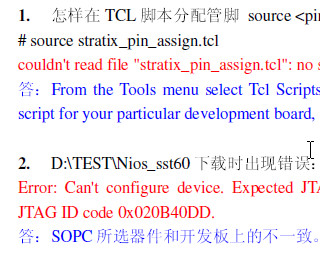

SOPC Builder/Nios 學(xué)習(xí)經(jīng)驗(yàn)總結(jié)

做四軸飛行器的經(jīng)驗(yàn)總結(jié)

開關(guān)電源測(cè)量的經(jīng)驗(yàn)總結(jié)

模擬電路設(shè)計(jì)經(jīng)驗(yàn)總結(jié)

基于verilog的FPGA編程經(jīng)驗(yàn)總結(jié)

FPGA設(shè)計(jì)的經(jīng)驗(yàn)技巧,FPGA開發(fā)設(shè)計(jì)經(jīng)驗(yàn)總結(jié)

FPGA設(shè)計(jì)的經(jīng)驗(yàn)技巧,FPGA開發(fā)設(shè)計(jì)經(jīng)驗(yàn)總結(jié)

評(píng)論