之前的文章介紹過DAC幾種結構和開關切換策略,但在實際應用中,其性能受到電容陣列的匹配影響,此時需要引入校準技術來優化這一問題。

背景

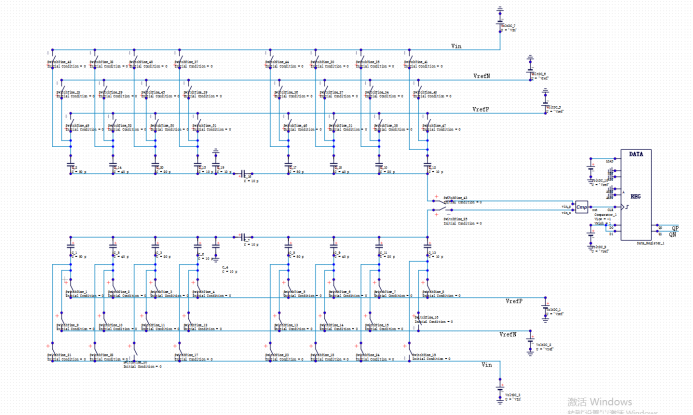

首先使用巨霖的通用電路仿真工具PowerExpert畫出SARADC中DAC+比較器的理想模型:

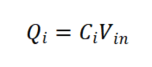

由上圖所示,前半部分是電容陣列,比較器后是數據寄存器,用來存放每一次比較器數輸出的數字碼,并送回電容陣列控制開關的切換。在采樣階段電容陣列開關分別接輸入信號Vin,此時陣列中每個電容上儲存的電荷為:

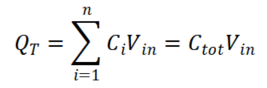

所有電容存儲的電荷量之和為:

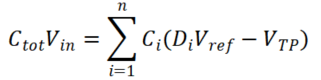

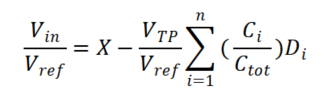

在比較階段轉換電容下極板到VrefP/N,通過電荷守恒方程可得:

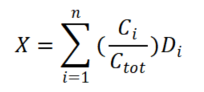

上式 為電容的上極板電壓,由此可知,輸出碼等于:

為電容的上極板電壓,由此可知,輸出碼等于:

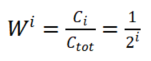

在理想情況下,電容陣列從LSB開始按照二進制加權遞增, 應是精準的二進制值,然而在實際工藝中,電容值會存在失配,導致權重

應是精準的二進制值,然而在實際工藝中,電容值會存在失配,導致權重 偏離理想值,此時輸入電壓與輸出數字碼關系為:

偏離理想值,此時輸入電壓與輸出數字碼關系為:

此現象在180nm及以下工藝中更加明顯。此時就需要一種校準方式解決此問題,通過傳統引入冗余位設計雖然可以避免失配,但是會增加轉換位數從而增加功耗和比較時間,通過注入校正電荷校準則需要高精度的DAC電路,難以實現且會占用額外面積。

原理

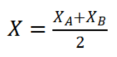

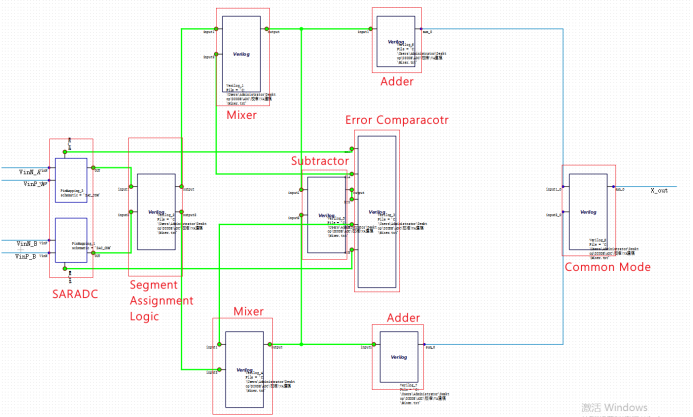

下面介紹一種名為Split ADC的架構來優化上述問題,該架構將一個SARADC“分裂”成兩個,稱為通道A和通道B,兩個陣列分配從LSB位到MSB位的電容。通過后續動態分配模塊實現將比較器決策分配給不同電容段,權重模塊將后續校準電路校準后的權重 與動態分配模塊產生的決策

與動態分配模塊產生的決策 相乘,然后將上下兩通道的相乘結果

相乘,然后將上下兩通道的相乘結果 取差模

取差模 送入后續誤差比較器,再取共模

送入后續誤差比較器,再取共模 輸出以抑制隨機噪聲。以一個16位高精度的SARADC為例,原理圖如下所示:

輸出以抑制隨機噪聲。以一個16位高精度的SARADC為例,原理圖如下所示:

動態分配模塊

將兩個SAR決策邏輯序列 的輸出接到一個動態分配模塊,該模塊是使用一個4位的LFSR實現,每個轉換周期更新一個值,生成新的PRN值。在傳統無校準的結構中,每一個電容段只會對應一個權重,如果這個電容段出現了失配,那么輸出結果將會出現偏差,而動態分配模塊的作用是隨機改變電容段和SAR決策邏輯序列

的輸出接到一個動態分配模塊,該模塊是使用一個4位的LFSR實現,每個轉換周期更新一個值,生成新的PRN值。在傳統無校準的結構中,每一個電容段只會對應一個權重,如果這個電容段出現了失配,那么輸出結果將會出現偏差,而動態分配模塊的作用是隨機改變電容段和SAR決策邏輯序列 的映射關系,避免輸入信號長期維持在一個模擬量導致某些位的輸出數字量無法被校準。可以使用Verilog編寫動態分配模塊并導入PowerExpert中。

的映射關系,避免輸入信號長期維持在一個模擬量導致某些位的輸出數字量無法被校準。可以使用Verilog編寫動態分配模塊并導入PowerExpert中。

誤差比較模塊

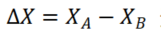

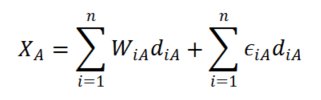

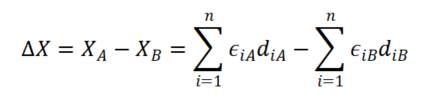

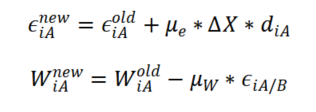

誤差比較模塊將AB兩個通道的差模輸出作為輸入,其中A通道的輸出為以下表達式:

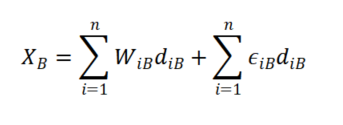

前項表示理想權重下的輸出,后項表示誤差,同理B通道的輸出如下:

誤差比較器得到的輸入為:

上式在實際電路設計中還需要考慮兩個通道的輸入信號偏移和增益誤差,此處忽略。誤差比較器的目的就是通過調整 使得

使得 等于零,從而使AB兩通道的差模輸出為0。具體實現是通過LMS算法迭代來逐漸修正

等于零,從而使AB兩通道的差模輸出為0。具體實現是通過LMS算法迭代來逐漸修正 ,下面簡單舉例介紹LMS算法原理和在誤差比較器里面的運用。

,下面簡單舉例介紹LMS算法原理和在誤差比較器里面的運用。

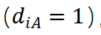

假設第五個電容段存在失配,同時也被激活 ,那么子通道A的權重由實際權重0.5變為了

,那么子通道A的權重由實際權重0.5變為了 ,誤差項

,誤差項 被送到了

被送到了 中,LMS算法檢測到

中,LMS算法檢測到 ,于是進行以下迭代:

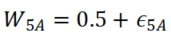

,于是進行以下迭代:

?

?  都是步長參數,用來控制收斂速度。

都是步長參數,用來控制收斂速度。  后將迭代的

后將迭代的 新權重結果送入乘法器中與電容陣列決策

新權重結果送入乘法器中與電容陣列決策 相乘,得到校準后的結果。在實際電路設計中,為了高效估計誤差參數,會根據多次收集的

相乘,得到校準后的結果。在實際電路設計中,為了高效估計誤差參數,會根據多次收集的 和電容陣列激活信號構建矩陣方程,再使用最小二乘法求解已優化誤差參數估計,從而減小功耗,有興趣的讀者可以自行了解。 ? ?

和電容陣列激活信號構建矩陣方程,再使用最小二乘法求解已優化誤差參數估計,從而減小功耗,有興趣的讀者可以自行了解。 ? ?

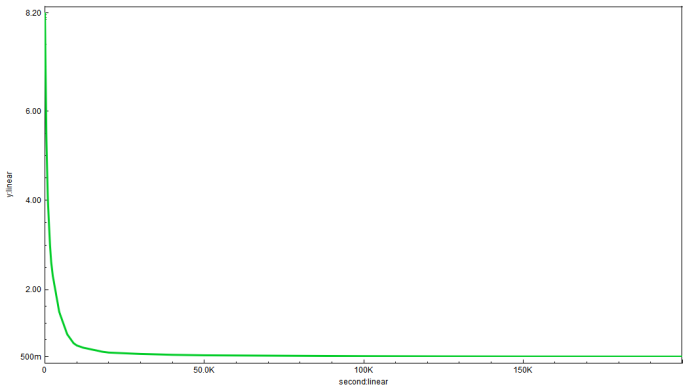

手動在電容陣列中添加10%的誤差,從下面仿真得出的波形可以看出,輸出X_out被逐漸縮小,最終穩定在理想權重0.5。

歡迎從官網申請試用我們的軟件,過程中的任何疑問可聯系support技術人員,期待與您的交流!

-

寄存器

+關注

關注

31文章

5394瀏覽量

122032 -

比較器

+關注

關注

14文章

1697瀏覽量

107815 -

dac

+關注

關注

43文章

2327瀏覽量

192258 -

模數轉換器

+關注

關注

26文章

3246瀏覽量

127361 -

電路仿真

+關注

關注

37文章

209瀏覽量

95923

原文標題:全數字校準在模數轉換器中的應用與仿真

文章出處:【微信號:巨霖,微信公眾號:巨霖】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

模數轉換器的工作原理

5962-9581501HXA高端AD模數轉換器

模數轉換器ADC簡介

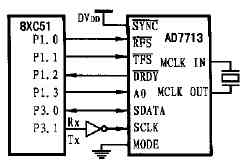

24位模數轉換器AD7713及其應用

嵌入式模數轉換器的原理及應用

電流積分模數轉換器(ADC),什么是電流積分模數轉換器(AD

模數轉換器分類_模數轉換器選型

什么是模數轉換器

ADS1112精密、連續自校準模數轉換器(ADC)數據表

評論