AS配置方式由FPGA器件引導配置操作過程,它控制著外部存儲器及其初始化過程,EPCS系列配置芯片如EPCS1、EPCS4配置器件專供AS模式。使用Altera串行配置器件來完成,FPGA器件處于主動地位,配置器件處于從屬地位。配置數據通過DATA0引腳送入 FPGA。配置數據被同步在DCLK輸入上,1個時鐘周期傳送1位數據。

PS配置方式則由外部計算機或其它控制器控制配置過程。通過加強型配置器件(EPC16,EPC8,EPC4)等配置器件來完成,在PS配置期間,配置數據從外部儲存部件,通過DATA0引腳送入FPGA。配置數據在DCLK上升沿鎖存,1個時鐘周期傳送1位數據。

JTAG接口是一個業界標準,主要用于芯片測試等功能,使用IEEE Std 1149.1聯合邊界掃描接口引腳,支持JAM STAPL標準,可以使用Altera下載電纜或主控器來完成。

FPGA在正常工作時,它的配置數據存儲在SRAM中,加電時須重新下載。在實驗系統中,通常用計算機或控制器進行調試,因此可以使用PS。在實用系統中,多數情況下必須由FPGA主動引導配置操作過程,這時FPGA將主動從外圍專用存儲芯片中獲得配置數據,而此芯片中FPGA配置信息是用普通編程器將設計所得的pof格式的文件燒錄進去。

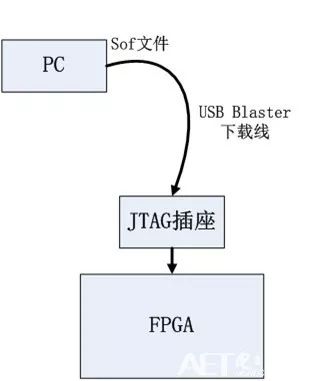

JTAG模式在線下載FPGA的原理如圖7.15所示,PC端的Quartus II軟件通過下載線纜將bit流(sof文件)下載到FPGA內部,下載完成后FPGA中立刻執行下載代碼,速度很快,非常適合調試。

圖7.15 基于JTAG的在線配置原理

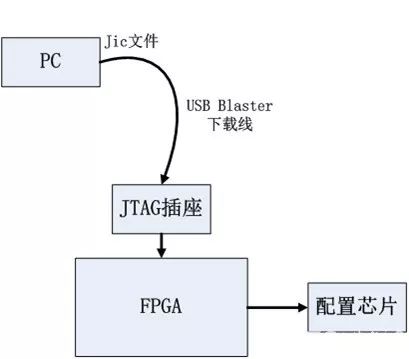

FPGA下載數據到配置芯片的原理如圖7.16所示,PC端的Quartus II軟件通過下載線纜將bit流(jic文件)下載到配置芯片中。由于配置芯片和JTAG接口都是分別連接到FPGA的,他們不是直接連接,所以配置文件從PC先是傳送到FPGA,然后FPGA內部再轉送給配置芯片,這個過程FPGA相當于起到一個橋接的作用。

圖7.16 基于FPGA的配置芯片固化原理

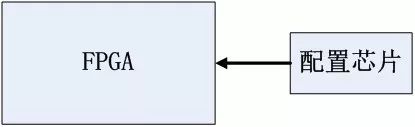

看完JTAG模式下在線配置FPGA和燒錄配置芯片的原理,我們再了解一下FPGA上電初始的配置過程。FPGA上電后,內部的控制器首先工作,確認當前的配置模式,如果是外部配置芯片啟動,則通過和外部配置芯片的接口(如我們的SPI接口)將配置芯片的數據加載到FPGA的RAM中,配置完成后開始正式運行,請數據流加載方向如圖7.17所示。當然了,有人可能在想,JTAG在線配置是否和配置芯片加載相沖突呢?非也,JTAG在線配置的優先級是最高的,無論此時FPGA中在運行什么邏輯,只要JTAG下載啟動,則FPGA便停下當前的工作,開始運行JTAG下載的新的配置數據。

圖7.17 FPGA離線加載原理

-

FPGA

+關注

關注

1629文章

21748瀏覽量

603912 -

JTAG

+關注

關注

6文章

400瀏覽量

71707

原文標題:【博文精選】Altera FPGA配置方式之AS/PS/JTAG配置方式

文章出處:【微信號:ChinaAET,微信公眾號:電子技術應用ChinaAET】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

請問lmk04828-EP設置DCLKx的模擬延遲失敗,導致時鐘不穩定的原因?怎么解決?

通過DSP6455的MCBSP配置TLV320AIC20,如果想使用LINEI和LINEO,還需要哪些別的配置嗎?

固化FPGA配置芯片的方式

樹莓派4B的WiFi配置過程

工控機bios如何修改引導方式

FPGA的配置模式有哪些?具體配置過程是怎樣的?

FPGA開發過程中配置全局時鐘需要注意哪些問題

AMD Xilinx 7系列FPGA的Multiboot多bit配置

光纖傳輸信息時的工作過程

FPGA的內部結構工作過程

AS配置方式由FPGA器件引導配置操作過程

AS配置方式由FPGA器件引導配置操作過程

評論