AXI接口FIFO是從Native接口FIFO派生而來的。AXI內存映射接口提供了三種樣式:AXI4、AXI3和AXI4-Lite。除了Native接口FIFO支持的應用外,AXI FIFO還可以用于AXI系統總線和點對點高速應用。

AXI接口FIFO不支持Builtin FIFO和 Shift Register FIFO配置。

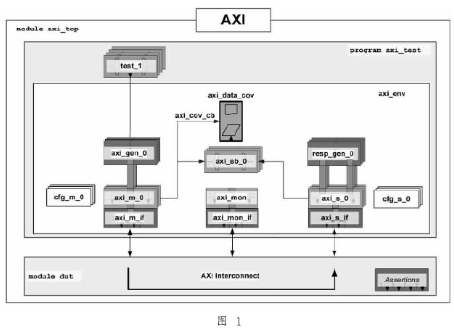

當需要連接到其他AXI功能時,可以在Native接口FIFO支持的相同應用中使用AXI FIFO。AXI FIFO可以通過IP集成器集成到系統中。

1 AXI FIFO的功能

AXI FIFO的功能概述主要體現在其對AXI Memory Mapped接口中讀寫通道的便捷集成能力上。

1.1 讀寫通道的分離

對于AXI Memory Mapped接口,AXI規范定義了寫通道和讀通道。

寫通道包括寫地址通道、寫數據通道和寫響應通道。

讀通道包括讀地址通道和讀數據通道。

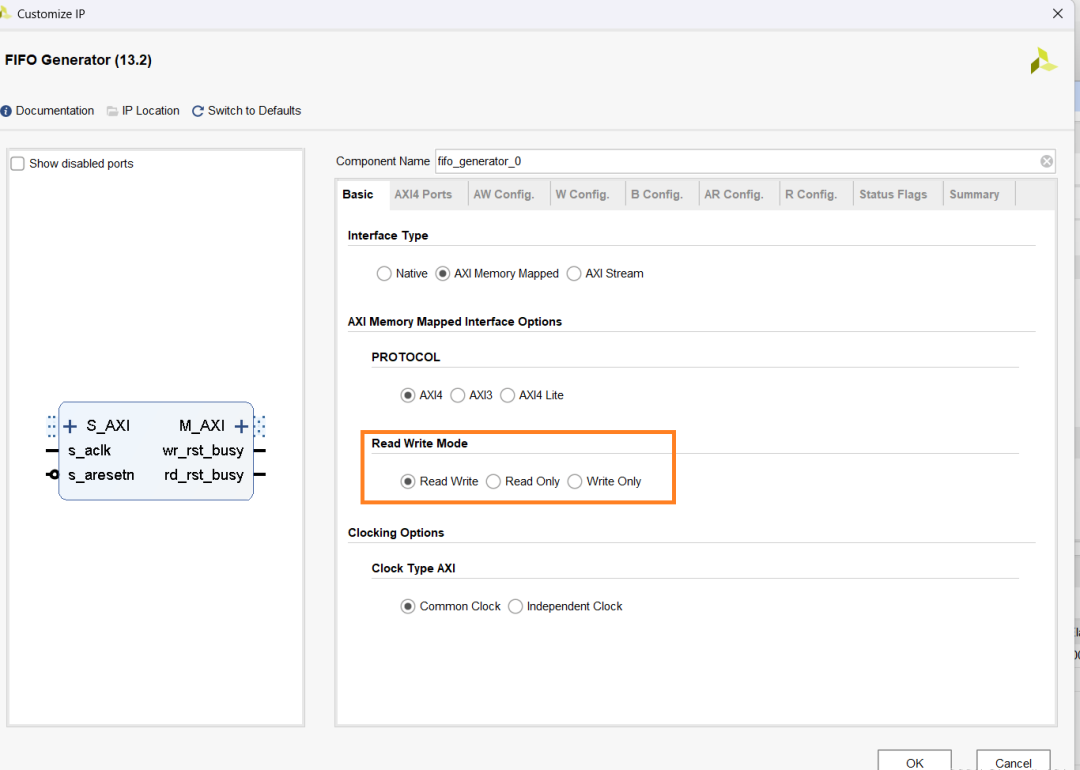

FIFO Generate IP核提供了為AXI Memory Mapped生成單獨的寫通道或讀通道,或者同時生成寫通道和讀通道的能力。如下圖所示。

對于寫通道,集成了三個FIFO:一個用于寫地址通道,一個用于寫數據通道,以及一個用于寫響應通道。

對于讀通道,集成了兩個FIFO:一個用于讀地址通道,一個用于讀數據通道。

當同時選擇寫通道和讀通道時,FIFO Generate IP核將集成五個獨立的FIFO。

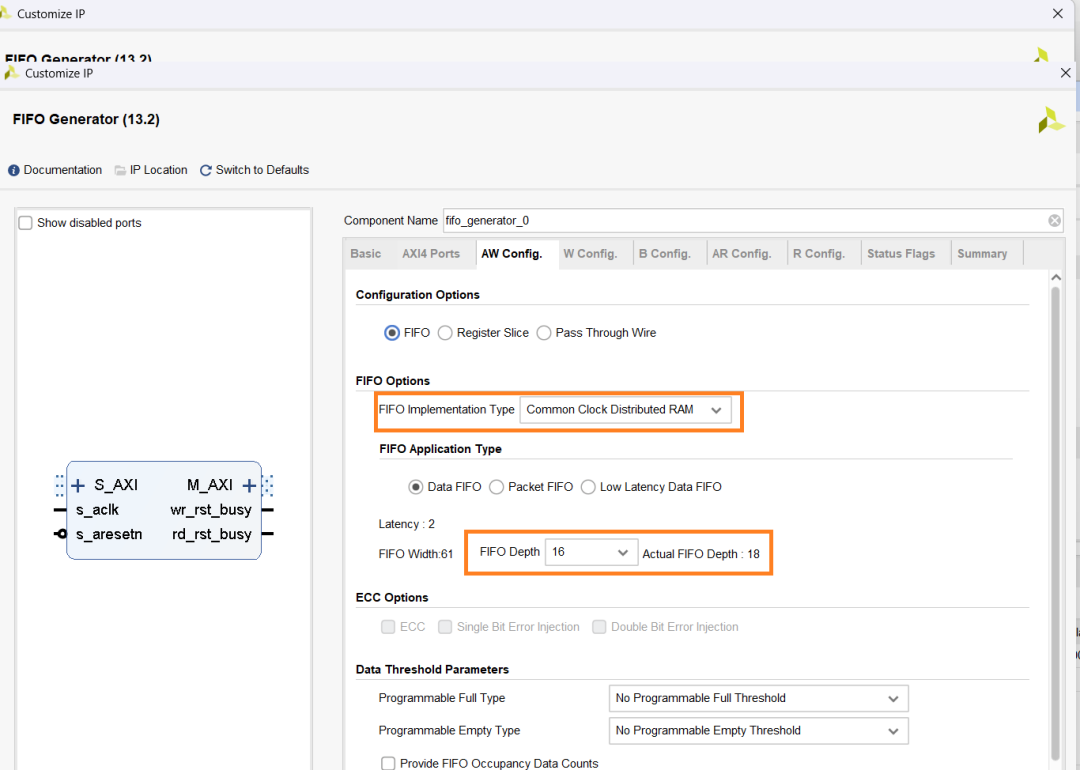

1.2 每個通道的獨立配置

對于每個通道,FIFO Generate IP核都可以獨立配置以生成基于Block RAM或Distributed RAM FIFO。每個FIFO的深度也可以獨立配置,以滿足特定應用的數據緩存需求。如下圖所示。

AXI FIFO的使用有助于簡化高速數據傳輸和處理的系統設計,因為它們能夠與AXI總線標準無縫集成,提供高吞吐量和低延遲的數據傳輸能力。這使得AXI FIFO成為高性能計算、圖像處理、視頻傳輸等領域的理想選擇。

2 AXI FIFO的時序

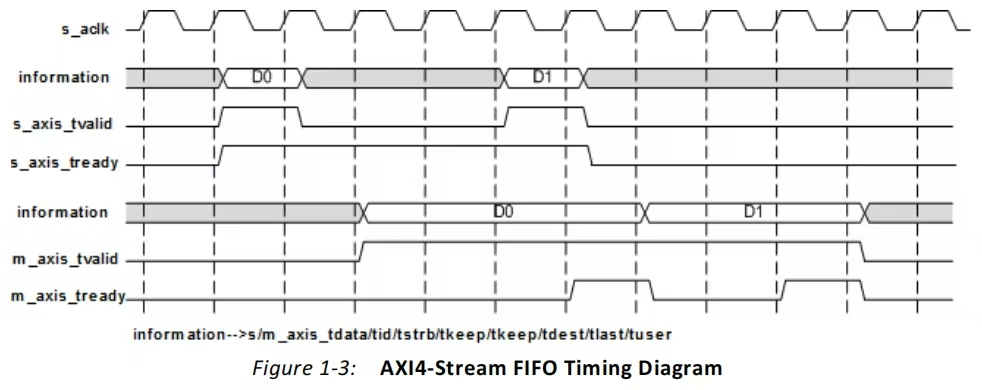

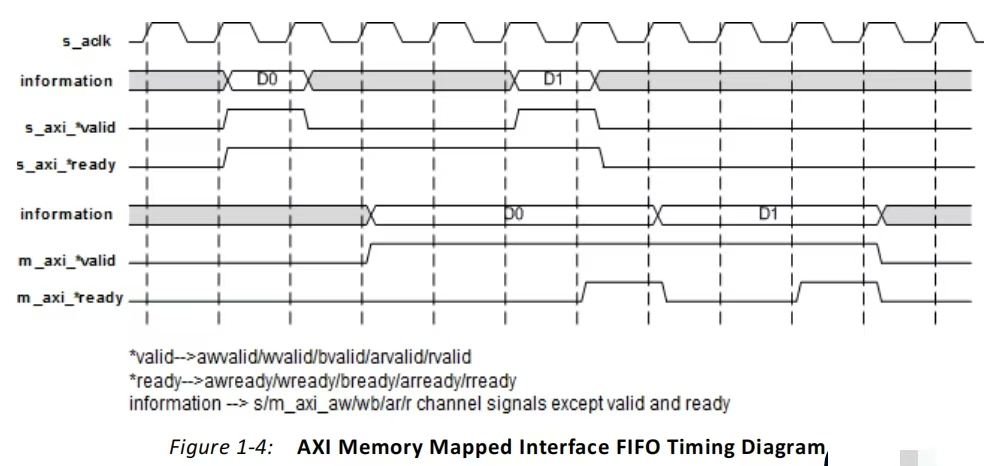

AXI接口協議使用雙向的有效(Valid)和就緒(Ready)握手機制。信息源使用有效信號來表示通道上何時有有效的數據或控制信息可用。信息目標使用就緒信號來表示何時可以接受數據。圖1-3展示了AXI4-Stream FIFO的寫和讀操作的示例時序圖,而圖1-4則展示了AXI Memory Mapped 接口FIFO的寫和讀操作的示例時序圖。

在圖1-3和圖1-4中,信息源生成有效信號(valid)以指示數據何時可用。目標生成就緒信號(ready)以指示它可以接受數據,并且只有當有效信號和就緒信號都為高時,才會發生數據傳輸。

對于AXI4-Stream FIFO,寫操作和讀操作通常涉及連續的數據流傳輸。在圖1-3中,看到寫操作和讀操作的時序圖,顯示了有效信號和就緒信號如何協同工作以完成數據傳輸。

而對于AXI Memory Mapped接口FIFO,寫操作和讀操作通常與特定的內存地址相關聯。在圖1-4中,看到寫地址通道、寫數據通道、寫響應通道以及讀地址通道和讀數據通道的時序圖。這些通道協同工作,通過有效和就緒信號的握手機制,確保數據在源和目標之間的正確傳輸。

由于AXI FIFO是從Native接口FIFO派生而來的,因此它們之間的很多行為是相似的。就緒信號是基于FIFO中可用空間來生成的,當FIFO中有空間時,就緒信號保持高電平以允許寫入FIFO。只有當FIFO中沒有剩余空間進行額外的寫入操作時,就緒信號才會被拉低。有效信號則是基于FIFO中數據的可用性來生成的,當FIFO中有數據可供讀取時,有效信號保持高電平以允許從FIFO中讀取數據。只有當FIFO中沒有可供讀取的數據時,有效信號才會被拉低。這些信息信號被映射到Native 接口FIFO的din和dout總線上。AXI FIFO的寬度是通過連接AXI接口的所有信息信號來確定的。這些信息信號包括除有效和就緒握手信號之外的所有AXI信號。

在AXI協議中,這種握手機制確保了數據在源和目標之間的可靠傳輸。當源設備準備好發送數據時,它會將有效信號置高,表示數據已經準備好。然后,目標設備會檢查就緒信號。只有當就緒信號也為高時,目標設備才會從源設備接收數據。這種機制確保了數據在傳輸過程中不會被丟失或發生錯誤。

AXI FIFO僅在First Word Fall Through模式下運行。該功能提供了在不執行讀取操作的情況下查看FIFO中下一個可用字的能力。當FIFO中有數據時,第一個字會自動通過FIFO并出現在輸出數據總線上。

注意:對于AXI接口,由于復位輸入總是異步的,因此在內核內部會自動啟用安全電路。

3 AXI FIFO的直通線(Pass Through Wire)

AXI Memory Mapped接口的IP核提供了直通線選項,使得所有輸入信號能夠直接傳遞到輸出,而無需經過任何處理或緩存。這在某些情況下可能很有用,比如當您希望將信號直接轉發到另一個接口或組件時。

3.1 數據包FIFO(Packet FIFO)

數據包FIFO配置確保了在接收到數據包(突發傳輸)的末尾(LAST節拍)之前,不會開始數據包的傳輸。這樣做可以確保一旦主設備側開始傳輸,數據就能不間斷地可用,從而避免了AXI數據通道的源端停滯。這對于數據起源于主設備的應用場景特別有價值。

例如,當實時信號通道以低于下游AXI交換機和/或從設備目的地的數據速率運行時,如高帶寬內存,這種配置就非常有用。

數據包FIFO原理既適用于AXI4/AXI3 Memory Mapped突發事務(寫入和讀取),也適用于AXI4-Stream數據包傳輸。這個特性有時被稱為“store-and-forward”,它描述了內存映射寫入和流傳輸的行為。對于內存映射讀取,事務會延遲到FIFO中有足夠的空位來確保整個讀取數據包能夠不間斷地緩沖,這是根據AR(地址讀取)通道事務的預測進行的。讀取事務實際上并不依賴RLAST信號。

數據包FIFO特性支持公共時鐘AXI4/AXI3和公共/獨立時鐘AXI4-Stream配置。它不支持AXI4-Lite配置。

3.2 AXI4-Stream Packet FIFO

AXI4-Stream Packet FIFO和AXI4/AXI3 Packet FIFO是兩種不同類型的FIFO,它們分別使用AXI4-Stream接口和AXI Memory Mapped接口來實現數據包FIFO的功能。

AXI4-Stream Packet FIFO使用AXI4-Stream接口。當在AXI4-Stream Slave側接收到一個完整的數據包(由tlast標記)或AXI4-Stream FIFO已滿時,FIFO Generate IP核會在AXI4-Stream Master側指示tvalid。由于FIFO變滿而在Master側指示tvalid是一個異常情況,在這種情況下,Packet FIFO會作為一個正常的FWFT(First Word Fall Through)FIFO工作,將Slave側接收到的數據轉發到Master側,直到在Slave側接收到tlast。

3.3 AXI4/AXI3 Packet FIFO

AXI4/AXI3 Packet FIFO 使用AXI Memory Mapped接口,它支持AXI協議中的寫(W)和讀(R)通道以及相關的地址(AW/AR)通道。Packet FIFO允許在數據傳輸過程中存儲完整的數據包,直到數據包被完全接收或發送。

寫通道上的Packet FIFO

當在AXI W通道Slave側接收到一個由wlast標記的完整數據包時,FIFO Generate IP核會在AXI AW通道Master側指示awvalid。這意味著寫地址(AW)的傳輸只有在W通道Slave側接收到請求傳輸所需的所有數據后才會被發送到AXI Write Address Channel。

寫通道Packet FIFO與寫地址通道(AW通道)耦合,這確保了在發送寫請求之前,有足夠的空間來存儲與該請求相關的所有數據。

W通道的最小深度被設置為512,這允許寫通道Packet FIFO存儲兩個最大長度的數據包。

讀通道上的Packet FIFO

當在AXI R通道Master側接收到一個由rlast標記的完整數據包時,FIFO Generate IP核會在AXI R通道Slave側指示rvalid。這意味著讀數據的傳輸(通過R通道)已經完成,并且整個數據包已經被成功接收。

讀通道Packet FIFO與讀地址通道(AR通道)耦合,這確保了在發送讀請求之前,Packet FIFO中有足夠的空間來存儲與該請求相關的數據。如果Packet FIFO中沒有足夠的空間,則不會向AXI Read Address Channel發送AR傳輸。

R通道的最小深度也被設置為512,允許讀通道Packet FIFO存儲兩個最大長度的數據包。

這種機制允許數據包在傳輸過程中被緩存,確保數據傳輸的連續性和完整性,同時避免由于數據不匹配或丟失而導致的錯誤。這對于需要處理大量數據或需要確保數據完整性的應用場景(如高速數據傳輸或實時信號處理)非常有用。

原文鏈接:https://tencentcloud.csdn.net/678a2f13edd0904849a69a14.html

-

接口

+關注

關注

33文章

8783瀏覽量

152463 -

fifo

+關注

關注

3文章

394瀏覽量

44120 -

總線

+關注

關注

10文章

2915瀏覽量

88737 -

AXI

+關注

關注

1文章

131瀏覽量

16850

原文標題:AXI接口FIFO簡介

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

可以在EDK中使用Axi4Stream接口/總線嗎?

AXI流FIFO掛起

高級可擴展接口(AXI)簡介

AXI FIFO和AXI virtual FIFO這兩個IP的使用方法

AXI STREAM FIFO如何設置雙時鐘

高級可擴展接口(AXI)簡介

你必須了解的AXI總線詳解

評論