1.名詞解釋:

FPGA:現(xiàn)場(chǎng)可編程門陣列,一般工藝SRAM(易失性),所以要外掛配置芯片。

CPLD:復(fù)雜可編程邏輯器件,一般工藝Flash(不易失)。

SOC:片上系統(tǒng)

SOPC:片上可編程系統(tǒng)

2.Verilog語法類:

①Verilog兩大數(shù)據(jù)類型:一類是線網(wǎng)類型,另一類是寄存器類型。

線網(wǎng)類型表示硬件電路元件之間實(shí)際存在的物理連線,有很多種:wire、tri、wor等等,當(dāng)然日常使用wire最多,其他的都沒遇到過。

寄存器類型表示一個(gè)抽象的數(shù)據(jù)存儲(chǔ)單元,只能在initial或always內(nèi)部被賦值,并且變量的值將從一條賦值語句保持到下一條賦值語句。有5種:reg、time(64位無符號(hào)的時(shí)間變量)、integer(32位帶符號(hào)的整數(shù)型變量)、real/realtime(64位帶符號(hào)的實(shí)數(shù)型變量)。reg用的最多。

②Verilog建模方式:結(jié)構(gòu)化描述方式、數(shù)據(jù)流描述方式、行為描述方式、混合描述方式。

結(jié)構(gòu)描述是指通過調(diào)用邏輯原件,描述它們之間的連接來建立邏輯電路的verilog HDL模型。這里的邏輯元件包括內(nèi)置邏輯門、自主研發(fā)的已有模塊、商業(yè)IP模塊。

數(shù)據(jù)流描述是指根據(jù)信號(hào)之間的邏輯關(guān)系,采用持續(xù)賦值語句描述邏輯電路的方式。通過觀察是否使用assign賦值語句可以判斷是否有數(shù)據(jù)流描述。

行為描述是指只注重實(shí)現(xiàn)的算法,不關(guān)心具體的硬件實(shí)現(xiàn)細(xì)節(jié)。這與C語言編程非常類似。通過觀察是否使用initial 或always語句塊可以判斷是否有行為描述。

混合描述是指以上幾種描述方法都存在的一種描述方式。具體在一個(gè)工程中,不可能只是用單獨(dú)哪一種描述方式,一般都是各種描述方式的混合。

3.VHDL相對(duì)于Verilog不能描述的層級(jí)?

網(wǎng)上有段話說的是:Verilog在其門級(jí)描述的底層,即晶體管開關(guān)級(jí)的描述方面比VHDL更強(qiáng)一些,所以即使使用VHDL的設(shè)計(jì)環(huán)境,在底層實(shí)質(zhì)上也會(huì)由Verilog描述的器件庫所支持。

Verilog較為適合系統(tǒng)級(jí)、算法級(jí)、RTL級(jí)、門級(jí)、開關(guān)級(jí)的設(shè)計(jì),而對(duì)于特大型(千萬門級(jí)以上)的系統(tǒng)設(shè)計(jì),則VHDL更為適合。(VHDL比較嚴(yán)謹(jǐn),而Verilog可以花式編碼)

所以,VHDL不能描述開關(guān)級(jí)。

4.阻塞與非阻塞的區(qū)別:

對(duì)于代碼:

1 //blocking; 2 begin 3 B = A; 4 C = B + 1; 5 end 6 //non-blocking; 7 begin 8 B <= A; 9 C <= B + 1; 10 end

在always語句內(nèi)部過程賦值語句有兩種,阻塞賦值語句與非阻塞賦值語句。

兩者主要區(qū)別是完成賦值操作的時(shí)間不同,阻塞賦值語句的賦值操作是立即執(zhí)行的,即執(zhí)行后一句的時(shí)候,前一句的賦值已經(jīng)完成;而非阻塞賦值語句的賦值操作到結(jié)束順序語句塊時(shí)才完成賦值操作,即賦值操作完成后,語句塊的執(zhí)行也就結(jié)束了。即阻塞是串行執(zhí)行,非阻塞是并行執(zhí)行的。對(duì)于上述代碼,阻塞賦值中相當(dāng)于C = A + 1;非阻塞賦值中B先前的值被A替代,但C的值是B先前值加1。

5.亞穩(wěn)態(tài)是什么怎么解決亞穩(wěn)態(tài)?

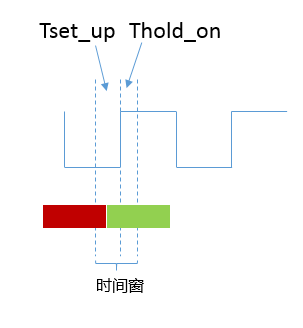

觸發(fā)器輸入端口的數(shù)據(jù)在時(shí)間窗口內(nèi)發(fā)生變化,會(huì)導(dǎo)致時(shí)序違例。觸發(fā)器的輸出在一段時(shí)間內(nèi)徘徊在一個(gè)中間電平,既不是0也不是1。這段時(shí)間稱為決斷時(shí)間(resolution time)。經(jīng)過resolution time之后Q端將穩(wěn)定到0或1上,但是穩(wěn)定到0或者1,是隨機(jī)的,與輸入沒有必然的關(guān)系。

觸發(fā)器由于物理工藝原因,數(shù)據(jù)并不是理想化的只要觸發(fā)沿時(shí)刻不變即可。觸發(fā)器有固定的建立時(shí)間,保持時(shí)間。

建立時(shí)間:在時(shí)鐘有效沿到來前數(shù)據(jù)需要穩(wěn)定的時(shí)間。

保持時(shí)間:在時(shí)鐘有效沿之后數(shù)據(jù)還需要保持不變的時(shí)間。

后果:會(huì)給設(shè)計(jì)帶來致命的功能故障。

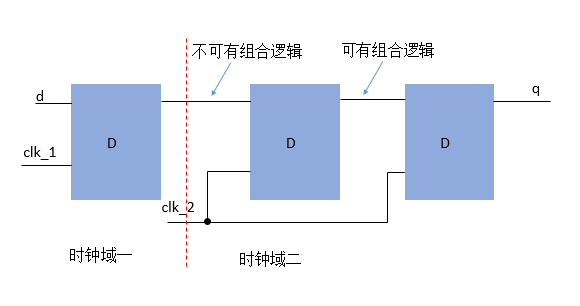

一般來說,信號(hào)是在異步信號(hào),跨時(shí)鐘域,復(fù)位電路中產(chǎn)生亞穩(wěn)態(tài)。

解決方式:

1.單比特信號(hào):

①采用同步器同步,低速設(shè)計(jì)打兩拍,高速設(shè)計(jì)可能需要打三拍。

低速到高速時(shí)鐘域,低速信號(hào)一般能被高速時(shí)鐘域采到甚至多次。但高速時(shí)鐘域到低速時(shí)鐘域就不太好辦了:

②閉環(huán)解決方案:采用握手反饋信號(hào),這會(huì)導(dǎo)致延時(shí)開銷大。

③開環(huán)解決方案:把信號(hào)展寬,至少為采樣T的1.5倍。這樣至少能采到一次。

2.多比特信號(hào):

傳遞多比特信號(hào),普通同步器就沒啥卵用了,因?yàn)槎啾忍匦盘?hào)偶發(fā)數(shù)據(jù)變化歪斜,導(dǎo)致采到的不一定是正確數(shù)據(jù)。

①多比特信號(hào)融合:把多比特信號(hào)轉(zhuǎn)換為單比特信號(hào),再用同步器同步。

②多周期路徑規(guī)劃:數(shù)據(jù)不需要同步,至需要同時(shí)傳遞一個(gè)同步的使能信號(hào)到接收時(shí)鐘域即可,使能信號(hào)沒被同步到接收時(shí)鐘域并被識(shí)別之前數(shù)據(jù)不被采集。即在信號(hào)某個(gè)沿產(chǎn)生同步脈沖指示信號(hào)。

③異步fifo。

6.競(jìng)爭(zhēng)冒險(xiǎn)是什么,怎么解決競(jìng)爭(zhēng)冒險(xiǎn)?

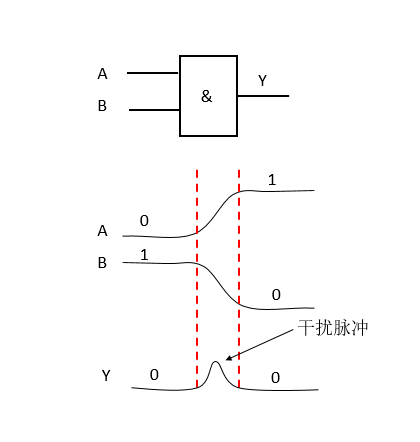

在組合電路中,當(dāng)輸入信號(hào)改變狀態(tài)時(shí),輸出端可能出現(xiàn)虛假信號(hào)(過渡干擾脈沖),這對(duì)電路來說是不利的。

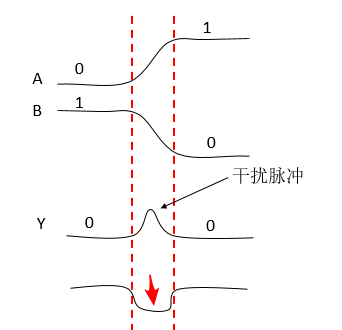

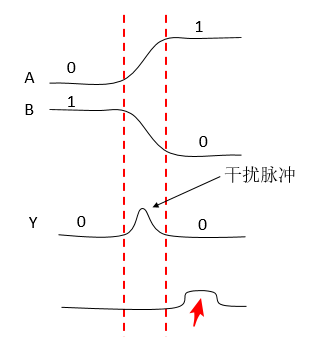

在數(shù)字電路中,任何一個(gè)門電路只要有兩個(gè)輸入信號(hào)同時(shí)向相反方向變化(由01變成10,或者相反),其輸出端就可能產(chǎn)生干擾脈沖。

信號(hào)由于經(jīng)由不同路徑傳輸達(dá)到某一匯合點(diǎn)的時(shí)間有先有后的現(xiàn)象,就稱之為競(jìng)爭(zhēng),英文名Race;由于競(jìng)爭(zhēng)現(xiàn)象所引起的電路輸出發(fā)生瞬間錯(cuò)誤的現(xiàn)象,就稱之為冒險(xiǎn),英文名Hazard或者Risk。

有競(jìng)爭(zhēng)不一定有冒險(xiǎn),但出現(xiàn)了冒險(xiǎn)就一定存在競(jìng)爭(zhēng)。

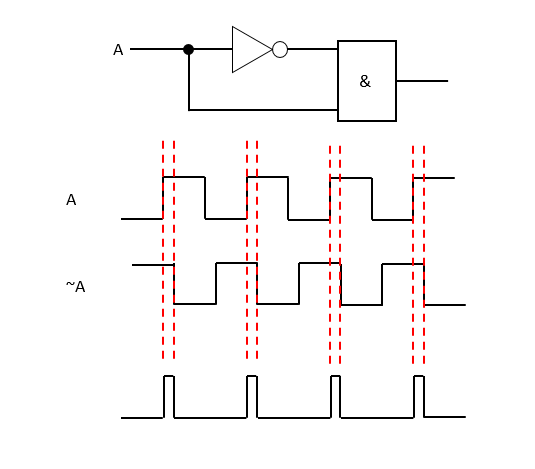

如下圖的簡單電路,由于門電路的延時(shí),A非相對(duì)于A信號(hào)會(huì)滯后一丟丟(時(shí)間由工藝決定),這就會(huì)導(dǎo)致輸出產(chǎn)生一個(gè)干擾脈沖。

更現(xiàn)實(shí)一點(diǎn),對(duì)于一個(gè)與門:

解決方式:

1.引入封鎖脈沖:引入負(fù)脈沖,在輸入信號(hào)發(fā)生競(jìng)爭(zhēng)的時(shí)間內(nèi),把可能產(chǎn)生的干擾脈沖的門鎖住。

封鎖脈沖的寬度不應(yīng)小于過渡時(shí)間且與輸出信號(hào)轉(zhuǎn)換同步。

缺點(diǎn):脈沖寬度和產(chǎn)生時(shí)間有嚴(yán)格要求。

2.引入選通脈沖:在電路狀態(tài)穩(wěn)定后,再選通輸出。

缺點(diǎn):脈沖寬度和產(chǎn)生時(shí)間有嚴(yán)格要求。

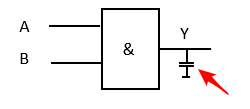

3.引入濾波電容:輸出端并接一個(gè)不大的濾波電容

缺點(diǎn):輸出波形邊沿變壞。

4.修改邏輯設(shè)計(jì),增加冗余項(xiàng):

對(duì)于給定的邏輯 Y=AB+?C,當(dāng)BC都為1的時(shí)候,若A值改變,則會(huì)發(fā)生競(jìng)爭(zhēng)。所以可以添加冗余項(xiàng):

Y=AB+?C+BC

分析有無競(jìng)爭(zhēng)冒險(xiǎn):畫出函數(shù)的卡諾圖,檢查有無幾何相鄰的邏輯項(xiàng),有則可能產(chǎn)生競(jìng)爭(zhēng)冒險(xiǎn)。

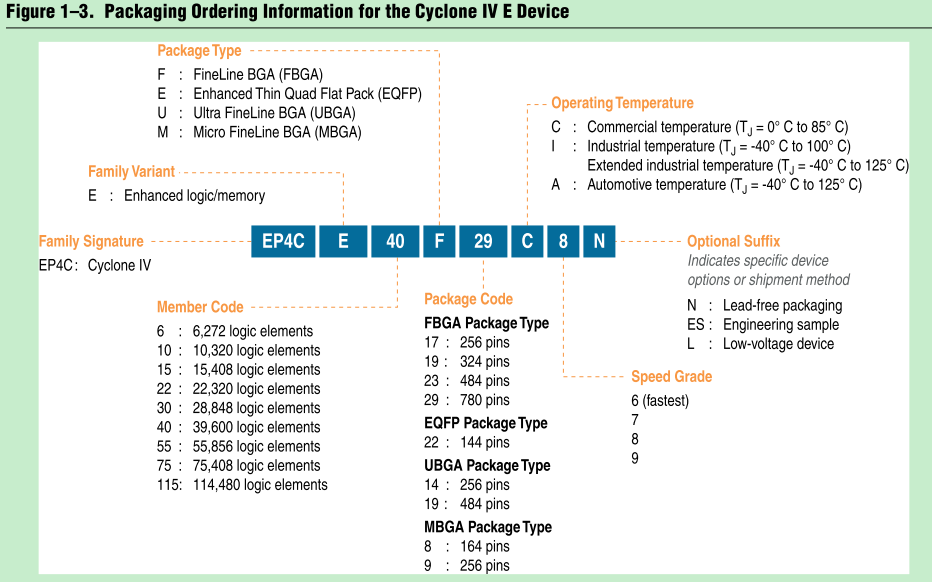

7.你使用的器件名稱含義?

-

FPGA

+關(guān)注

關(guān)注

1638文章

21856瀏覽量

609664 -

集成電路

+關(guān)注

關(guān)注

5409文章

11764瀏覽量

365284 -

Verilog

+關(guān)注

關(guān)注

28文章

1360瀏覽量

111084 -

觸發(fā)器

+關(guān)注

關(guān)注

14文章

2027瀏覽量

61596 -

可編程邏輯器件

+關(guān)注

關(guān)注

5文章

145瀏覽量

30455

原文標(biāo)題:FPGA基礎(chǔ)

文章出處:【微信號(hào):gh_9d70b445f494,微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

Xilinx FPGA學(xué)習(xí)筆記

FPGA學(xué)習(xí)筆記-入門

FPGA學(xué)習(xí)筆記-關(guān)于FPGA資源

FPGA學(xué)習(xí)筆記-電源電壓

FPGA的學(xué)習(xí)筆記---FPGA的開發(fā)流程

FPGA學(xué)習(xí)筆記---基本語法

FPGA基礎(chǔ)學(xué)習(xí)筆記--組合邏輯電路-編碼器和譯碼器

FPGA基礎(chǔ)學(xué)習(xí)筆記--組合邏輯電路-算術(shù)運(yùn)算電路

《高級(jí)FPGA設(shè)計(jì)》學(xué)習(xí)筆記:復(fù)位方案

C.P FPGA學(xué)習(xí)筆記

FPGA學(xué)習(xí)筆記匯總(7.13更新)

INTEL FPGA學(xué)習(xí)筆記

FPGA學(xué)習(xí)筆記:ROM IP核的使用方法

評(píng)論